# Quasi Two-Level Operation of Modular Multilevel Converter for Use in a High-Power DC Transformer with DC Fault Isolation capability

I. A. Gowaid, G. P. Adam, A. M. Massoud, *Senior Member, IEEE*, S. Ahmed, *Senior Member, IEEE*D. Holliday, and B. W. Williams

Abstract—DC fault protection is one challenge impeding the development of multi-terminal DC grids. The absence of manufacturing and operational standards has led to many pointto-point HVDC links built at different voltage levels, which creates another challenge. Therefore, the issues of voltage matching and DC fault isolation are undergoing extensive research and are addressed in this paper. A quasi two-level operating mode of the modular multilevel converter is proposed, where the converter generates a square wave with controllable dv/dt by employing the cell voltages to create transient intermediate voltage levels. Cell capacitance requirements diminish and the footprint of the converter is reduced. The common-mode DC component in the arm currents is not present in the proposed operating mode. The converter is proposed as the core of a DC to DC transformer where two converters operating in the proposed mode are coupled by an AC transformer for voltage matching and galvanic isolation. The proposed DC transformer is shown to be suitable for high-voltage high-power applications due to the low switching frequency, high efficiency, modularity, and reliability. The DC transformer facilitates DC voltage regulation and near instant isolation of DC faults within its protection zone. Analysis and simulations confirm these capabilities in a system-oriented approach.

*Index Terms*— Modular multilevel converter, dc transformer, dual active bridge, dc fault, and dc/dc power conversion.

### I. INTRODUCTION

HE increasing penetration of renewable energy into power grids, along with ambitious carbon reduction targets, is the main driving force towards new energy trade and security regulations worldwide. In this regard, high voltage DC grids are viewed as a key element in building

I.A. Gowaid is with the Department of Electronic and Electrical Engineering, University of Strathclyde, G1 1XW Glasgow, U.K., and also with the Electrical Engineering Department, Faculty of Engineering, Alexandria University, Alexandria 21544, Egypt (e-mail: i.azmy.gowaid@strath.ac.uk)

G.P. Adam, D. Holliday and B.W. Williams are with the Department of Electronic and Electrical Engineering, University of Strathclyde, G1 1XW Glasgow, U.K. (e-mail: <a href="mailto:grain.adam@eee.strath.ac.uk">grain.adam@eee.strath.ac.uk</a>, <a href="mailto:derrick.holliday@strath.ac.uk">derrick.holliday@strath.ac.uk</a>, <a href="mailto:bww.williams@eee.strath.ac.uk">b.w.williams@eee.strath.ac.uk</a>)

A. M. Massoud is with the Department of Electrical Engineering, Qatar University, Doha, Qatar (e-mail: <a href="mailto:ahmed.massoud@qu.edu.qa">ahmed.massoud@qu.edu.qa</a>).

S. Ahmed is with Texas A&M University at Qatar, Doha, Qatar (e-mail:<a href="mail:shehab.ahmed@qatar.tamu.edu">shehab.ahmed@qatar.tamu.edu</a>).

anticipated high capacity transmission systems. However, realization of such DC systems is surrounded by challenges ranging from the- need for a new business model to major technical obstacles and lack of operational experience. Nevertheless, the concept continues to gain momentum across the industry.

Voltage-source converter (VSC) based DC transmission systems offer an essential feature; power reversal is realized without reversing the DC voltage polarity. A feature conventional current-source converter based DC transmission systems lack. Therefore, the VSC multi-terminal DC (MTDC) grid is the core of academia and industry interests when looking beyond point-to-point connections.

Analogous to an AC system, a reliable DC grid must feature defined protection zones with high selectivity where all types of faults are rapidly isolated without affecting the rest of the system. Isolating and clearing DC faults is a showstopper for DC networks. A DC circuit breaker is required to interrupt high fault currents in the absence of zero current crossings [1]. The low impedance of a DC circuit leads to a steep rise in fault current where protection of power electronics necessitates interruption times in the order of a few milliseconds. Conventional mechanical circuit breakers are slow and suited to ac type faults [1-3]. Solid-state DC circuit breakers can achieve fast interruption times but at high capital cost and on-state operational losses [4]. A hybrid DC circuit breaker (CB) has been proposed where a mechanical path serves as a main conduction path with minimal losses during normal operation, and a parallel connected solid-state breaker is used for dc fault isolation [4, 5]. However, capital cost remains high, and it has relatively large footprint. The mechanical opening time is a few milliseconds at 70kV and is expected to increase because of the increased time needed to bridge the wider contact gap necessary for higher voltage ratings. The semiconductors conduct and commutate high fault currents arising during the mechanical CB opening time. Furthermore, for reliable grid-wide protection, proper and fast coordination between individual DC circuit breakers in different sections of the grid must be administered to achieve fast interruption times[1], less than the dc link time constant of very few milliseconds (depending whether the link is cable or overhead).

Voltage regulation and optimized power flows through network lines are mandatory for proper and efficient operation of a DC grid. Dual to frequency in an AC network, a stable DC voltage level is the indicator to power balance along the DC system. Several techniques have been devised for DC line voltage control as reported in [6-11]. However, most of these techniques are not suitable for generic DC grids, with large numbers of converters and busses. Furthermore, additional power flow controllers, similar to phase shifters in an AC system, may be needed to support system voltage stability [12].

A real DC super-grid with multiple in-feed points, tapping points, and various terminals connected to different AC grids makes the voltage regulation issue more complex. Forming and solving an optimal DC load flow problem may be a practical solution to calculate terminal voltage set points. Information and commands throughout the network can be exchanged between individual DC busses and a control center, which determines optimal load flow scenarios similar to AC systems [13]. In general, any attempt to address voltage regulation in a real DC super-grid cannot disregard that it is not possible to build a vast grid without voltage stepping and matching. Unlike an AC transformer, so called 'DC transformer' will be based on active controlled power electronic components where DC voltage control and/or power flow control can be readily augmented. Having grid components dispersed through the DC network actively contributing to voltage regulation, power flow control and rapid fault protection, in addition to terminal ports, will significantly boost network controllability and security.

While organizations such as CIGRE, IEEE, and IEC are developing guidelines and standards for common HVDC manufacturing and operation practices, more point-to-point links are planned and commissioned in the absence of common standards [4]. The result is more point-to-point connections at different voltage levels (e.g. ±80kV, ±150kV and ±320kV) and different topology concepts [4]. Therefore, apart from any efficiency considerations, high power DC transformers appear the only way to interconnect and retrofit existing point-to-point links. If DC transformers built with active components are present at vital nodes throughout a potential DC grid, an augmented fault protection function will constitute a milestone towards a super-grid.

A multitude of DC-DC converter designs for low and medium voltage and power ranges are in operation across industry and power systems. High switching losses render traditional high-frequency hard-switched converters unsuitable for bulk power applications. Soft switched converters offer low switching losses [14]; hence may be more applicable for heavy power transfer. Such a low-loss characteristic is achieved using a resonant stage allowing zero-voltage switching or zero-current switching. The switching frequencies of both transformer and transformerless designs [15-25] are selected in the range of kilohertz or even tens of kilohertz in an attempt to reduce the size of the transformer and passive resonant components. However, these designs aim at medium voltage (a few kilovolts) and medium power (a few megawatts) applications such as, wind generation, DC distribution and transportation. Apparently, a DC grid requires DC transformers capable of handling hundreds or even thousands of megawatts, at hundreds of kilovolts.

Scaled up versions of the designs discussed in [15-26] are not compatible as the basis of an ultra-high voltage ultra-high power DC transformer. The reasons range between unidirectional operation, extremely high voltage stresses on passive components of resonant designs, destructive voltage derivatives acting upon converter transformer stage, and the high frequency operation. A 25MW HVDC tap was proposed in [27, 28], which is a unidirectional design to tap power to loads and not a solution for line interconnection with large power exchange.

An interesting DC converter topology, claimed appropriate as a DC transformer for MTDC grids, is analyzed in [1, 29-33]. The topology is transformerless, thyristor-based featuring a "rotating" capacitor resonating with inductors to achieve high voltage stepping ratios. However, the peak capacitor voltage in normal operation exceeds that of the high DC voltage side. Being exposed to such high voltage stresses, switching device arrays in both the primary and secondary sides must be rated at higher than the high-side DC voltage. Furthermore, the proposed topology lacks isolation and defined ground separation between the low and high voltage circuits, which is not reliable considering the critical role of the DC transformer in bulk power transfer.

Conceptually, dual active bridge (DAB) DC-DC converter configurations may have potential as high power DC transformers [34-40]. They employ an AC transformer to perform voltage stepping. Three-phase topologies enjoy low ripple currents in addition to simple phase angle control and an inherent soft switching nature. The problem of transformer phase current unbalance, due to asymmetric leakage inductances, is addressed in [25, 34] through fast controllers. However, square-wave operation of the DAB converters is a fundamental drawback at high voltage. This impedes their scalability since the very steep rising and falling edges of square wave voltages apply destructive dv/dt stresses on transformer insulation. Moreover, the adopted ranges of switching frequency are not applicable in applications with gigawatt-level power transfer.

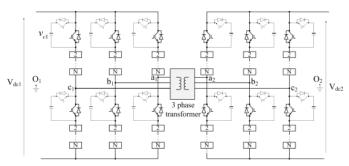

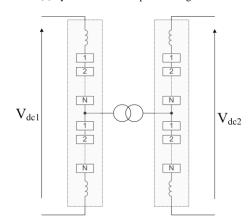

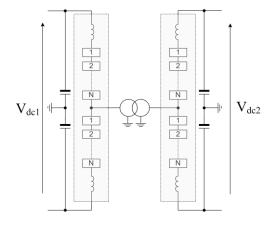

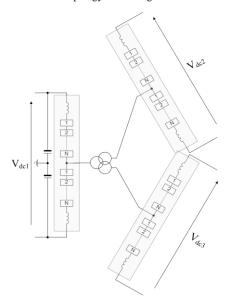

Taking into account the features of existing technology, and the trend towards modular designs, this paper proposes a DC transformer based on modular multi-level converters (MMC). Two three-phase MMCs are connected through an AC transformer as in Fig. 1; a high voltage converter and a medium voltage converter. Both MMCs employ half-bridge cells. Due to the proposed operating mode, the converters offer a considerable reduction in footprint, cost and weight. Power flow control or DC voltage regulation is administered by phase shift and voltage magnitude control. Both modular converters operate in a quasi-two-level (Q2L) mode in order to alleviate voltage derivative dv/dt stress on the AC transformer stage, thereby rendering the proposed DC transformer topology viable at ultra-high voltage levels. The trapezoidal voltage waveform, with controllable slopes, is created by sequential switching of the cells as in a conventional MMC operating with sinusoidal reference in a staircase mode.

Fig.1: Modular multilevel converter based DC transformer for high-voltage high-power applications.

In the proposed operating mode, each cell capacitor is utilized as an energy tank (switch voltage clamp) to generate intermediate voltage levels for a few microseconds during transitions between  $\frac{1}{2}V_{dc}$  and  $-\frac{1}{2}V_{dc}$ , allowing cell capacitances to be drastically reduced. This considerably reduces the footprint and cost of each Q2L converter. In Q2L mode, the arms currents of the converter do not contain a common-mode DC component, unlike conventional MMC operation, therefore semiconductor losses are reduced. When a DC fault occurs, the proposed Q2L DC transformer (specifically the non-fault-side converter) rapidly isolates the faulted line such that the rest of the DC grid remains functional. Furthermore, galvanic isolation stops fault propagation between DC transformer sides, even when a fault occurs in one of the DC transformer converters. Modified design of conventional AC power transformer core reduces iron losses allowing switching frequency in the range of a few hundred Hz where a number of low-order harmonics engage in power transfer.

The paper investigates the role of the proposed DC transformer in addressing some of the technical challenges related to proper operation of generic DC grids with multiple DC voltage levels, including DC fault ride-through. The discussion includes aspects related to losses, cost, and additional functionality.

## II. BRIEF REVIEW OF CONVENTIONAL OPERATION OF MODULAR MULTILEVEL CONVERTER

Conventionally, established modulation techniques operate the modular multilevel converter such that the upper and lower arms of the same phase-leg conduct simultaneously, and this constitutes the sum of the cell capacitor voltages in conduction path of both arms must be equal to the total DC link voltage minus the AC voltage drop in the arm inductances[41-44]. This necessitates the voltages developed across the cell capacitors of the upper and lower arms to be complementary, which can be approximated by

$$v_{x1} = \frac{1}{2}V_{dc}(1 - m\sin(\omega t + \varphi_x))$$

$$v_{x2} = \frac{1}{2}V_{dc}(1 + m\sin(\omega t + \varphi_x))$$

(1)

where  $V_{dc}$  is the converter input DC link voltage, m is modulation index, and  $\varphi_x = \{0, \frac{4}{3}\pi, \frac{2}{3}\pi\}$  for three phases a, b and c respectively. With such simultaneous operation of the

upper and lower arms, the arm currents of each phase-leg contain AC and DC components. The AC component of the arm current comprises the fundamental current that is associated with active power exchange between the converter and the AC side, and a number of low-order harmonics (predominantly 2<sup>nd</sup> harmonic) that are caused by cell capacitor voltage fluctuations in attempt to counter the ac voltage drop in the arm inductances. The DC component of the arm current is associated with the power exchange between the converter and the DC side. In steady-state, the converter power exchange with the AC side equals the power exchanged with the DC side. Under such a condition, the converter cell capacitors exchange zero net active power with the AC side over one or several fundamental periods; hence the cell capacitor voltages are maintained around the desired set point  $V_{dc}/N$ , where N is the number of cells per arm. Normally, the modular converter cell capacitors are rotated based on arm currents polarities, to ensure capacitor voltage balancing. The presence of the common-mode DC component in the arm currents represents a major concern as it increases converter semiconductor losses [45-55].

Also, the AC fundamental current flow through the cell capacitors increases their energy storage requirements; thus relatively large cell capacitances are needed [42]. The device issues influence modular converter viability from theperspective of efficiency and footprint. Additionally, the half-bridge modular converter does not inherent the ability to block current in-feed from the grid during a pole-to-pole DC fault, which necessitates increased sizing of arm inductances (together with interfacing transformer leakage inductance) to effectively limit the DC fault current. This further influences the cell capacitor size needed to limit the capacitor voltage ripple within the 10% range necessary to avoid a negative impact on the control system cross-modulation.

# III. QUASI TWO-LEVEL OPERATION OF A MODULAR MULTILEVEL CONVERTER

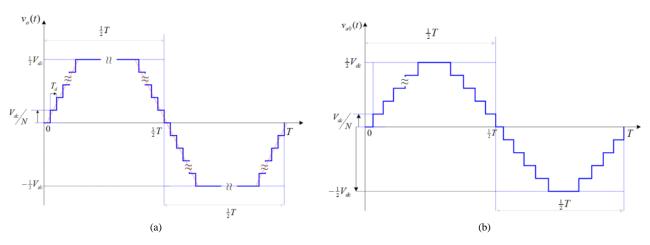

In this paper, each modular converter in the DC transformer of Fig. 1 is operated in Q2L mode where the cell capacitors of the MMC are used for short periods,  $T_d$ , only to facilitate orderly stepped transitions between voltage levels  $\pm \frac{1}{2}V_{dc}$  through intermediate cell voltage levels (see Fig. 2). The dwell time  $T_d$  spent at each intermediate cell voltage level is sufficiently small to reduce the energy storage requirement per cell capacitor for a given voltage ripple value, and must remain compatible with the switching ability of high-voltage insulated gate bipolar transistors. Also the value of  $T_d$  must be large enough to avoid unacceptable voltage derivative dv/dt levels and eliminate higher harmonics from the output voltage waveform. These harmonics, otherwise, bring about additional losses in the coupling transformer as they do not engage in power transfer.

In this manner, each phase in the Q2L modular converter of the DC transformer generates a step approximation of a trapezoidal AC voltage with pre-defined voltage steps equal to one cell capacitor voltage ( $V_{dc}/N$ ), with a total transition

time between  $\frac{1}{2}V_{dc}$  and  $-\frac{1}{2}V_{dc}$  of  $2(N-1)T_d$  per fundamental cycle, where N is the number of cells per arm. The dwell time at each cell voltage level is sufficiently small so that the time  $2(N-1)T_d$  is much smaller than the fundamental period T. During the non-transitional times, the AC poles of the Q2L converter will be directly connected to the DC rails. This means the MMCs of the DC transformer effectively operate similar to two-level converters. That is, current flows separately in each arm per leg for a period  $\frac{1}{2}T - (N-1)T_d$  of the fundamental half-cycle. Only during brief periods when the cell capacitors are successively switched, both upper and lower arms of the O2L converter simultaneously conduct currents to the AC input as in true multilevel operation of an MMC. Therefore, the proposed Q2L mode eliminates the common-mode DC component normally present in the arm currents of a conventional MMC. Consequently, lower semiconductor losses are expected. Furthermore, small cell capacitances are required for the quasi two-level mode, since they are only loaded for a small fraction of the fundamental cycle, where smaller arm inductances are sufficient to limit inrush currents associated with cell switching.

As in the conventional MMC, the inserted cell voltages in each phase leg must sum to the DC voltage minus the arm inductances voltage drop. Over one fundamental cycle starting at  $t=t_o$ , the voltage of one converter arm in the Q2L mode can be expressed as in (2).

The voltage of the other arm, in the same leg, is the complement. The arms of other legs in a three phase Q2L converter exhibit the same voltage waveform, phase-shifted accordingly. In (2),  $V_l$  is the voltage drop in both arm inductances, whereas  $V_{lc}$  is the inductance drop in the complementary arm. Proper Q2L mode operation can be achieved with minimal arm inductance, with circuit stray inductance being sufficient, as will be shown. Therefore, the inductance voltage drop in (2) can be neglected.

In the converter controllers, (2) can be realized by dividing the real-time value of a trapezoidal function of the fundamental frequency at slopes  $\pm V_{dc}/(N-1)T_d$  by the

voltage step  $V_{\rm dc}/N$  . Rounding the result to the closest integer brings about the number of active cells per arm.

In the proposed operating mode, the fundamental voltage output is

$$V_{m1} = \frac{2V_{dc}}{\pi} \frac{\sin \alpha}{\alpha} \tag{3}$$

where  $\alpha = \frac{1}{2}\omega(N-1)T_d$ , and  $\omega$  is the fundamental frequency in rad/s. This corresponds to a modulation index of

$$m_1 = \frac{V_{m1}}{\frac{1}{2}V_{dc}} = \frac{4}{\pi} \frac{\sin \alpha}{\alpha} \tag{4}$$

This expression shows that the trapezoidal voltage fundamental of the modular converter, present to interfacing AC transformer when operated in Q2L mode, tends to that of the square waveform, provided  $\alpha \rightarrow 0$ .

$$m_1 = \frac{4}{\pi} \cdot \lim_{\alpha \to 0} \frac{\sin \alpha}{\alpha} \approx \frac{4}{\pi}$$

(5)

Additionally, most of the dominant low-order harmonics such as the 3<sup>rd</sup>, 5<sup>th</sup>, and 7<sup>th</sup> can contribute to the power transfer, as will be presented.

Although the dwell time is assumed constant for each transition step between  $\pm \frac{1}{2}V_{dc}$ , it can be varied so as to minimize the higher order harmonics (e.g.  $17^{th}$ ,  $19^{th}$ , etc.) which contribute little to power transfer but are increasingly likely to be absorbed as losses in the bandwidth limited transformer iron core.

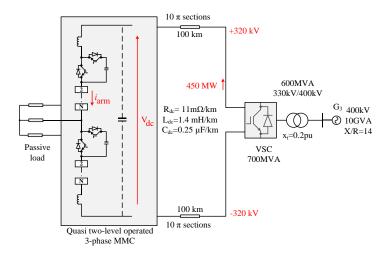

Different operational aspects and parameters of the proposed Q2L mode are illustrated using Matlab/Simulink® to simulate a basic test case where an open-looped Q2L converter feeding a resistive load of 450MW (0.99 lagging pf) is connected to an AC grid via an HVDC link of  $\pm 320$ kV.

$$V_{arm} = \begin{cases} \sum_{i=0,1...N-1} \frac{V_{dc} - V_{l}}{N} [u(t - iT_{d} - \frac{k}{f_{s}})], & \frac{k}{f_{s}} \leq t < \frac{k}{f_{s}} + (N - 1)T_{d} \\ V_{dc} - V_{lc}, & \frac{k}{f_{s}} + (N - 1)T_{d} \leq t < \frac{k}{f_{s}} + \frac{1}{2}T \\ V_{dc} - V_{lc} - \sum_{i=0,1...N-1} \frac{V_{dc} - V_{l}}{N} [u(t - [\frac{1}{2}T + iT_{d} + \frac{k}{f_{s}})], & \frac{k}{f_{s}} + \frac{1}{2}T \leq t < \frac{k}{f_{s}} + \frac{1}{2}T + (N - 1)T_{d} \\ 0, & \frac{k}{f_{s}} + \frac{1}{2}T + (N - 1)T_{d} \leq t < \frac{k}{f_{s}} + T \end{cases}$$

$$where \quad t_{o} = \frac{k}{f_{s}}, \quad k = 0, 1, 2, ...., \infty$$

(2)

Fig. 2: phase output voltage measured relative to virtual dc link mid-point for (a) Quasi two-level mode, and (b) Conventional mode.

Fig. 3: The test system for the proposed quasi two-level modular converter.

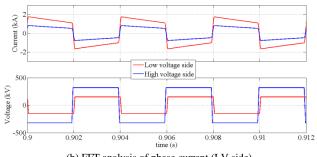

Control of the AC grid-side converter is presented in section VII. For expedience, the converter comprises 10 cells per arm. A dwell time of  $T_d = 5 \mu s$  gives a 45 $\mu s$  transition time between the two main voltage levels ( $\frac{1}{2}V_{dc}$  and  $-\frac{1}{2}V_{dc}$ ), which is 1/90 of the fundamental cycle at 250Hz. The test system parameters are depicted in Fig. 3.

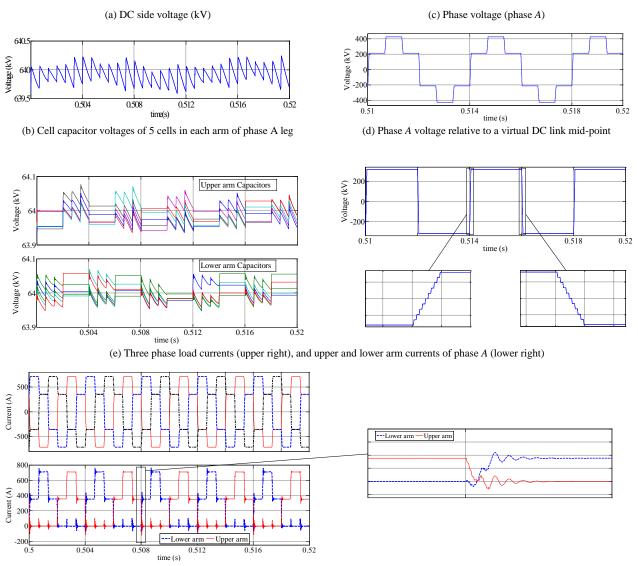

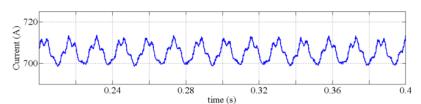

Various current and voltage waveforms are shown in Fig. 4. Subplot 4c depicts the load phase voltage peaking at  $\frac{2}{3}$  the DC link voltage while subplot 4d shows the phase voltage to the virtual DC link midpoint, peaking at half the DC link voltage. The gradual transition between the two voltage levels  $\pm 320 \text{kV}$ is realized in 10 steps, where cell capacitor voltages remain balanced with less than 0.3% peak-to-peak ripple around 64kV (Fig. 4b). This low ripple is achieved with cell capacitors as small as 50µF (64kV assumed per cell to simplify detailed models), which is significantly smaller than the corresponding cell capacitance for conventional MMC operation at comparable voltage and power levels. Such a low voltage ripple indicates that the cell capacitance can be further reduced to give ±10% ripple, which is a widely accepted figure for conventional MMCs. For the operating conditions in Fig. 3, cell capacitance of only 1µF achieves ±6% voltage ripple. However, with smaller cell capacitance, the DC current ripple increases.

Generally, cell capacitor sizing depends on voltage and power levels as well as the number of cells per arm; that is, it is application-specific. As a compromise,  $50\mu F$  cell capacitance is selected for the systems analyzed in this paper. A higher number of cells per arm and/or faster transition between intermediate voltage levels further reduces the cell capacitance requirement as each capacitor supports the voltage for a shorter period. However, this may be impeded by practical limitations.

For expedient comparison with the conventional MMC, the cell energy requirement in kJ/MVA is compared for the proposed Q2L converter with that of the 401-level MMC,  $\pm 320 \text{kV}$ , 1059MVA application in [52]. Therein it was concluded that a 10mF cell capacitor is needed to achieve 30kJ/MVA, which is the energy level typically required for conventional MMC operation within  $\pm 10\%$  cell voltage ripple [53]. This figure is calculated from

$$E_{cell} = \frac{3CV_{dc}^2}{NS} \tag{6}$$

where  $E_{cell}$  is cell energy in kJ/MVA, S is the total power in MVA, and  $V_{dc}$  is the pole-to-pole DC voltage in kV. If the

same MMC converter is operated in the Q2L mode with a  $50\mu F$  capacitor per cell, the energy requirement, according to (6), drops to 0.145kJ/MVA (with voltage ripple below 1%) which is less than 0.5% of the energy requirement for the conventional MMC. This confirms a drastic reduction in cell volume when operated in the Q2L mode.

The cell voltages are balanced with the same principles used in the conventional MMC [56]. During phase voltage transition, cell capacitors per arm are switched into or out of the circuit conduction path in an order dictated by their individual voltage magnitudes and arm current directions. This ensures the capacitors are rotated with their voltages remaining within an allowable voltage ripple band.

The voltage ripple is further reduced since, when switched in the circuit, cell capacitors have ideally no current flow, excluding the brief voltage transition periods between  $+\frac{1}{2}V_{dc}$  and  $-\frac{1}{2}V_{dc}$ . This implies that the load current always flows in the arm which has its cells in the off state, as long as the respective AC pole is at one of its two main voltage levels (note the positive arm current direction in Fig. 3).

During an AC pole transition, output phase current is shared between the upper and lower arms as cell capacitors of both arms switch in complementary pattern. At the same time, the difference between the DC side voltage and the sum of cell voltages in each leg, results in limited inrush current acting to establish voltage balance. The net result is a limited common-mode current whenever the load current commutates between the upper and lower arms of each phase leg, as observed in Fig 4e. This is why the aggregate voltage drop on both the upper and lower arm inductances was considered during voltage transition periods in (2). As in conventional MMC operation, this common-mode circulating current neither diverts to output AC phase current nor reflects in the AC voltage waveforms. This transient is mitigated by arm inductances.

For the considered case study,  $5\mu H$  inductance per arm was found to acceptably mitigate the common-mode current (Fig 4e). In an actual system, this would be the stray inductance of the circuit. Higher arm inductance values produced longer current oscillations due to the small cell capacitances. In-depth study and mathematical quantification of this issue may need to be considered in a separate device-oriented context.

A DC voltage ripple at the Q2L converter terminals, at triple the fundamental frequency, can be observed in Fig.4a. In each leg, all cell capacitors in the conduction path, having to sum up to DC side voltage, experience similar ripple. This triggers additional common mode arm currents twice per half cycle, as seen in Fig. 4e. This DC side voltage ripple is the result of DC current ripple.

Unlike two level square wave operation where DC current is almost ripple-free in steady-state, the introduced intermediary voltage levels in Q2L operation produce brief DC current dips of significant magnitude whenever current commutates between the arms of any phase leg (6 times per fundamental cycle). In practice, the application of the Q2L modular converter in a DC transformer involves long DC cables. The distributed capacitance and inductance of a DC cable inherently bypasses and damps the DC current ripple

along cable length. Fig. 5 indicates that only 2% current ripple (15A peak-to-peak) is seen at the grid-side end of the 100 km HVDC line, with each DC cable modeled as 10 consecutive  $\pi$  sections. At the Q2L converter end, the first few kilometers of each DC cable are modeled as inductance in series with a resistor to account for their negligible equivalent capacitance as seen by the Q2L converter. When a DC filter (500  $\mu$ F capacitor) is installed across the DC rails of the Q2L converter in the example of Fig. 3, the triple load frequency cell voltage ripple and arm inrush currents are mitigated. The larger the filter capacitor, the smaller the DC voltage and current ripples at the Q2L converter terminals. With a perfectly stiff DC source, these would be totally eliminated.

Despite being fairly a short line, the distributed parameters of the 100 km HVDC cables are clearly sufficient to assure satisfactory operating conditions for both load and grid, without any discrete DC filters. Longer HVDC cables will further alleviate DC voltage and current ripples. However, in applications where the Q2L converter is connected directly to a non-stiff DC source, or connected to low-capacitance DC line (e.g. overhead HVDC lines), discrete DC link filter and/or increased size of cell capacitance may be needed.

The presence of a load current commutation transient in phase arms, in principle, may affect the soft-switching characteristics of some cells. However, the potential impact of common-mode arm currents on switching losses is expected to be outweighed by the alleviated conduction losses due to the higher fundamental output voltage, as described in (3) - (5), as well as the absence of the common-mode DC component and additional harmonics in arm currents.

The calculation method presented in [57] is used to quantify the conduction loss of the Q2L converter relative to a conventional MMC. It was presented in [57] that the conduction loss of a three phase 17-level MMC with 20 kV DC voltage supplying an 11 kV load at 0.8 lagging power factor has around 0.85% (170.8 kW) conduction losses. For a three phase 16 cell-per-arm Q2L converter with 20 kV DC supply and with the AC power output of the 50 Hz fundamental voltages and currents being 20 MVA at 0.8 lagging power factor, the losses are 0.51% (102.05 kW). The same 3.3kV IGBT module was used for both cases, with parameters given in [57].

## IV. OPERATION AND CONTROL OF THE PROPOSED DC TRANSFORMER

#### A) Operation and topologies:

The back-to-back connection of two Q2L converters through a coupling AC transformer creates a type of dual active bridge (DAB) topology, which is recognized as a potential arrangement for high power applications. The coupling transformer is responsible for voltage matching. Unlike other DAB proposals, a high frequency coupling transformer is not considered. As pointed earlier, the switching speed of state-of-the-art power electronic devices, at ultra-high voltage and power transfer levels, is not expected to exceed a few hundred Hz, mainly due to switching losses

Fig. 4: Voltages and currents of the quasi two-level modular converter in Fig. 3.

Fig. 5: DC current at the grid side converter in the example of Fig. 3.

and gating characteristics (long delay times). An operating frequency in the range of 250Hz to 400Hz is considered for the proposed transformer. Selection of a fundamental frequency which is higher than the power frequency (50/60Hz) may facilitate AC transformer design that can operate at ultra-high voltage/power levels where parasitic component-related phenomena are to some extent mitigated.

With an appropriate coupling transformer design, the proposed Q2L converter-based DC transformer may allow power transfer at fundamental frequency plus some of the higher harmonic frequencies. Today, such AC transformer

design is technically feasible, and achievable with limited modifications to core design of the conventional 50/60Hz AC power transformers. Power transfer at frequencies up to 2000 Hz implies that the 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> harmonics of a 250Hz fundamental voltage waveform engage in power transfer rather than inducing large iron losses in the core. This is a necessary step forward for a high efficiency DC transformer that may be comparable to AC power counterparts. Additionally, the claimed smaller size of a high-frequency transformer cannot be fully exploited because at applicable ultra-high voltages the physical clearance needed for mounting

Fig. 6: Plots for normal operation of the mono-polar DC transformer topology in Fig. 1 and Fig. 7a.

large transformer bushings is limiting, hence critical. Generally because of these high voltage creepage and clearance requirements, a transformer operating at a few multiples of the utility frequency is only expected to be slightly smaller than a conventional 50/60Hz AC power transformer. Thus there is no footprint gain in significantly increasing the operating frequency.

Consequently, the proposed DC transformer may have restricted potential as an offshore installation. This is traded for the galvanic isolation and high efficiency offered by the AC transformer at such a frequency range. Further assessment of the transformer design and characteristics is not within the scope of this text.

In the proposed DC transformer, the two Q2L converters act as voltage sources coupled through interface impedance. Conceptually, bidirectional power flow is possible. The direction and amount of power flow in this case is theoretically administered by controlling the phase angle between the developed voltage space vectors, as well as vector magnitudes. Traditionally, DAB assemblies control both power flow direction and amount mainly by the polarity and magnitude of the phase shift angle, respectively [38, 39]. This is due to their limited capability of controlling voltage magnitudes, especially three phase designs. Employing Q2L converters introduces the capability of controlling the fundamental voltage magnitudes due to the modular multilevel design. Moreover, selective harmonic elimination is a possibility. This brings about additional degrees of freedom for the proposed DC transformer to control power flow and provide voltage regulation. In this paper, only phase angle control is considered.

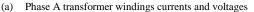

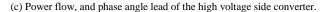

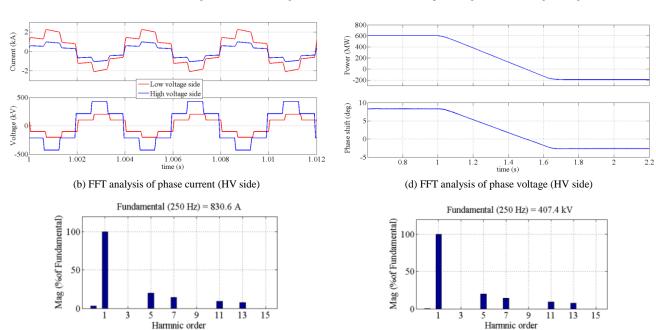

To investigate transformer operation, two three phase Q2L converters are connected to form the mono-polar arrangement in Fig. 1. The high voltage converter operates at  $\pm 320 kV$  DC

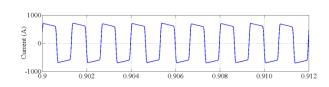

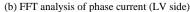

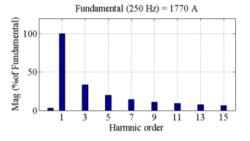

whereas the low voltage side operates at  $\pm 150$ kV. The coupling AC transformer is modeled as an ideal transformer, with the required turns ratio, in series with 10% impedance (700MVA base). At this stage, without any external control action, suitable phase angle values are commanded to alter power flow from 600 MW, injected into the ±150kV side, to around 190 MW in the reverse direction. Fig. 6 presents a view of transformer winding voltages and currents, as well as phase angle and power flow. As observed, a limited phase angle change is needed. When power flows into the  $\pm 150 \text{kV}$ side, winding voltages of the ±320kV side lead those of the ±150kV windings. FFT analyses of the phase voltage, line voltage and current (Figs. 6c and 6d) show that triplen harmonics are absent. Thus, in practice, power transfer will not involve the 3<sup>rd</sup> and 9<sup>th</sup> harmonic power even when transformer core design permits.

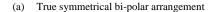

Low order triplen harmonics can be made to contribute to power transfer when the topology is modified as in Fig. 7b. For each transformer side, providing a closed path between the neutral point of the respective AC transformer windings and the DC-link midpoint lowers the phase voltage peak, hence current peak. Effectively, the developed path permits the flow of zero-sequence currents associated with triplen harmonics. The flow of triplen currents reshapes the resultant current waveform (Fig. 8). Particularly, the 3<sup>rd</sup> harmonic has one reverse-polarity peak exactly at the middle of the fundamental half cycle and two peaks of the same polarity as the fundamental half cycle, near its sides. Being of significant magnitude (around 1/3 the fundamental current magnitude), the 3rd harmonic flattens the phase current waveform at threefourth its former peak. Consequently, IGBTs of lower current rating could be utilized in the converter modules. However, the expense of current rating curtailment is the installation of high voltage split capacitors (a few microfarads each) between

#### (a) Symmetrical mono-polar arrangement

#### (b) Symmetrical configuration with both AC and DC sides grounded

Fig. 7: Possible mono-polar arrangements of the proposed bidirectional DC transformer.

#### Phase A transformer windings currents and voltages

#### (d) FFT analysis of phase voltage (LV side)

Fig. 8: Plots for steady-state operation of the mono-polar DC transformer topology of Fig. 7b (with split capacitors). [same simulation scenario as in Fig. 6]

the DC rails of each Q2L converter, where it has been shown in section III that discrete DC-link capacitors are not mandatory for DC transformer operation. This implies the sufficiency of a small discrete DC-side capacitance, just to provide the grounding point. The midpoint of the each DClink capacitor and respective transformer winding neutral point can be tied to ground or hard- wired.

The Q2L converter inherent capabilities of voltage magnitude manipulation and selective harmonic elimination enable its utilization in more complex DC transformer topologies, as for the 3-terminal transformer topology shown in Fig. 9a. It incorporates a 3 winding AC transformer and three Q2L inverters for the connection of three DC lines at different voltage levels. Power flow control in this topology can be achieved only through combined control of both voltage magnitudes (modulation indices)

displacements. When a fault occurs at any of the three lines, the dc transformer (in conjunction with ac circuit breakers) isolates it immediately but the power flow through the other unaffected long-term, although temporary interruption of power flow may be unavoidable. Fault protection capabilities of the proposed topologies are detailed in subsection IV.C. A symmetrical bi-polar arrangement is depicted in Fig. 9b.

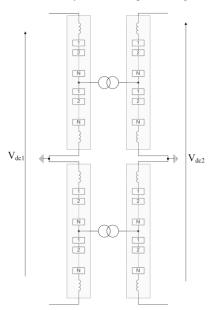

#### *B)* Steady-st ate control:

In remaining within main scope of the paper, the phase angle between the fundamental voltage space vectors of both converters is the only degree of freedom considered for transformer control (No voltage magnitude modulation has been incorporated at this stage).

(a) Three terminal topology connecting 3 different DC levels

Fig. 9: More complex configurations of the proposed DC transformer.

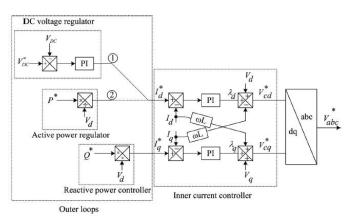

Bidirectional power flow control can be achieved by setting the voltage phase angle of one Q2L converter as the reference (i.e. zero angle) and control acts upon the phase angle of the other Q2L converter to control the power flow through the transformer. The former converter is denoted as the 'reference converter' and the latter the 'voltage/power control converter', depending on what parameter it controls. In a power control mode (Fig.10a), the power reference  $P_{dc}^*$  is compared to the measured power and the error signal is fed to a PI controller. The PI output is forwarded to a fast current controller which produces the required phase angle ( $\delta$ ) and voltage modulation index (m). Fast current control is important for a fine-tuned transient operation and to compensate for any asymmetry in transformer parameters. In this paper, the discrete transfer function of the fast current control block is set to C(z) = 1 and the modulation index is fixed to m=1. AC transformer asymmetry is neglected, and detailed control design including fast current and transient control transfer function C(z) is beyond the scope of this basic demonstration.

In the DC voltage control mode, the outer power control loop is replaced with a voltage control loop, as in Fig. 10b, where the DC voltage reference  $V_{dc}^*$  is produced by a droop controller or commanded by the operator (the output of a load flow scenario). In both control modes (the DC voltage or active power), reactive power required by the AC transformer is shared between both converters, depending on  $\delta$  and m.

#### C) Operation under DC line fault:

When a two-level or modular multilevel voltage source converter undergo a DC fault, the fault absorbs large current from the AC side once the DC voltage drops below the AC line voltage peak. Such uncontrolled rectifier action is unavoidable in a Q2L converter with half-bridge cells during a DC line fault. The proposed fault protection scheme utilizes the DC transformer configuration to deprive the fault-side

Q2L converter of energy input. That is, whenever one of the two Q2L converters senses current rise above a predefined threshold (e.g. 1.2 pu), all IGBTs of the other converter are immediately blocked (in the order of several microseconds for high power IGBTs). This truncates energy in-feed to the AC transformer. As the AC transformer leakage inductance has negligible stored energy, the fault loses its energy in-feed from the DC transformer line terminal. Effectively, the fault and the fault-side Q2L converter become isolated from the healthy line on the other side of the transformer. The galvanic isolation provided by the AC transformer prohibits fault propagation from one side to another even if one converter fails. Additionally, ac circuit breakers can be used at each side of the transformer, acting in a disconnector mode. If, at fault inception, the fault-side Q2L converter is not blocked, all cell capacitors will discharge into the fault. The small cell capacitors do not store a significant amount of energy, and their contribution to fault current will be insignificant. However, blocking the fault-side converter to retain its cell capacitor voltages serves for a smoother line restoration. With the topology of Fig. 7b, the split capacitor fault contribution is also insignificant due to its small size.

Once the fault is cleared, or isolated, Q2L converters can contribute to system restoration due to their black-start capability. DC transformer action depends on the pre-fault operating mode of the fault-side converter:

- Voltage control converter: The fault-side Q2L converter re-energizes the DC line where the DC voltage command ramps up from zero with an adequate slope to avoid transients and large inrush currents.

- Reference converter or power control converter: The line is first energized by the other terminal converter station; the DC transformer power command is ramped up (e.g. at a rate imposed by the grid operator).

Q2L

Converter

#### (a) Power flow control

Fig. 10: Generic control algorithm for the control converter of the proposed DC Transformer.

$i_{\rm ac}$

The converter control flexibility allows for additional maneuvering during post fault system restoration, if required. In the three terminal DC transformer topology (Fig. 9a), upon a fault in the DC side of one Q2L converter, the IGBTs of the other two converters (or all three converters) are blocked; stopping current flow into the fault. Immediately, the ac circuit breaker poles of the fault-side converter are opened and the other two converters instantly resume operation. The operational restart procedure depends on the opening time of the ac circuit breakers and the dc link time constant.

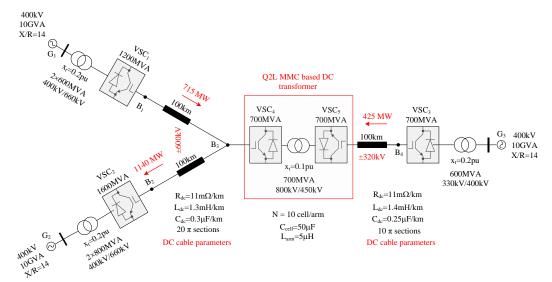

#### V. THREE TERMINAL DC TEST SYSTEM

Fig. 11 shows the test network used to assess the capabilities of the proposed high-power DC transformer under normal and transient conditions. In this three terminal illustrative network, a main high voltage DC line  $B_1$ - $B_2$  of  $\pm 600 kV$  is connected at point  $B_3$  to a  $\pm 320 kV$  DC line through the proposed DC transformer. Terminal grid side converter stations  $VSC_1$ ,  $VSC_2$  and  $VSC_3$  are modeled as half-bridge modular multilevel converters, with all their basic controllers incorporated (Fig. 12).

For the  $\pm 600 \text{kV}$  DC line, VSC<sub>2</sub> is configured to regulate the voltage at B<sub>2</sub>, while VSC<sub>1</sub> controls active power and AC voltage at busbar B<sub>1</sub>; therefore VSC<sub>2</sub> is rated at 1600 MVA, higher than VSC<sub>1</sub>. For the  $\pm 320 \text{kV}$  line, VSC<sub>3</sub> controls active power flow and AC voltage magnitude at B<sub>4</sub>, whereas DC voltage control is administered by the DC transformer control converter VSC<sub>5</sub>. The other Q2L converter VSC<sub>4</sub> is the reference converter. To ensure that the harmonic requirements are met at B<sub>1</sub>, B<sub>2</sub> and B<sub>4</sub>, converter terminals VSC<sub>1</sub>, VSC<sub>2</sub> and VSC<sub>3</sub> are operated in typical multilevel mode, with sinusoidal pulse width modulation (SPWM). Each Q2L converter in the DC transformer station has a  $20 \mu F$  split capacitor connected across the DC rails, hardwired to the respective transformer winding neutral point, which is grounded. System parameters are shown in Fig. 11.

#### VI. PERFORMANCE EVALUATION

#### A) Steady-state operation

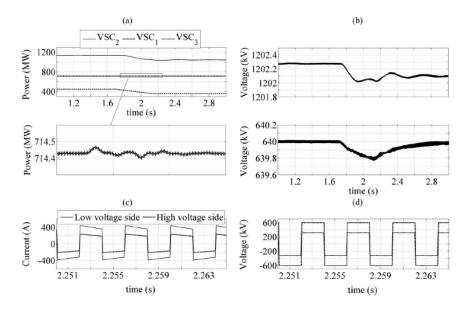

In the system described in section V, the simulation scenario is where power flows in the lines are 425 MW over line  $B_3$ - $B_4$ , 715MW over line  $B_1$ - $B_3$ , and 1140MW over line  $B_3$ - $B_2$ , with directions shown in Fig. 11. In steady-state, the simulated grid has stable line voltages and steady power flows between all busbars. At t = 1.7s, VSC $_3$  curtails the power injected to the grid at point  $B_4$  down to 355MW within 0.4s. Fig. 13 shows the DC grid response to the power reference change at VSC $_3$ . The DC voltage controllers quickly regulate the DC voltage at each line with brief 0.03% and 0.025% dips in the  $\pm 320$ kV and  $\pm 600$ kV DC voltages lines, respectively. The created power imbalance is taken up smoothly and the grid returns quickly to steady state operation at a new operating point. In Fig. 13b, both voltages are measured close to DC terminals of the DC transformer station.

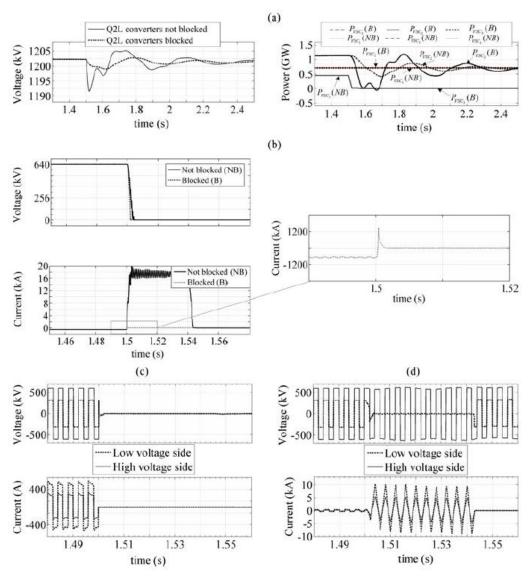

#### B) DC fault ride-through

A simulated fault scenario is when the test three-terminal DC grid of Fig. 11 encounters a pole-to-pole fault, at t=1.5s, in line  $B_3$ - $B_4$  at a distance of 3 km from the DC transformer station. Each grid side converter station is equipped with AC circuit breakers which are modeled to open the circuit at the first AC current zero crossing after the DC side current exceeds 120% of the station's DC current rating. The slow mechanical time constant of an AC circuit breaker is considered, with a 40ms delay in tripping action modeled for every AC circuit breaker. At 120% DC current, each grid side converter blocks its switches. Similarly, the DC transformer is equipped with an AC circuit breaker at the low voltage side of the AC coupling transformer, as well as an off-load isolation switch at each DC side, connected between the positive DC rail and the positive pole cable.

Data collected from two simulation runs are plotted in Fig. 14. In the first run, DC transformerQ2L converters continue operation under fault without blocking their IGBTs. In this case, the fault protection, as far as the DC transformer is concerned, is the sole responsibility of its 40ms-delayed AC circuit breaker (triggered at 120% of current rating). In the second simulation case, both Q2L converters of the DC transformer block their IGBTs 20µs after the 120% current barrier is reached.

In Fig. 14b, when the DC transformer converters are not blocked, the fault current leaps to 18kA in 4ms, as measured from the DC transformer end. Concurrently, line B<sub>3</sub>-B<sub>4</sub> voltage drops to zero within the same time span, as seen from DC transformer end. Both DC voltage and fault current encounter oscillations due to the distributed impedance of the line.

All cell capacitors of the control converter (fault-side converter) discharge their energy into the fault, as does the low voltage side DC-link split capacitor. At the other end of line  $B_3$ - $B_4$ , grid side converter station  $VSC_3$  encounters high fault currents both in the AC and DC sides. Although all IGBTs of  $VSC_3$  were immediately blocked, DC fault current

Fig. 11: Three terminal DC test system.

Fig. 12: Generic block diagram illustrating control systems of the grid side converter terminals (refer to [58-60]).

of 16kA freewheels in the cell diodes until its AC circuit breaker interrupts all AC phase currents in about 42ms. During this time the grid side converters at both ends of line  $B_1$ - $B_2$  do not encounter any high currents. The DC line voltage undergoes a shallow dip mainly due to the sudden interruption of power in-feed from line  $B_3$ - $B_4$ . The DC voltage regulator at VSC<sub>2</sub> rapidly restores the DC voltage, resulting in power oscillations at VSC<sub>2</sub> (Fig. 14a), whereas the power flow remains near steady at VSC<sub>1</sub>.

The reason that line  $B_1$ - $B_2$  is affected most by the power imbalance triggered by the fault, is the presence of the DC transformer. The reference converter, which is energized by the voltage of line  $B_1$ - $B_2$ , remains in operation despite the fault, applying Q2L voltage to the transformer windings. Being counteracted by zero voltage output from the control converter, the reference converter drives high currents in the windings of the AC transformer (Fig. 14d), which are rectified in the control converter to feed the fault. These currents are  $90^{\circ}$  phase shifted with respect to the reference converter output voltage, as observed in Fig.14d. This implies that the power fed to the fault by the DC transformer is purely reactive, which agrees with the fact that no active power can be fed to a line at zero-voltage (line  $B_3$ - $B_4$ ). Within 40ms, the

high currents in the DC transformer are interrupted by its AC circuit breaker and the DC fault current drops to zero.

In Fig. 14d, low-side winding phase voltage does not actually return to its pre-fault level when the AC circuit breaker trips, it is rather the voltage induced by current flowing in the high voltage windings. The net result is that the fault is confined within the downstream line (B<sub>3</sub>-B<sub>4</sub>) and the upstream line is only affected by the power imbalance and, to a lesser extent, by the circulating reactive power. However, without blocking Q2L converters the DC transformer is exposed to destructive currents. A current controller acting on the reference converter must be included to limits these currents; otherwise the second protection scenario, where all IGBTs are blocked, becomes the only practical fault protection scheme.

When IGBTS of the Q2L converters are blocked once the DC current reaches the 120% limit, energy supply is cut from the DC transformer line end. Hence, the fault current contribution from the transformer end drops immediately to zero and currents in both transformer sides diminish (Fig. 14c).

At the other end of the line, VSC<sub>3</sub> undergoes the same high currents like the previous case and is tripped out by its AC

Fig. 13: Performance of the test system in Fig. 11 with a 16% drop in the power flow through the ±320 kV line. (a) Power flows in the grid. (b) DC line voltages at dc transformer sides (pole-to-pole). (c) Steady-state dc transformer winding currents (phase A). (d) Steady-state dc transformer winding voltages (phase A).

circuit breaker. The power oscillations triggered in the system by the contingency are of lower magnitude and the system migrates relatively faster to the new power balance point (Fig 14a).

It is clear that when Q2L converters of the DC transformer are blocked, a smoother fault-ride through is achieved by the protected line (line  $B_1$ - $B_2$  in this case). Note that the DC transformer effectively impedes fault propagation from one side to another, but it has no role in protecting VSC<sub>3</sub>. Additional protecting devices are required for VSC<sub>3</sub> to ride-through the DC fault.

### VII. CONCLUSION

A quasi two-level (Q2L) operating mode has been proposed for modular multilevel converters, for utilization in a dualactive-bridge DC transformer topology. In this mode, a modular multilevel converter offers the following merits:

- Two level operation with controllable values of voltage derivative, dv/dt.

- Low cell capacitance requirement results in a considerable reduction in converter footprint.

- Lower losses due to higher fundamental output voltage and the absence of a DC common-mode component in converter arm currents. Soft switching is due the DC transformer topology.

- Beside flexibility of manufacturing and installation, the modular design results in additional output control capabilities; voltage magnitude (modulation index) and selective harmonic elimination.

The small cell capacitances of a Q2L converter are unable to filter out DC current ripple. Theoretically, a discrete DC-link capacitor may be needed to filter this ripple. Practically, the DC current ripple is naturally filtered out as the Q2L converter of a DC transformer is normally connected to DC

cables. It was shown that the distributed impedance of a 100km DC cable attenuates the DC current ripple to acceptable limits.

A DC transformer topology comprising two Q2L converters connected through a coupling AC transformer was shown to be promising for high power and high voltage applications. The topology offers galvanic isolation and voltage level matching. With a low operating frequency range (250-400Hz), efficient AC transformers with thinner core laminations could be utilized, with low order harmonics contributing to power transfer. Although the low frequency range (250-400Hz) reduces overall losses and size, the inevitable size of an ultrahigh voltage AC transformer may still limit the application of the proposed DC transformer to onshore locations.

In addition to voltage matching, the proposed DC transformer is controlled normally to provide DC voltage regulation or power flow control. More importantly, it offers near instant fault isolation within a certain protection zone. At DC fault inception at one side (e.g. the secondary circuit), the proposed DC transformer instantly interrupts the fault current contribution of the healthy line, connected at the other side, by blocking all power electronic switches in both converters. Alternatively, fault currents can be limited by the current controller of the non-fault-side converter. In either case, the DC fault is seen by the healthy line as an AC fault. When the fault is cleared, the DC transformer actively participates in smooth restoration of the healthy line.

In a generic DC grid with several power corridors and AC grid connection ports, multifunctional active components distributed around key points within the grid are necessary for protection, power flow control, DC voltage regulation, and voltage matching. Despite cost downsides, the presented DC transformer shows promise as such a component. Further detailed studies at both system and device levels are necessary for precise evaluation of the concept presented in this paper.

Fig. 14. System response to a fault in line  $B_3 - B_4$  at t = 1.5 s. [B: Q2L converters blocked, NB: Q2L converters not blocked]. (a) Line  $B_1 - B_2$  dc voltage (pole-to-pole) and power flows in the system [B: Q2L converters blocked, NB: Q2L converters not blocked]. (b) DC voltage and fault current in the faulted line (seen from the transformer end). (c) DC transformer voltages and currents when both Q2L converters are blocked. (d) DC transformer voltages and currents when both Q2L converters are not blocked.

[6]

[7]

[8]

## VIII. REFERENCES

- [1] M. Hajian, D. Jovcic, and W. Bin, "Evaluation of Semiconductor Based Methods for Fault Isolation on High Voltage DC Grids," Smart Grid, IEEE Transactions on, vol. 4, pp. 1171-1179, 2013.

- [2] B. Bachmann, G. Mauthe, E. Ruoss, H. P. Lips, J. Porter, and J. Vithayathil, "Development of a 500kV Airblast HVDC Circuit Breaker," *Power Apparatus and Systems, IEEE Transactions on*, vol. PAS-104, pp. 2460-2466, 1985.

- [3] O. Gomis-Bellmunt, J. Liang, J. Ekanayake, R. King, and N. Jenkins, "Topologies of multiterminal HVDC-VSC transmission for large offshore wind farms," *Electric Power Systems Research*, vol. 81, pp. 271-281, 2// 2011.

- [4] F. o. t. Supergrid, "Roadmap to the Supergrid Technologies Final Report," Available online: http://www.cesi.it/news\_ideas/ideas/Documents/FOSG%20%20WG2%20Final-report.pdf, March 2013.

- [5] B. J. J. Häfner, "Proactive Hybrid HVDC Breakers A key innovation for reliable HVDC grids," presented at the Integrating

- supergrids and microgrids international symposium Bologna, Italy, 2011.

- J. Beerten and R. Belmans, "Analysis of Power Sharing and Voltage Deviations in Droop-Controlled DC Grids," *Power Systems, IEEE Transactions on*, vol. PP, pp. 1-10, 2013.

- A. Egea-Alvarez, F. Bianchi, A. Junyent-Ferre, G. Gross, and O. Gomis-Bellmunt, "Voltage Control of Multiterminal VSC-HVDC Transmission Systems for Offshore Wind Power Plants: Design and Implementation in a Scaled Platform," *Industrial Electronics, IEEE Transactions on*, vol. 60, pp. 2381-2391, 2013.

- O. Gomis-Bellmunt, J. Liang, J. Ekanayake, and N. Jenkins, "Voltage–current characteristics of multiterminal HVDC-VSC for offshore wind farms," *Electric Power Systems Research*, vol. 81, pp. 440-450, 2// 2011.

- [9] T. M. Haileselassie and K. Uhlen, "Precise control of power flow in multiterminal VSC-HVDCs using DC voltage droop control," in Power and Energy Society General Meeting, 2012 IEEE, 2012, pp. 1-9.

- [10] T. Nakajima and S. Irokawa, "A control system for HVDC transmission by voltage sourced converters," in *Power Engineering Society Summer Meeting*, 1999. IEEE, 1999, pp. 1113-1119 vol.2.

- [11] E. Prieto-Araujo, F. D. Bianchi, F. Junyent, x, A., and O. Gomis-Bellmunt, "Methodology for Droop Control Dynamic Analysis of Multiterminal VSC-HVDC Grids for Offshore Wind Farms,"

\*Power Delivery, IEEE Transactions on, vol. 26, pp. 2476-2485, 2011.

- [12] E. Veilleux and O. Boon-Teck, "Multiterminal HVDC With Thyristor Power-Flow Controller," *Power Delivery, IEEE Transactions on*, vol. 27, pp. 1205-1212, 2012.

- [13] R. T. Pinto, P. Bauer, S. F. Rodrigues, E. J. Wiggelinkhuizen, J. Pierik, and B. Ferreira, "A Novel Distributed Direct-Voltage Control Strategy for Grid Integration of Offshore Wind Energy Systems Through MTDC Network," *Industrial Electronics, IEEE Transactions on*, vol. 60, pp. 2429-2441, 2013.

- [14] T. M. U. Ned Mohan, *Power Electronics: Converters, Applications, and Design*, 3rd ed.: John Wiley & Sons Inc., 2003.

- [15] O. Deblecker, A. Moretti, and F. Vallee, "Comparative Study of Soft-Switched Isolated DC-DC Converters for Auxiliary Railway Supply," *Power Electronics, IEEE Transactions on*, vol. 23, pp. 2218-2229, 2008.

- [16] N. Denniston, A. Massoud, S. Ahmed, and P. Enjeti, "Multiple-Module High-Gain High-Voltage DC-DC Transformers for Offshore Wind Energy Systems," *Industrial Electronics, IEEE Transactions on*, vol. 58, pp. 1877-1886, 2011.

- [17] D. S. Gautam and A. K. S. Bhat, "A Comparison of Soft-Switched DC-to-DC Converters for Electrolyzer Application," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 54-63, 2013.

- [18] C. Honnyong, D. Rongjun, T. Qingsong, and F. Z. Peng, "Design and Development of High-Power DC–DC Converter for Metro Vehicle System," *Industry Applications, IEEE Transactions* on, vol. 44, pp. 1795-1804, 2008.

- [19] T. Jimichi, H. Fujita, and H. Akagi, "A Dynamic Voltage Restorer Equipped With a High-Frequency Isolated DC–DC Converter," *Industry Applications, IEEE Transactions on*, vol. 47, pp. 169-175, 2011.

- [20] G. Ortiz, D. Bortis, J. Biela, and J. W. Kolar, "Optimal Design of a 3.5-kV/11-kW DC-DC Converter for Charging Capacitor Banks of Power Modulators," *Plasma Science, IEEE Transactions on*, vol. 38, pp. 2565-2573, 2010.

- [21] A. K. Rathore, A. K. S. Bhat, and R. Oruganti, "Analysis, Design and Experimental Results of Wide Range ZVS Active-Clamped L-L Type Current-Fed DC/DC Converter for Fuel Cells to Utility Interface," *Industrial Electronics, IEEE Transactions on*, vol. 59, pp. 473-485, 2012.

- [22] J. M. Shen, H. L. Jou, and J. C. Wu, "Transformer-less three-port grid-connected power converter for distribution power generation system with dual renewable energy sources," *Power Electronics*, *IET*, vol. 5, pp. 501-509, 2012.

- [23] Y. Xibo, C. Jianyun, and L. Yongdong, "A Transformer-Less High-Power Converter for Large Permanent Magnet Wind Generator Systems," *Sustainable Energy, IEEE Transactions on*, vol. 3, pp. 318-329, 2012.

- [24] S. Xu, A. Q. Huang, S. Lukic, and M. E. Baran, "On Integration of Solid-State Transformer With Zonal DC Microgrid," Smart Grid, IEEE Transactions on, vol. 3, pp. 975-985, 2012.

- [25] W. Zhan and L. Hui, "A Soft Switching Three-phase Current-fed Bidirectional DC-DC Converter With High Efficiency Over a Wide Input Voltage Range," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 669-684, 2012.

- [26] M. S. Almardy and A. K. S. Bhat, "Three-Phase (LC)(L)-Type Series-Resonant Converter With Capacitive Output Filter," *Power Electronics, IEEE Transactions on*, vol. 26, pp. 1172-1183, 2011.

- [27] M. Aredes, R. Dias, A. F. Da Cunha De Aquino, C. Portela, and E. Watanabe, "Going the Distance," *Industrial Electronics Magazine*, *IEEE*, vol. 5, pp. 36-48, 2011.

- [28] M. Aredes, C. Portela, and F. C. Machado, "A 25-MW soft-switching HVDC tap for ±500-kV transmission lines," Power Delivery, IEEE Transactions on, vol. 19, pp. 1835-1842, 2004

- [29] D. Jovcic, "Bidirectional, High-Power DC Transformer," Power Delivery, IEEE Transactions on, vol. 24, pp. 2276-2283, 2009.

- [30] D. Jovcic, "Step-up DC-DC converter for megawatt size applications," *Power Electronics, IET*, vol. 2, pp. 675-685, 2009.

- [31] D. Jovcic and B. T. Ooi, "High-power, resonant DC/DC converter for integration of renewable sources," in *PowerTech*, 2009 IEEE Bucharest, 2009, pp. 1-6.

- [32] D. Jovcic and B. T. Ooi, "Developing DC Transmission Networks Using DC Transformers," *Power Delivery, IEEE Transactions on*, vol. 25, pp. 2535-2543, 2010.

- [33] D. Jovcic, D. Van Hertem, K. Linden, J. P. Taisne, and W. Grieshaber, "Feasibility of DC transmission networks," in Innovative Smart Grid Technologies (ISGT Europe), 2011 2nd IEEE PES International Conference and Exhibition on, 2011, pp. 1-8.

- [34] S. P. Engel, N. Soltau, H. Stagge, and R. W. De Doncker, "Dynamic and Balanced Control of Three-Phase High-Power Dual-Active Bridge DC-DC Converters in DC-Grid Applications," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 1880-1889, 2013.

- [35] B. Hua and C. Mi, "Eliminate Reactive Power and Increase System Efficiency of Isolated Bidirectional Dual-Active-Bridge DC-DC Converters Using Novel Dual-Phase-Shift Control," *Power Electronics, IEEE Transactions on*, vol. 23, pp. 2905-2914, 2008.

- [36] L. Xiaodong and A. K. S. Bhat, "Ac equivalent circuit analysis for high-frequency isolated dual-bridge series resonant dc/dc converter," in *Power Electronics Specialists Conference*, 2008. PESC 2008. IEEE, 2008, pp. 238-244.

- [37] L. Xiaodong and A. K. S. Bhat, "Analysis and Design of High-Frequency Isolated Dual-Bridge Series Resonant DC/DC Converter," Power Electronics, IEEE Transactions on, vol. 25, pp. 850-862, 2010.

- [38] H. van Hoek, M. Neubert, and R. W. De Doncker, "Enhanced Modulation Strategy for a Three-Phase Dual Active Bridge-Boosting Efficiency of an Electric Vehicle Converter," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 5499-5507, 2013.

- [39] R. T. Naayagi, A. J. Forsyth, and R. Shuttleworth, "Bidirectional control of a dual active bridge DC-DC converter for aerospace applications," *Power Electronics, IET*, vol. 5, pp. 1104-1118, 2012.

- [40] G. G. Oggier, M. Ordonez, J. M. Galvez, and F. Luchino, "Fast Transient Boundary Control and Steady-State Operation of the Dual Active Bridge Converter Using the Natural Switching Surface," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 946-957, 2014.

- [41] J. A. Ferreira, "The Multilevel Modular DC Converter," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 4460-4465, 2013.

- [42] K. Ilves, S. Norrga, L. Harnefors, and H. P. Nee, "On Energy Storage Requirements in Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 77-88, 2014.

- [43] S. Qiang, L. Wenhua, L. Xiaoqian, R. Hong, X. Shukai, and L. Licheng, "A Steady-State Analysis Method for a Modular Multilevel Converter," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 3702-3713, 2013.

- [44] G. Minyuan and X. Zheng, "Modeling and Control of a Modular Multilevel Converter-Based HVDC System Under Unbalanced Grid Conditions," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 4858-4867, 2012.

- [45] G. P. Adam, O. Anaya-Lara, G. M. Burt, D. Telford, B. W. Williams, and J. R. McDonald, "Modular multilevel inverter: Pulse width modulation and capacitor balancing technique," *Power Electronics, IET*, vol. 3, pp. 702-715, 2010.

- [46] L. Angquist, A. Antonopoulos, D. Siemaszko, K. Ilves, M. Vasiladiotis, and H. P. Nee, "Open-Loop Control of Modular Multilevel Converters Using Estimation of Stored Energy,"

- Industry Applications, IEEE Transactions on, vol. 47, pp. 2516-2524, 2011

- [47] A. Antonopoulos, L. Angquist, L. Harnefors, K. Ilves, and H. Nee, "Global Asymptotic Stability of Modular Multilevel Converters," *Industrial Electronics, IEEE Transactions on*, vol. PP, pp. 1-1, 2013

- [48] S. Ceballos, J. Pou, C. Sanghun, M. Saeedifard, and V. Agelidis, "Analysis of voltage balancing limits in modular multilevel converters," in *IECON 2011 - 37th Annual Conference on IEEE Industrial Electronics Society*, 2011, pp. 4397-4402.

- [49] N. Cherix, M. Vasiladiotis, and A. Rufer, "Functional modeling and Energetic Macroscopic Representation of Modular Multilevel Converters," in *Power Electronics and Motion Control Conference* (EPE/PEMC), 2012 15th International, pp. LS1a-1.3-1-LS1a-1.3-8.

- [50] D. Fujin and C. Zhe, "A Control Method for Voltage Balancing in Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 66-76, 2014.

- [51] M. Hagiwara and H. Akagi, "Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 24, pp. 1737-1746, 2009.

- [52] K. Ilves, A. Antonopoulos, S. Norrga, and H. P. Nee, "A New Modulation Method for the Modular Multilevel Converter Allowing Fundamental Switching Frequency," *Power Electronics*, *IEEE Transactions on*, vol. 27, pp. 3482-3494, 2012.

- [53] K. Ilves, A. Antonopoulos, S. Norrga, and H. P. Nee, "Steady-State Analysis of Interaction Between Harmonic Components of Arm and Line Quantities of Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 57-68, 2012.

- [54] L. Zixin, W. Ping, Z. Haibin, C. Zunfang, and L. Yaohua, "An Improved Pulse Width Modulation Method for Chopper-Cell-Based Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 3472-3481, 2012.

- [55] L. Zixin, W. Ping, C. Zunfang, Z. Haibin, L. Yongjie, and L. Yaohua, "An Inner Current Suppressing Method for Modular Multilevel Converters," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 4873-4879, 2013.

- [56] S. Rohner, S. Bernet, M. Hiller, and R. Sommer, "Analysis and Simulation of a 6 kV, 6 MVA Modular Multilevel Converter," in *Industrial Electronics*, 2009. IECON '09. 35th Annual Conference of IEEE, 2009, pp. 225-230.

- [57] Y. Zhang, G. P. Adam, T. C. Lim, S. J. Finney, and B. W. Williams, "Voltage source converter in high voltage applications: Multilevel versus two-level converters," in AC and DC Power Transmission, 2010. ACDC. 9th IET International Conference on, 2010, pp. 1-5.

- [58] G. P. Adam, G. O. Anaya-Lara, and G. Burt, "Statcom based on modular multilevel converter: Dynamic performance and transient response during ac network disturbances," in *Power Electronics, Machines and Drives (PEMD)*, 6th IET Intl Conference on, 2012, pp. 1-5.

- [59] H. Barnklau, A. Gensior, and J. Rudolph, "A Model-Based Control Scheme for Modular Multilevel Converters," *Industrial Electronics, IEEE Transactions on*, vol. 60, pp. 5359-5375, 2013.

- [60] S. Gum Tae, L. Hee-Jin, N. Tae Sik, C. Yong-Ho, L. Uk-Hwa, et al., "Design and Control of a Modular Multilevel HVDC Converter With Redundant Power Modules for Noninterruptible Energy Transfer," Power Delivery, IEEE Transactions on, vol. 27, pp. 1611-1619, 2012.

I.A. Gowaid received his B.Sc. (first class honors) and M.Sc. degrees in Electrical Engineering from Alexandria University, Egypt in 2007 and 2011 respectively. He is currently pursuing his PhD studies at the University of Strathclyde, Glasgow, UK. He worked at the department of electrical engineering at Alexandria University where he was appointed as a demonstrator in 2008 and as an assistant lecturer in 2012. Since 2010, he is with Spiretronic LLC as a research assistant. His research interests include

Renewable Energy Integration, Power System Dynamics, Power Electronics and HVDC.

G.P. Adam received a first class BSc and MSc from Sudan University for Science and Technology, Sudan in 1998 and 2002 respectively; and. a PhD in Power Electronics from University of Strathclyde in 2007. He has been working as a research fellow with Institute of Energy and Environment, University of Strathclyde in Glasgow, UK, since 2008. His research interests are fault tolerant voltage source converters for HVDC systems; control of HVDC transmission

systems and multi-terminal HVDC networks; voltage source converter based FACTS devices; and grid integration issues of renewable energies. Dr Adam has authored and co-authored several technical reports, and journal and conference papers in the area of multilevel converters and HVDC systems, and grid integration of renewable power. Also, he is actively contributing to reviewing process for several IEEE and IET Transactions and Journals, and conferences. Dr Adam is an active member of IEEE and IEEE Power Electronics Society.

Ahmed M. Massoud (SM'11) received the B.Sc. (first class honors) and M.Sc. degrees from the Faculty of Engineering, Alexandria University, Egypt, in 1997 and 2000, respectively, and the Ph.D. degree in electrical engineering from the Computing and Electrical Department, Heriot-Watt University, Edinburgh, U.K., in 2004. From 2005 to 2008, he was a Research Fellow at Strathclyde University, Glasgow, U.K. From 2008 to 2009, he was a Research Fellow at Texas A&M at Qatar, Doha, Qatar. From 2009 to 2012, he was an Assistant

Professor at the Department of Electrical Engineering, College of Engineering, Qatar University, where he is currently an Associate Professor in the same department. His research interests include Power Electronics, Energy Conversion, Renewable Energy and Power Quality.

Shehab Ahmed (SM'12) was born in Kuwait City, Kuwait in July 1976. He received the B.Sc. degree in Electrical Engineering from Alexandria University, Alexandria, Egypt, in 1999; the M.Sc. and Ph.D. degrees from the Department of Electrical & Computer Engineering, Texas A&M University, College Station, TX in 2000 and 2007, respectively. From 2001 to 2007, he was with Schlumberger Technology Corporation working on downhole mechatronic systems. He is currently an Assistant Professor with Texas A&M University at Qatar,

Doha, Qatar. His research interests include mechatronics, solid-state power conversion, electric machines, and drives.

**Derrick Holliday** has research interests in the areas of power electronics, electrical machines and drives. In 1995 he obtained the degree of PhD from Heriot Watt University and, since then, has held full-time academic posts at the Universities of Bristol and Strathclyde. He has authored or co-authored over 70 academic journal and conference publications. He is currently leading industrially funded research in the field of power electronics for HVDC applications, and is co-investigator on research programmes in the

fields photovoltaic systems and the interface of renewable energy to HVDC systems.

**B.W. Williams** received the M.Eng.Sc. degree from the University of Adelaide, Australia, in 1978, and the Ph.D. degree from Cambridge University, Cambridge, U.K., in 1980. After seven years as a Lecturer at Imperial College, University of London, U.K., he was appointed to a Chair of Electrical Engineering at Heriot-Watt University, Edinburgh, U.K., in 1986. He is currently a Professor at Strathclyde University, U.K. His teaching covers power electronics (in which he has a free internet text) and drive systems. His research

activities include power semiconductor modelling and protection, converter topologies, soft switching techniques, and application of ASICs and microprocessors to industrial electronics.