# University of Strathclyde

# Department of Electronic and Electrical Engineering

# Measurement, control and protection of microgrids at low frame rates supporting security of supply

Volume 1

Andrew Roscoe

A thesis presented in fulfillment of the requirements for the degree of Doctor of Philosophy

February 2009

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has lead to the award of a degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Signed :

Date :

#### Acknowledgements:

The author gratefully acknowledges the guidance given by Prof. Graeme Burt at the University of Strathclyde, the funding provided by Rolls-Royce, and the support of Dr. Nina Roscoe.

# Contents

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Distributed generation and microgrid background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                                                                                     |

| 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Measurements at low frame rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                                                                                                                                                                     |

| 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reliable detection of loss-of-mains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                                                                                                                                                                                     |

| 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Structure of this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                                                                                                                     |

| 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | References for chapter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                                                                                                                     |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | System study of amplitude, phase and frequency measureme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nt                                                                                                                                                                                                                                     |

| requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s within 3-phase AC microgrids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                                                                                                                                                                                                                                     |

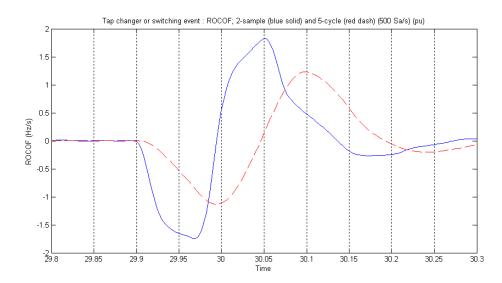

| 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Increased rates of change of frequency within microgrids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                                                                                                                                                                     |

| 2.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of frequency measurement requirements (ROCOF and reaction time) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                     |

| 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Frequency measurement range requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                        |

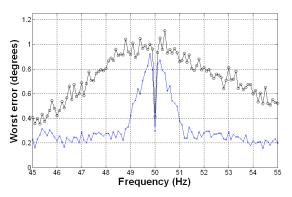

| 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Frequency measurement accuracy requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                        |

| 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Voltage amplitude measurement speed and accuracy requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                        |

| 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Current amplitude measurement speed and accuracy requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                        |

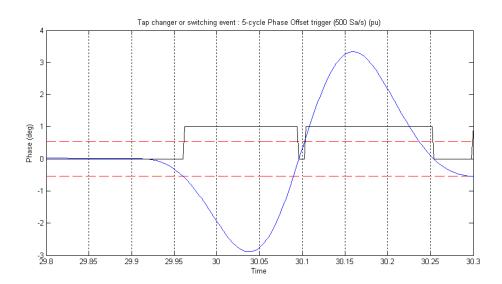

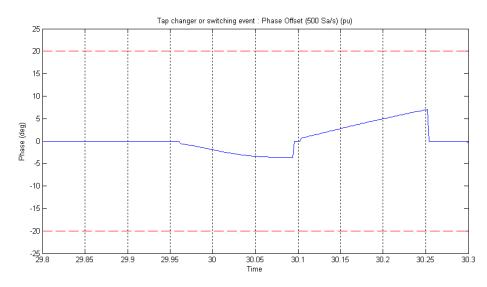

| 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Phase measurement speed and accuracy requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                        |

| 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Required tolerance to signals with poor power quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                                                                                                                                                                     |

| 2.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Unbalance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                                                                                                                                                                                     |

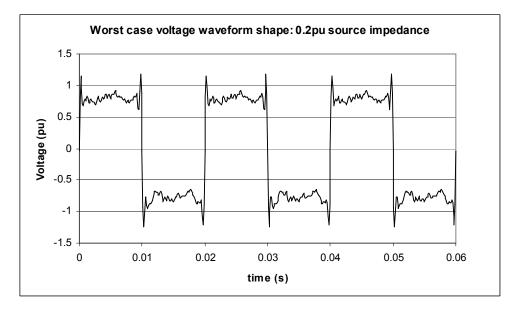

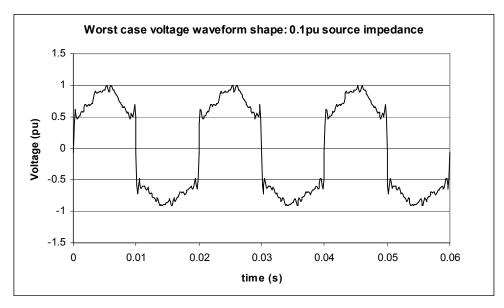

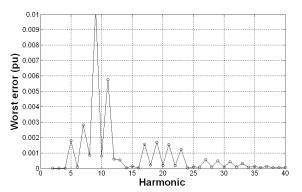

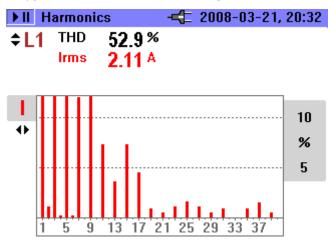

| 2.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Harmonic content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                                                                                                                                                                     |

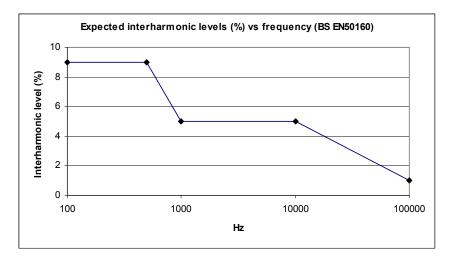

| 2.7.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Inter-harmonic content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                                                                                                                                                                                                                     |

| 2.7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Flicker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                                                                                                                                                     |

| 2.7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Tolerance to voltage dips and surges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                     |

| 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Loss of mains requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                                                                                                                                     |

| 2.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Measurement hardware and sample rate considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60                                                                                                                                                                                                                                     |

| 2.40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                        |

| 2.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Overall amplitude and frequency measurement specifications (for volta measurements)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                        |

| 2.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | measurements)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>66                                                                                                                                                                                                                               |

| 2.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | measurements)<br>Generation of suitable test waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63<br>66<br>67                                                                                                                                                                                                                         |

| <b>2.11</b> 2.11.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | measurements)<br>Generation of suitable test waveforms<br>Waveform 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63<br>66<br>67<br>67                                                                                                                                                                                                                   |

| <b>2.11</b><br>2.11.1<br>2.11.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | measurements)<br>Generation of suitable test waveforms<br>Waveform 1<br>Waveform 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63<br>66<br>67<br>67<br>68                                                                                                                                                                                                             |

| 2.11<br>2.11.1<br>2.11.2<br>2.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | measurements)<br>Generation of suitable test waveforms.<br>Waveform 1<br>Waveform 2<br>References for chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> </ul>                                                                                                                                                     |

| 2.11<br>2.11.1<br>2.11.2<br>2.12<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | measurements)<br>Generation of suitable test waveforms.<br>Waveform 1<br>Waveform 2<br>References for chapter 2<br>Measurement of voltage or current amplitudes & phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> <li>72</li> </ul>                                                                                                                                         |

| 2.11<br>2.11.1<br>2.11.2<br>2.12<br>3<br>3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | measurements)<br>Generation of suitable test waveforms.<br>Waveform 1<br>Waveform 2<br>References for chapter 2<br>Measurement of voltage or current amplitudes & phases<br>Documented methods relevant to chapters 3 & 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> <li>72</li> <li>73</li> </ul>                                                                                                                             |

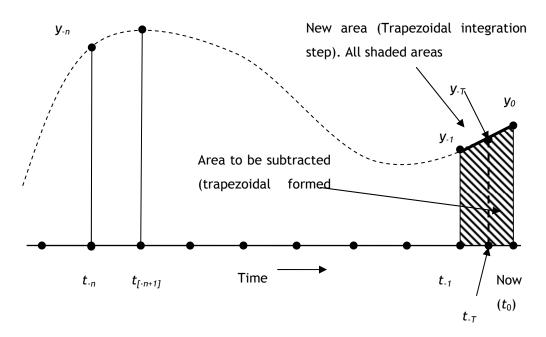

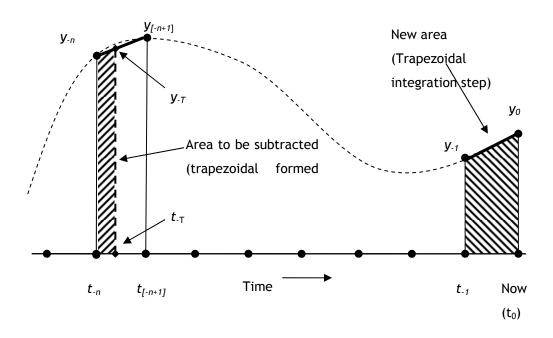

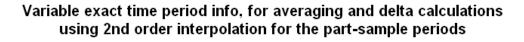

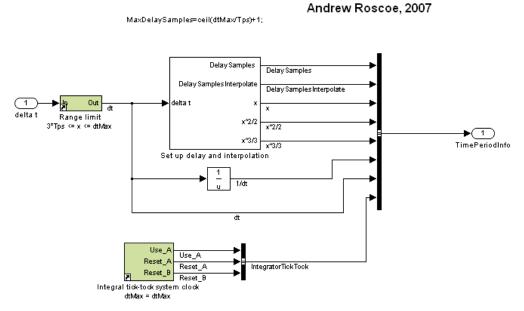

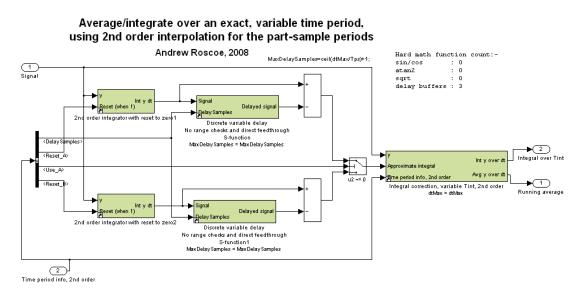

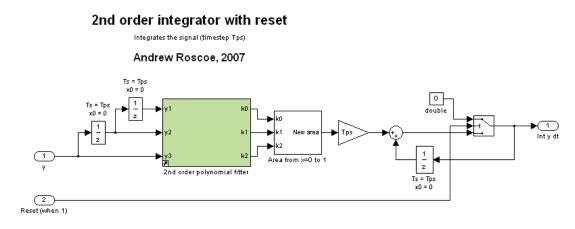

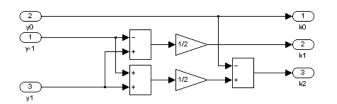

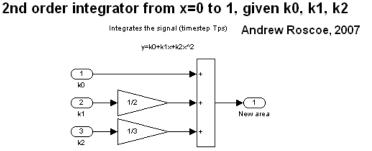

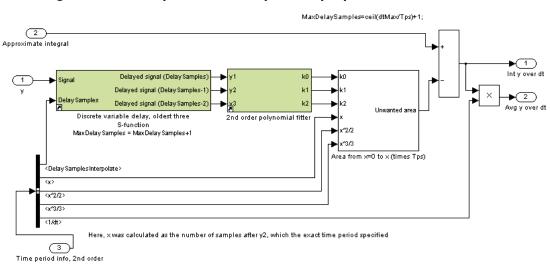

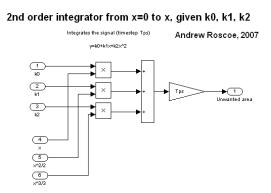

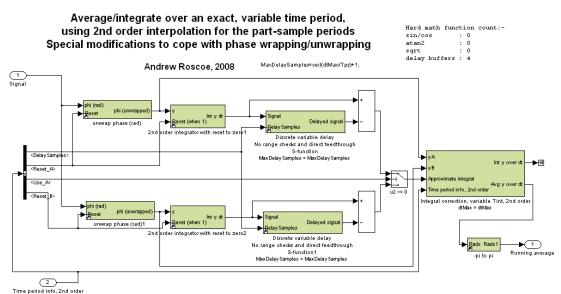

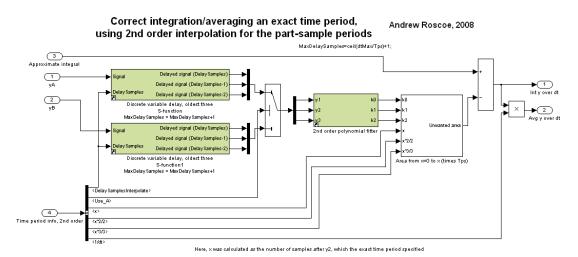

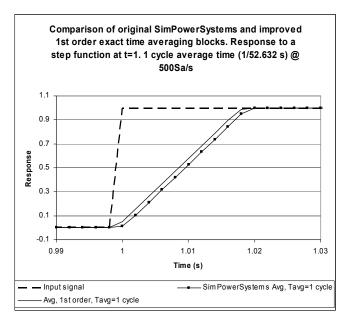

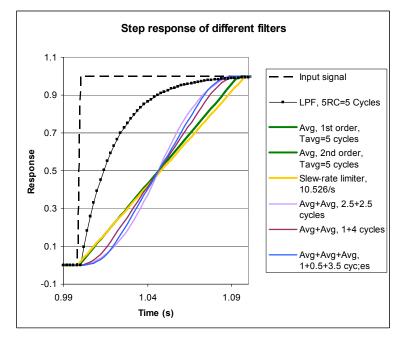

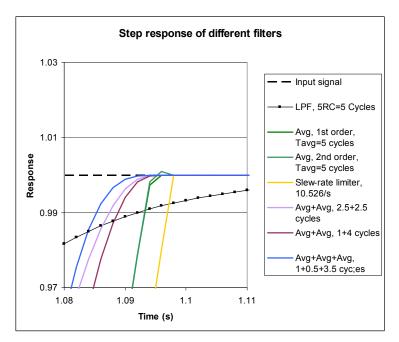

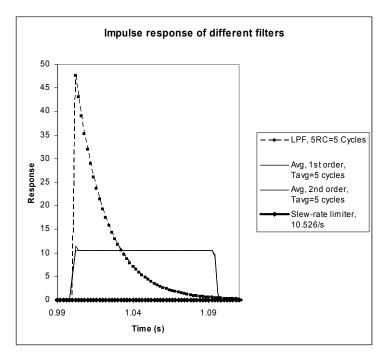

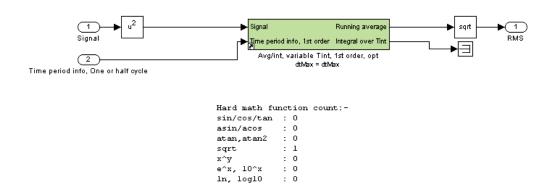

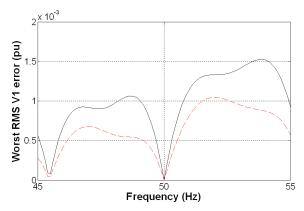

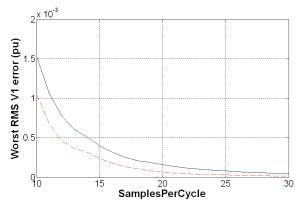

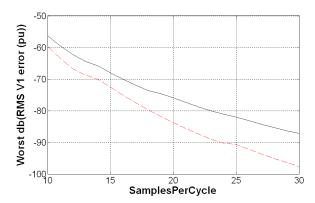

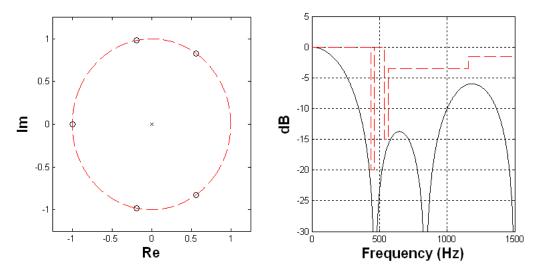

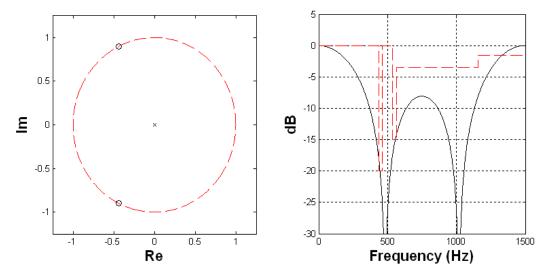

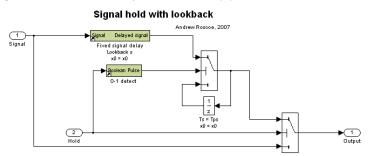

| 2.11<br>2.11.1<br>2.11.2<br>2.12<br>3<br>3.1<br>3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | measurements)<br>Generation of suitable test waveforms.<br>Waveform 1<br>Waveform 2<br>References for chapter 2<br>Measurement of voltage or current amplitudes & phases<br>Documented methods relevant to chapters 3 & 4.<br>Averaging signals over exact time periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> <li>72</li> <li>73</li> <li>76</li> </ul>                                                                                                                 |

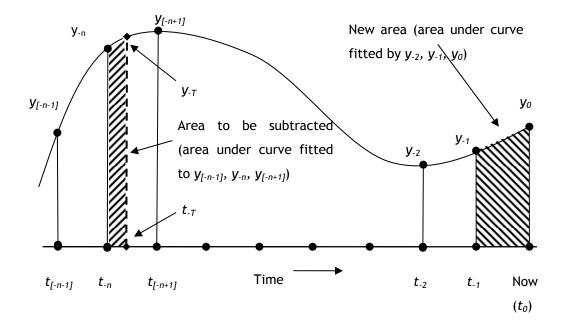

| 2.11<br>2.11.1<br>2.11.2<br>2.12<br>3<br>3.1<br>3.2<br>3.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | measurements)<br>Generation of suitable test waveforms.<br>Waveform 1<br>Waveform 2<br>References for chapter 2<br>Measurement of voltage or current amplitudes & phases<br>Documented methods relevant to chapters 3 & 4<br>Averaging signals over exact time periods<br>Improving the latency of the exact-time averaging<br>Extension to 2 <sup>nd</sup> order interpolation                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> <li>72</li> <li>73</li> <li>76</li> <li>77</li> </ul>                                                                                                     |

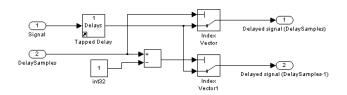

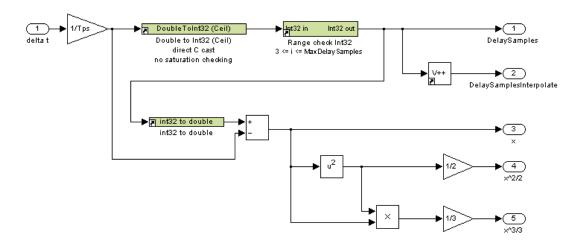

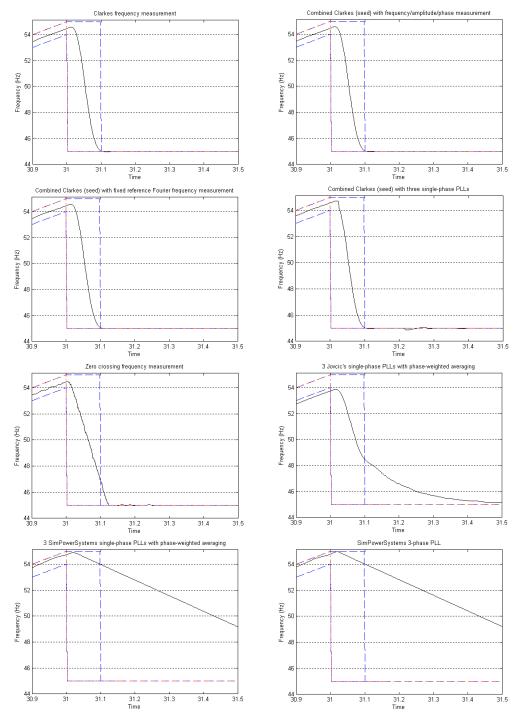

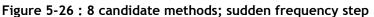

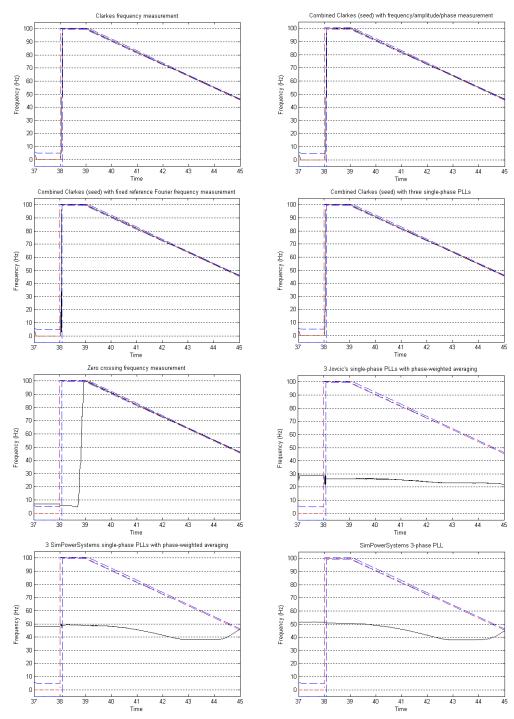

| 2.11<br>2.11.1<br>2.11.2<br>2.12<br>3<br>3.1<br>3.2<br>3.2.1<br>3.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | measurements)         Generation of suitable test waveforms.         Waveform 1         Waveform 2         References for chapter 2         Measurement of voltage or current amplitudes & phases         Documented methods relevant to chapters 3 & 4.         Averaging signals over exact time periods         Improving the latency of the exact-time averaging         Extension to 2 <sup>nd</sup> order interpolation         Avoidance of integrator wind-up, and algorithm detail overview.                                                                                                                                                                                                                                                                         | <ul> <li>63</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>70</li> <li>72</li> <li>73</li> <li>76</li> <li>77</li> <li>78</li> </ul>                                                                                         |