#### 1

# Enhanced Independent Pole Control of Hybrid MMC-HVDC System

Wang Xiang, Student Member, IEEE, Weixing Lin, Member, IEEE, Lie Xu, Senior Member, IEEE, Jinyu Wen, Member, IEEE

Abstract—This paper presents an enhanced independent pole control scheme for hybrid modular multilevel converter (MMC) based on full bridge sub-module (FBSM) and half bridge sub-module (HBSM). A detailed analysis of power distribution between upper and lower arms under asymmetrical DC pole voltages is presented. It is found that the fundamental AC currents in the upper and lower arms are asymmetrical. To enable operation under asymmetrical DC pole voltages, an enhanced independent pole control scheme is proposed. The controller is composed of two DC control loops, two AC control loops and circulating current suppression control based on current injection. Six modulation indices are presented to independently control the upper and lower arms. With this controller, the DC voltage operating region is significantly extended. To ride through pole to ground DC fault without bringing DC bias at the neutral point of interface transformer, a pole to ground DC fault ride through strategy is proposed. Feasibility and effectiveness of the proposed control scheme are verified by simulation results using PSCAD/EMTDC.

Index Terms— Asymmetrical DC pole voltage, DC pole to ground fault, DC pole to pole fault, energy balance, hybrid MMC, overhead line.

#### I. INTRODUCTION

Increasing demand for integrating bulk onshore renewable energy over long distance has promoted researches on MMC-HVDC (modular multilevel converter based HVDC) transmission using overhead lines [1][2]. To deal with the frequent DC faults on overhead lines, several DC fault tolerant topologies have been proposed [2]-[5]. Although these topologies can isolate the fault current by blocking the IGBTs of the MMC, it prolongs the shutdown of the entire HVDC system and loses the ability to continuously support the AC system during DC faults [6].

To ride through DC faults without blocking the IGBTs, the hybrid MMC based on full bridge sub-module (FBSM) and half bridge sub-module (HBSM) has drawn significant attention in the last few years [7]. The hybrid MMC utilizes the

This work is sponsored by the National Key Research and Development project (2016YFB0901002) and the China Postdoctoral Science Foundation (2016T90690).

W. Xiang, W. Lin and J. Wen are with State Key Laboratory of Advanced Electromagnetic Engineering and Technology, Huazhong University of Science and Technology, Wuhan 430074, China. W. Lin is also with the TBEA China Xinjiang Sunoasis Co. Ltd. Xi'an 710000, China (e-mail: xiangwang1003 @foxmail.com, weixinglin@foxmail.com, jinyu.wen @mail.hust.edu.cn)

L. Xu is with the Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow G1 1XW, U.K. (e-mail: lie.xu@strath.ac.uk)

negative voltage output ability and has the merits of fast DC fault current clearance, flexible DC voltage manipulation, and quick system recovery. The design, operation and improved PWM modulation of hybrid MMC have been discussed in [7]-[9]. Its pre-charging and pole-to-pole DC fault ride through strategy were studied in [10], and in [11] an optimal design method to determine the number of FBSM and HBSM was presented and a DC modulation index and elementary control were also introduced.

However, most of the existing literatures have mainly focused on the design, operation and control of hybrid MMC under symmetrical DC pole conditions. Limited attention has been paid to asymmetrical conditions which are common in practical applications. For the HB MMC, reference [12] analysed the behaviour of HB MMC under asymmetrical arm impedance and a differential mode controller, a common mode controller and power balance controller for each phase whereas were designed. An asymmetric control mode for HB MMC to suppress capacitor voltage ripples in low frequency low voltage motor drive applications was proposed in [13]. References [14] and [15] studied the general performance of HB MMC under asymmetrical DC pole voltages and it was reported that there would be DC bias voltage and current at the secondary side of the interface transformer, which increase the cost of insulation and manufacturing of the transformers. To enable operation under DC pole imbalance, [15] proposed a method of controlling the current injected into the star-point reactor of the interface transformer though this method interferes the third harmonic voltage injection of HB MMC leading to reduced MMC voltage margins.

Compared with the HB MMC, hybrid MMC has more control freedoms and can have better performance under asymmetrical conditions. Reference [16] studied the operation of MMC with asymmetrical arm configurations. Double-loop controllers are re-designed for the upper and lower arms separately to decouple the AC/DC voltage offset. However, the DC faults handing ability of the proposed controller was not validated. An enhanced fault ride through control for hybrid MMC was presented in [17] where an additional phase angle was introduced to balance the power between the upper and lower arms during a pole-to-ground (PTG) DC fault.

The main contribution of this paper is to presents a novel independent pole control scheme for hybrid MMC-HVDC system to enable continuous operation under asymmetrical DC pole voltages and DC faults. With the independent control scheme, the hybrid MMC is able to continuously operate under asymmetrical DC pole voltages and ride through PTG DC fault without bringing DC bias at the neutral point of the interface transformer. Thus, a symmetrical monopole MMC-HVDC system can be operated as a bi-pole HVDC

system.

This paper is organised as follows. Section II depicts the operating principle of hybrid MMC under asymmetrical DC pole voltages. Based on the analysis, section III proposes an independent pole control scheme to independently control the upper and lower arms. To ride through the PTG DC fault, a fault ride through strategy is proposed in section IV. The effectiveness of the proposed control is verified by simulations in section V, and finally, conclusions are drawn in section VI.

# II. ANALYSIS OF HYBRID MMC UNDER ASYMMETRICAL DC POLE VOLTAGES

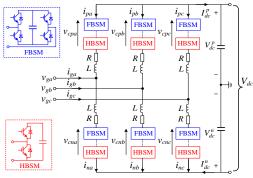

The circuit configuration of a three-phase hybrid MMC is depicted in Fig. 1. Each converter arm has N sub-modules that are consisted of  $N_{fb}$  FBSM and  $N_{hb}$  HBSM. Topologies of the FBSM and HBSM are shown in Fig. 1.

In Fig. 1,  $V_{dc}^p$  and  $V_{dc}^n$  are the respective potentials of positive and negative DC poles.  $I_{dc}^p$  and  $I_{dc}^n$  are the DC pole currents.  $v_{gi}$  and  $i_{gi}$  are the respective output AC phase voltage and current;  $v_{cpi}$  and  $v_{cni}$  are the arm voltages generated by the N SMs;  $i_{pi}$  and  $i_{ni}$  are the upper and lower arm currents, where the subscript i refers to phase a, b, c. C is the SM capacitance. L and R are the arm inductance and resistance.  $S_n$ ,  $V_{dcn}$ ,  $I_{dcn}$ ,  $V_{cn}$  are the rated transmitting power, rated DC pole to pole voltage, rated DC pole current and rated SM capacitor voltage, respectively.

Fig. 1. Topology of hybrid MMC based on FBSM and HBSM.

Taking phase *a* as an example, the phase voltage and current can be expressed as:

$$\begin{cases} v_{ga} = V_m \cos \omega t \\ i_{ga} = I_m \cos (\omega t + \varphi_a) \end{cases}$$

(1)

where  $V_m$  and  $I_m$  are the amplitude of the phase voltage and current.  $\varphi_a$  is the angle difference between the phase voltage and current. According to [18], each arm current mainly contains a DC component, a fundamental frequency component and a second order harmonic component. Thus, the arm currents can be denoted as

$$\begin{cases} i_{pa} = I_{pa0} - I_{pa1m} \cos(\omega t + \varphi_a) + I_{pa2m} \cos(2\omega t + \varphi_{2a}) \\ i_{na} = I_{na0} + I_{na1m} \cos(\omega t + \varphi_a) + I_{na2m} \cos(2\omega t + \varphi_{2a}) \end{cases}$$

(2)

where  $I_{ja0}$ ,  $I_{ja1m}$ ,  $I_{ja2m}$  (j=p, n) are the amplitudes of the DC component, the fundamental frequency component and the second order harmonic component in arm currents, respectively.  $\varphi_{2a}$  is the phase angle of the second order

harmonic component in the arm current. Neglecting the high order components and the resistive voltage drops on arm inductors, the instantaneous power absorbed by the SM capacitors on the upper arm can be obtained

$$\begin{aligned} p_{pa} &= v_{cpa} \cdot i_{pa} = (V_{dc}^{p} - v_{ga}) \cdot i_{pa} \\ &= V_{dc}^{p} I_{pa0} + \frac{V_{m} I_{pa1m} \cos \varphi_{a}}{2} - V_{m} I_{pa0} \cos \omega t - V_{dc}^{p} I_{pa1m} \cos(\omega t + \varphi_{a}) \\ &- \frac{V_{m} I_{pa2m} \cos(\omega t + \varphi_{2a})}{2} + \frac{V_{m} I_{pa1m} \cos(2\omega t + \varphi_{a})}{2} \\ &+ V_{dc}^{p} I_{na2m} \cos(2\omega t + \varphi_{2a}) \end{aligned} \tag{3}$$

Similarly, the instantaneous power absorbed by the SM capacitors on the lower arm is

$$\begin{aligned} p_{na} &= v_{cna} \cdot i_{na} = (v_{ga} - V_{dc}^{n}) \cdot i_{na} \\ &= -V_{dc}^{n} I_{na0} + \frac{V_{m} I_{na1m} \cos \varphi_{a}}{2} + V_{m} I_{na0} \cos \omega t - V_{dc}^{n} I_{na1m} \cos(\omega t + \varphi_{a}) \\ &+ \frac{V_{m} I_{na2m} \cos(\omega t + \varphi_{2a})}{2} + \frac{V_{m} I_{na1m} \cos(2\omega t + \varphi_{a})}{2} \\ &- V_{dc}^{n} I_{na2m} \cos(2\omega t + \varphi_{2a}) \end{aligned} \tag{4}$$

To balance the transferred power between the AC and DC systems, the integral of (3) and (4) in one fundamental cycle should be zero. Therefore, there are

$$\begin{cases} V_{dc}^{p} I_{pa0} + \frac{V_{m} I_{pa1m} \cos \varphi_{a}}{2} = 0\\ -V_{dc}^{n} I_{na0} + \frac{V_{m} I_{na1m} \cos \varphi_{a}}{2} = 0 \end{cases}$$

(5)

Since the sum of three-phase arm currents is equal to the DC pole current,  $I_{pa0}$  and  $I_{na0}$  can be calculated as

$$I_{pa0} = -\frac{I_{dc}^p}{3}, I_{na0} = -\frac{I_{dc}^n}{3}$$

(6)

Substituting (6) into (5) and considering that  $I_{dc}^p$  equals  $I_{dc}^n$  during steady state, there is

$$-\frac{V_{dc}^{p}}{V_{dc}^{n}} = \frac{I_{palm}}{I_{nalm}} \tag{7}$$

Considering  $i_{na}$ - $i_{pa}$ = $i_{ga}$ , the fundamental frequency components in the upper and lower arm currents can be calculated as

$$\begin{cases} i_{pa1} = \frac{V_{dc}^{p}}{V_{dc}^{p} - V_{dc}^{n}} i_{ga} \\ i_{na1} = \frac{-V_{dc}^{n}}{V_{dc}^{p} - V_{dc}^{n}} i_{ga} \end{cases}$$

(8)

The circulating current  $i_{diffa}$  on phase a can be therefore calculated as

$$i_{diffa} = \frac{i_{pa} + i_{na}}{2} = -\frac{I_{dcn}}{3} - \frac{V_{dc}^{p} + V_{dc}^{n}}{2(V_{dc}^{p} - V_{dc}^{n})} i_{ga} + i_{diff 2}$$

(9)

where  $i_{dfiff2}$  denotes the second order frequency component.

Comparing with operation under symmetrical condition, it can be concluded from the above analysis that: 1) the peak value of the fundamental frequency components in the upper and lower arm currents are proportional to the potential of the DC pole voltages as shown in (7); 2) there is a fundamental frequency component existing in the circulating current as

shown in (9); 3) the positive and negative poles can be separately controlled if the AC and DC components in the upper and lower arm currents are independently controlled.

#### III. INDEPENDENT POLE CONTROL OF HYBRID MMC

#### A. DC Pole Voltage/Power Control

As reported in [11] and [19], the AC output voltage of phase *a* can be controlled by

$$v_{ga} = m_a \frac{V_{armdcn}}{2} \cos \omega t \tag{10}$$

where  $m_a$  is the AC modulation index of phase a ( $0 < m_a \le 1$ ).  $V_{armdcn}$  is the DC component in arm voltage which is the same as nominal DC voltage under steady state conditions ( $V_{armdcn} = V_{dcn}$ ).

To regulate the DC pole voltages independently, two DC modulation indices  $M_{dc}^p$  and  $M_{dc}^n$  are introduced

$$V_{cp\_dc} = M_{dc}^{p} \frac{V_{armdcn}}{2}, V_{cn\_dc} = M_{dc}^{n} \frac{V_{armdcn}}{2}$$

(11)

where  $V_{cp\_dc}$ ,  $V_{cn\_dc}$  are the DC components in arm voltages. The arm voltages can be re-written as

$$v_{cpa} = \frac{V_{armdcn}}{2} (M_{dc}^p - m_a \cos \omega t), v_{cna} = \frac{V_{armdcn}}{2} (m_a \cos \omega t - M_{dc}^n)$$

(12)

The dynamic of the upper arm current of phase a is obtained

$$L\frac{di_{pa}}{dt} + Ri_{pa} = V_{dc}^{p} - \frac{1}{2}M_{dc}^{p}V_{armdcn}$$

(13)

Adding up the three upper arms of the three-phase and considering  $i_{pa}+i_{pb}+i_{pc}=-I_{dc}^{p}$  result

$$L\frac{dI_{dc}^{p}}{dt} + RI_{dc}^{p} = \frac{3}{2}M_{dc}^{p}V_{armden} - 3V_{dc}^{p}$$

(14)

Let  $V_{com}^p = 3M_{dc}^p V_{armdcn}/2 - 3V_{dc}^p$  then it can be obtained from the PI controller as

$$V_{com}^{p} = K_{p} (I_{dcref}^{p} - I_{dcpu}^{p}) + K_{i} \int (I_{dcref}^{p} - I_{dcpu}^{p}) dt$$

(15)

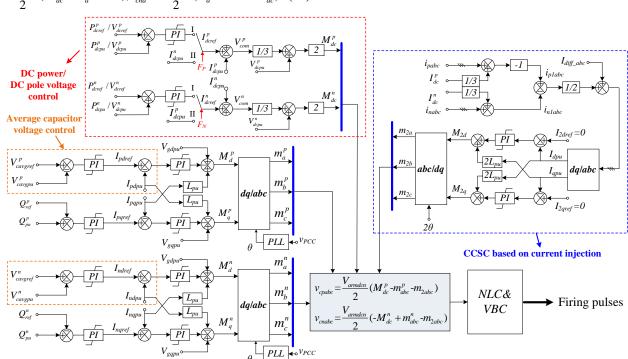

Based on (15), an inner DC current control can be designed for the positive pole as shown in Fig. 2. Taking into account the active power transmitted to the DC positive pole, it satisfies:

$$P_{dc}^p = V_{dc}^p \cdot I_{dc}^p \tag{16}$$

Combining (16) with (15), the DC power/ pole voltage control can be implemented as an outer DC control loop, shown in Fig. 2. Similarly, the DC power/ voltage control and inner DC current control can be designed for the negative pole. It can be concluded that, by controlling  $M_{dc}^{p}$  and  $M_{dc}^{n}$ , the independent DC pole power/ voltage control can be achieved.

Fig. 2. Control diagram of independent pole control.

## B. Capacitor Energy Control

For the upper arms, the active power injected into the hybrid MMC from the AC system can be expressed as:

$$P_{ac}^{p} = \frac{3}{2} v_{gd} i_{pd} \tag{17}$$

where  $i_{pd}$  is the *d-axis* component of  $i_{pal}$ ,  $i_{pbl}$  and  $i_{pcl}$  in dq rotating frame. The instantaneous power transmitted to the DC system satisfies:

$$\frac{3}{2}v_{gd}i_{pd} = P_{dc} + P_{csm}^{p} \tag{18}$$

where  $P_{csm}^{p}$  is the power absorbed by the SMs on the upper arms and can be expressed as:

$$P_{csm}^{p} = 3Nd(\frac{1}{2}CV_{cavg}^{p2}) / dt = 3NCV_{cavg}^{p} dV_{cavg}^{p} / dt$$

(19)

where  $V_{cavg}^p$  is the average capacitor voltage of the 3N SMs on the upper arms.

To balance the instantaneous power between the DC and

AC systems at any instant, the power absorbed by the SMs should be controlled to zero. By combining (18) and (19), an average capacitor voltage control can be designed as the outer AC control loop which controls the average capacitor voltage to be the set value and generates the *d*-axis current order [11].

Similarly, an average capacitor voltage control can be designed for the lower arms.

In Fig. 2,  $V_{gdpu}$  and  $V_{gqpu}$  are the dq components of the phase voltage in per unit form.  $v_{PCC}$  is the AC voltage at the PCC (Point of common coupling).  $(M_d^p, M_q^p, M_d^n, M_q^n)$  are the modulation indices in the dq rotating frame generated by the inner AC current control loop.

# C. Circulating Current Suppression Control Based on Current Injection

To suppress the second order fundamental frequency component in the circulating currents, the circulating current suppression control (CCSC) proposed in [20] can be used. However, referring to (9), there is also an AC fundamental frequency components in the circulating current  $i_{diffi}$  (i=a, b, c) under asymmetrical DC pole voltages. As a result, high order harmonics will be deduced using dq transformation in the double fundamental frequency, negative sequence rotational reference frame.

To extract the second order frequency component, as seen in (9), the fundamental frequency component should be compensated. Therefore, the current injection method is re-designed for the CCSC as:

$$\dot{i}_{inject\_i} = \frac{\dot{i}_{pi1} - \dot{i}_{ni1}}{2} \tag{20}$$

As shown in Fig. 2, the compensated current is injected as the input of CCSC.

Since the detailed design of nearest level control (NLC) and capacitor voltage balancing control (VBC) has been reported in [1] and [11], they will not be described further in this paper.

#### D. Operating Region of DC Pole Voltage

According to (5), (10) and (11), for the upper arm of phase a, there is

$$I_{palm} = 2M_{dc}^{p} I_{dc}^{p} / (3m_a \cos \varphi_a)$$

(21)

To ensure successful voltage balancing of the HBSMs, (22) should be satisfied.

$$I_{palm} \ge \left| I_{pa0} \right| = \left| I_{dc}^p / 3 \right| \tag{22}$$

Therefore,  $M_{dc}^p$  should satisfy:

$$M_{dc}^{p} \ge m_a \cos \varphi_a / 2 \tag{23}$$

It can be seen from (23) that the minimum DC pole voltage is 0.5 (in pu term relative to  $V_{dcn}/2$ ) under unit power factor. To enable operation under lower DC pole voltage, a feasible approach is to insert all  $N_{fb}$  FBSMs on each arm. Referring to (12), the output voltage of the upper arm meets

$$-N_{fb}V_{cn} \le v_{cpi} = \frac{V_{armdcn}}{2} (M_{dc}^{p} - m_{a}\cos\omega t) \le N_{fb}V_{cn} \quad (24)$$

Since  $V_{cn}=V_{dcn}/N$ , there is

$$-2N_{fb}/N+m_a\cos\omega t\leq M_{dc}^p\leq 2N_{fb}/N+m_a\cos\omega t\quad (25)$$

To always meet(25),  $M_{dc}^{p}$  should satisfy

$$m_a - 2N_{fb} / N \le M_{dc}^p \le 2N_{fb} / N - m_a$$

(26)

Equation (26) shows that the minimum value of  $M_{dc}^{\rho}$  can be equal to  $(m_a$ - $2N_{fb}/N)$ . Similar relationship can be derived for the lower arms as

$$m_a - 2N_{fb} / N \le M_{dc}^n \le 2N_{fb} / N - m_a$$

(27)

Equation (27) shows that the maximum value of  $M_{dc}^n$  can be equal to  $(2N_{fb}/N-m_a)$ . Taking  $N_{fb}=N_{hb}=N/2$  and m=0.9 as an example, (26) and (27) become

$$-0.1 \le M_{dc}^p, \ M_{dc}^n \le 0.1$$

(28)

It shows that the minimum and maximum values of  $M_{dc}^p$  are -0.1 and 0.1 (in pu term relative to  $V_{dcn}/2$ ) respectively. Therefore, with all the FBSMs inserted, the hybrid MMC is able to operate under the DC pole to pole voltage in the range of -0.1~0.1 $V_{dcn}$ .

As for  $M_{dc}^p$ , within the range of (0.1~0.5), HBSMs should be inserted to provide sufficient positive voltage, contributing to the total arm voltage in (12). However, to avoid HBSM voltage balancing problem and meet(23), the power factor  $\cos \varphi_a$  shown in (23) should be decreased.

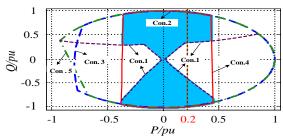

Using the dynamic phasor model proposed in [21], Fig. 3 depicts the PQ operating zone of the upper arms versus several constraints under  $V_{dc}^p$ =0.2pu. The DC base voltage, current, and apparent power are defined respectively as  $V_{base}$ = $V_{dcn}$ /2,  $I_{base}$ = $I_{dcn}$ ,  $S_{base}$ = $S_n$ /2. It can be seen from Fig. 3 that at 0.2 pu DC voltage, the upper arms of hybrid MMC is able to operate under 1pu DC pole current (namely, 0.2pu active power) unless 0.5~1pu capacitive or 0.4~1pu inductive reactive power is provided.

Fig. 3. PQ operating zone of positive pole when  $V_{dc}^{p}=0.2pu$ . Con.1, voltage balancing constraint. Con.2, converter capacity constraint. Con.3, maximum arm current constraint (2pu). Con.4, maximum DC current constraint (2pu). Con.5, capacitor voltage fluctuation constraint  $(\pm 10\%)$ .

In conclusion, for hybrid MMC with half FBSM and half HBSM, the operating region of DC pole voltage can be extended to  $-0.1 \sim 1 pu$ .

#### IV. FAULT RIDE THROUGH OF PTG DC FAULT

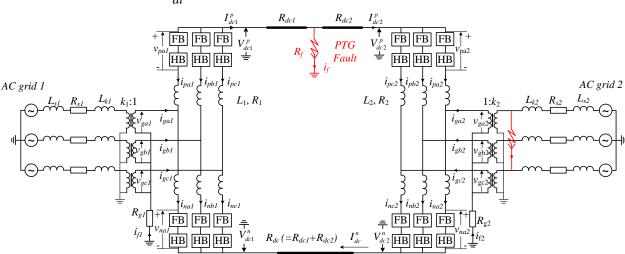

As for the most severe asymmetrical condition, the dynamics of the hybrid MMC during PTG DC fault is analysed. Fig. 4 shows the circuit diagram of a two-terminal HVDC system based on the hybrid MMC. The grounding configuration of the interface transformer adopts the high resistance grounding method implemented in the *Yunnan Luxi* MMC-HVDC asynchronous interconnection project [22].

Assuming the positive pole is subjected to a PTG DC fault, by using Kirchhoff's Voltage Law (KVL) and Kirchhoff's

Current Law (KCL), the following equations can be derived for the upper arms of the three-phase of MMC1.

$$\begin{cases} v_{ga1} - R_{g1}i_{f1} = -R_{1}i_{pa1} - L_{1}\frac{di_{pa1}}{dt} - v_{pa1} + R_{dc1}I_{dc1}^{p} + R_{f}i_{f} \\ v_{gb1} - R_{g1}i_{f1} = -R_{1}i_{pb1} - L_{1}\frac{di_{pb1}}{dt} - v_{pb1} + R_{dc1}I_{dc1}^{p} + R_{f}i_{f} \end{cases}$$

(29)

$$v_{gc1} - R_{g1}i_{f1} = -R_{1}i_{pc1} - L_{1}\frac{di_{pc1}}{dt} - v_{pc1} + R_{dc1}I_{dc1}^{p} + R_{f}i_{f}$$

where  $R_{dc1}$ ,  $R_{dc2}$  and  $R_{dc}$  are the resistances of the overhead lines.  $R_{g1}$  and  $R_{g2}$  are the respective grounding resistances at MMC1 and MMC2 sides.  $R_f$  is the fault resistance.  $i_f$  is the fault current at the fault point.  $i_{f1}$  and  $i_{f2}$  are the currents flowing into the neutral point of the interface transformers at MMC1 and MMC2 sides, respectively. The subscript "I" refers to the variables at MMC1 side and the subscript "I" refers to the variables at MMC2 side. Adding up the three equations in (29) results:

$$\sum_{i=a,b,c} v_{pi1} = (3R_{dc1} + R_1)I_{dc1}^p + L_1 \frac{dI_{dc1}^p}{dt} + 3R_{g1}i_{f1} + 3R_f i_f$$

(30)

For the lower arms of MMC1 and MMC2, the following equations can be derived:

$$v_{ga1} - R_{g1}i_{f1} = R_{1}i_{na1} + L_{1}\frac{di_{na1}}{dt} + v_{na1} - R_{dc}I_{dc}^{n}$$

$$-v_{na2} - R_{2}i_{na2} - L_{2}\frac{di_{na2}}{dt} + v_{ga2} - R_{g2}i_{f2}$$

(31)

$$v_{gb1} - R_{g1}i_{f1} = R_1i_{nb1} + L_1\frac{di_{nb1}}{dt} + v_{nb1} - R_{dc}I_{dc}^n$$

$$-v_{nb2} - R_2i_{nb2} - L_2\frac{di_{nb2}}{dt} + v_{gb2} - R_g2i_{f2}$$

(32)

$$v_{gc1} - R_{g1}i_{f1} = R_{1}i_{nc1} + L_{1}\frac{di_{nc1}}{dt} + v_{nc1} - R_{dc}I_{dc}^{n}$$

$$-v_{nc2} - R_{2}i_{nc2} - L_{2}\frac{di_{nc2}}{dt} + v_{gc2} - R_{g2}i_{f2}$$

(33)

Adding up (31)-(33) results,

$$\sum_{i=a,b,c} v_{ni1} - \sum_{i=a,b,c} v_{ni2}$$

$$= (L_1 + L_2) \frac{dI_{dc}^n}{dt} + (3R_{dc} + R_1 + R_2) I_{dc}^n + 3R_{g2} i_{f2} - 3R_{g1} i_{f1}$$

(34)

Recalling (12) and neglecting the line resistance, (30) and (34) can be re-written as

$$\frac{3V_{armden}}{2}M_{de1}^{p} - R_{1}I_{de1}^{p} - L_{1}\frac{dI_{de1}^{p}}{dt} = 3R_{g1}i_{f1} + 3R_{f}i_{f}$$

(35)

$$\frac{3V_{armdcn}}{2} \left( M_{dc2}^{n} - M_{dc1}^{n} \right) = (L_{1} + L_{2}) \frac{dI_{dc}^{n}}{dt} + (R_{1} + R_{2}) I_{dc}^{n} + 3R_{g2} i_{f2} - 3R_{g1} i_{f1}$$

(36)

Combining (35)-(36) and (14), it can be seen that the grounding resistance provides the path for fault current and affects the dynamic response of the DC current control loop.

Fig. 4. Circuit diagram of a two-terminal VSC-HVDC based on hybrid MMC.

If the fault currents  $i_{fl}$  and  $i_{fl}$  are not controlled, there will be DC current flowing through the grounding devices of the interface transformers, which could bring magnetic saturation at the transformer windings and continuous heat of the grounding resistance. Thus, such current path needs to be avoided. To eliminate the fault current path for the fault currents, according to KCL, the DC current of the faulted pole  $(I_{dc}^p, I_{dc2}^p)$  needs to be controlled to be the same as the current  $I_{dc}^n$  at the un-faulted pole. For the un-faulted pole, since it is desirable to transmit half of the rated power,  $I_{dc}^n$  should be controlled at the pre-fault value.

Referring to Fig. 2, the flags  $F_P(F_N)$  are used to configure

the outer of the DC control loops.  $F_P$ =I corresponds to DC power control or DC voltage control whereas  $F_P$ =II corresponds to PTG DC fault ride through control. During a pole-to-ground DC fault, the DC current order of the faulted pole is set to be the same as the measured current of the un-faulted pole so that no steady-state fault current will flow through the fault point and the grounding resistance at the interface transformer.

#### V.SIMULATION VALIDATIONS

#### A. The Test System

In order to verify the efficacy of the proposed controller, a

201-level two-terminal hybrid MMC-HVDC system shown in Fig. 4 is simulated in PSCAD/EMTDC. The number of FBSM per arm is 100 while the number of HBSM per arm is also 100. The simulation parameters are listed in Table 1.

The 120km overhead line is modelled using the frequency dependent model provided by PSCAD. MMC1 controls the DC pole voltages and MMC2 controls the transferred active power. To test the performance of the proposed controller, a relatively small DC limiting inductance of 50mH is used [23]. This independent pole control method is also applicable to HVDC using star reactor with resistance grounding configuration.

Table 1 Parameters of the simulated system

| Parameters                                      | Nominal value |

|-------------------------------------------------|---------------|

| MMC nominal power $S_n$                         | 1000MW        |

| Rated DC pole voltage                           | ±320 kV       |

| Rated DC arm voltage $V_{armdcn}$ ( $V_{dcn}$ ) | 640kV         |

| AC system nominal voltage                       | 400 kV        |

| Short circuit ratio (SCR)                       | 4.0           |

| X/R ratio                                       | 10.0          |

| Interface Transformer                           | 400kV/352kV   |

| Grounding Resistance $R_g$                      | 5000Ω [22]    |

| Capacitance of each SM                          | 10mF          |

| Arm inductance L                                | 0.07H         |

| Arm resistance R                                | 3Ω            |

| Rated capacitor voltage of each SM              | 3.2 kV        |

## B. Verification of Monopole Reduced DC Voltage Operation

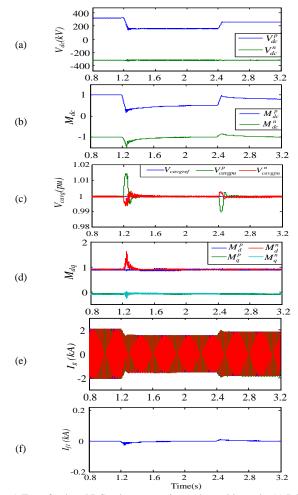

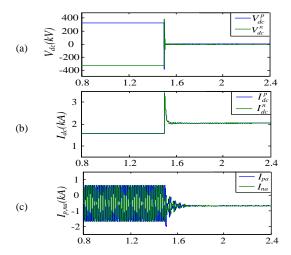

To verify the independent pole control, the DC voltage order of the positive pole is set to be 0.5pu (160kV) during 1.3-2.4s and 0.8pu (256kV) during 2.5-3.2s (the pu unit is relative to  $V_{dcn}/2$  of 320kV). The simulation results are shown in Fig. 5.

Fig. 5(a) shows the DC pole voltages of MMC1. As can be seen, the DC voltage of positive pole is well controlled at 160 kV during 1.3-2.4s and 256 kV during 2.5-3.2s. Whereas the negative pole voltage is controlled at the rated -320 kV during the entire process.

Fig. 5(b) shows the DC modulation indices generated by the upper and lower DC current control loops.  $M_{dc}^p$  is controlled at 0.5 under steady state during 1.3-2.4s and at 0.8 during 2.5-3.2s, whereas  $M_{dc}^n$  is controlled at -1 under steady state. Figs. 5(a)-(b) validates the effectiveness of the two DC control loops.

Fig. 5 (c) shows the average capacitor voltages. At 1.2s and 2.4s, the active power is not equally split among the upper and lower arms due to the sudden change of DC pole voltages. As a result, there is divergence between the average capacitor voltages in the upper and lower arms. However, they are well controlled at 1 pu under steady state.

Fig. 5(d) shows the AC modulation indices generated by the upper and lower AC current control loops. Despite some transients at 1.2s, they are well controlled by the two AC control loops. Fig. 5(e)-(f) shows the output AC current and current flowing through  $R_{gl}$  at MMC1 side. Although the DC voltages of the positive and negative pole are asymmetrical, no DC bias current is observed.

Fig. 5. Test of reduced DC voltage operation at the positive pole. (a) DC pole voltages. (b) DC modulation indices. (c) Average capacitor voltages of upper and lower arms. (d) AC modulation indices. (e) Output AC current. (f) Current flowing through  $R_{gl}$ .

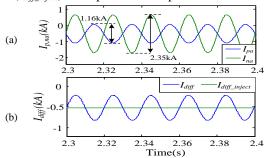

To verify the efficacy of the proposed CCSC, the zoomed waveforms of the arm and circulating currents during 2.3-2.4s  $(V_{dc}^p=160kV, V_{dc}^n=-320kV)$  are shown in Fig. 6.

Fig. 6(a) shows that the peak-to-peak value of the fundamental frequency component in the lower arm current (2.35kA) is almost 2 times larger than the one in the upper arm current (1.16kA), which verifies the analysis in (7). The circulating current  $I_{diff}$  shown in Fig. 6(b) is calculated as the common mode current of the upper and lower arm currents. It can be seen that there are a DC component and a fundamental frequency component existing in  $I_{diff}$ . After adopting the current injection method as outlined in (23), the circulating current  $(I_{diff\_inject})$  has a pure DC component.

Fig. 6. Verification of CCSC based on current injection method. (a) Upper and lower arm currents of phase a. (b) Circulating currents.

# C. Verification of Operating Region of DC Voltage

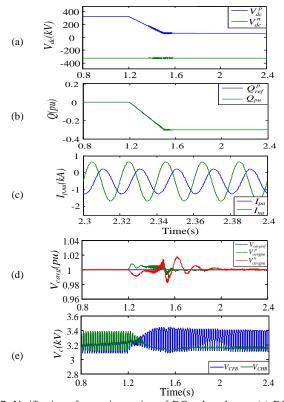

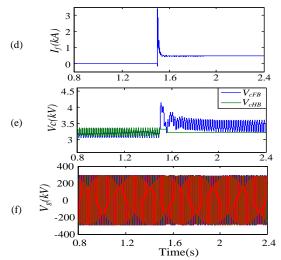

To verify the operating region of the DC pole voltage, the DC voltage order of the positive pole is ramped down from 1pu to 0.2pu during 1.2-1.5s. At the same time, the reactive power order of the positive pole is gradually decreased from 0 to -0.25 pu (relative to  $S_n$ ). The simulations results are shown in Fig. 7.

Fig. 7(a) shows that the DC positive and negative pole voltages can be operated stably at 64 kV and -320 kV respectively, while providing reactive power as shown in Fig. 7(b). The upper and lower arm currents shown in Fig. 7(c) have both positive and negative values to ensure successful SM capacitor voltage balancing. This can be further noticed in Fig. 7(d) where the average capacitor voltages of the upper and lower arms are all well controlled at 1pu, and the well balanced average capacitor voltages of the FBSMs and HBSMs on the upper arm of phase a are shown in Fig. 7(e).  $V_{cFB}$  and  $V_{cHB}$  are the average capacitor voltages of the N/2 FBSMs and the N/2 HBSMs on the upper arm of phase a, respectively.

Fig. 7 validates the analysis in section III.D and Fig. 3, where 0.5 (in pu relative to  $0.5S_n$ ) reactive power should be provided to enable operation under 0.2pu DC positive pole voltage.

Fig. 7. Verification of operating region of DC pole voltages. (a) DC pole voltages. (b) Order and measured value of reactive power. (c) Upper and lower arm currents of phase a. (d) Average capacitor voltages of upper and lower arms. (e) Average capacitor voltages of FBSMs and HBSMs on the upper arm of phase a.

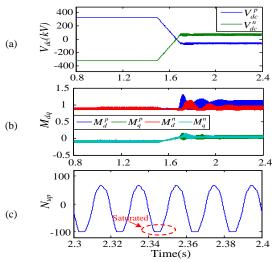

To verify the performance under minimum DC pole voltage, the DC voltage is ramped down from 640kV to -64kV ( $-0.1V_{den}$ )

during 1.5-1.7s, and the simulations results are shown in Fig. 8

Fig. 8(a) shows that the DC positive and negative pole voltages can remain stable at -32kV and 32kV respectively. Figs. 8(b)-(c) show the DC and AC modulation indices respectively, and they are well controlled by the DC and AC control loops. Both the upper and lower arm currents have negative value only as shown in Fig. 8(d). Since the HBSMs cannot be balanced with unipolar arm current, all HBSMs should be bypassed.

Fig. 8(e) shows the inserted SM number calculated by NLM (nearest level modulation). It can be seen that the minimum number is -100, i.e. all the FBSMs on each arm are negatively inserted. Fig. 8(f) shows the average capacitor voltages of the HBSMs and FBSMs on the upper arm of phase a. Since the HBSMs are bypassed, their average capacitor voltage on the upper arm of phase a ( $V_{CHB}$ ) stays unchanged.

Fig. 8. Test of the hybrid MMC under DC voltage of  $-0.1V_{den}$ . (a) DC pole voltages. (b) DC modulation indices. (c) AC modulation indices. (d) Upper and lower arm currents of phase a. (e) Number of inserted SM on upper arm of phase a. (f) Average capacitor voltages of FBSMs and HBSMs on the upper arm of phase a.

To further verify the performance, the DC voltage is reduced from 640kV to -128kV ( $-0.2V_{dcn}$ ) at 1.5s. The simulations results are shown in Fig. 9. From Figs. 9(a) and (b), it can be seen that the DC voltage and AC current controllers

become saturated. This is further evidenced from the inserted SM number shown in Fig. 9(c), as the output of NLM is saturated at -100.

Fig. 9. Test of the hybrid MMC under DC voltage of  $-0.2V_{den}$ . (a) DC pole voltages. (b) AC modulation indices. (c) Number of inserted SM on upper arm of phase a.

### D.Response to Pole to Pole DC Fault

To test the natural response of the proposed controller during pole to pole DC faults, a permanent pole to pole fault is applied at 1.5s. The fault point is 20km away from the DC terminal of MMC1.

Figs. 10(a) and (b) show the DC voltages and currents of both poles. Since the inner DC current reference is saturated at the upper limit  $I_{dclim}$  (1.3pu in this paper), the DC pole currents are controlled at 2.02kA. Figs. 10(c) and (d) show the arm currents and the fault current, and it can be seen that the arm currents are well limited with no over-current during the fault.

Fig. 10(e) shows the average capacitor voltages of the HBSMs and FBSMs on the upper arm of phase *a*. They largely remain balanced around the rated value except the initial over-voltage for the FBSMs during the fault due to the sudden loss of transmission power. Fig. 10(f) shows that the output AC voltage at MMC1 side has no DC bias.

Fig. 10. Test of the hybrid MMC under pole to pole DC fault. (a) DC pole voltages. (b) DC pole currents. (c) Arm currents. (d) Fault current. (e) Average capacitor voltages of FBSMs and HBSMs. (f) Output AC voltage.

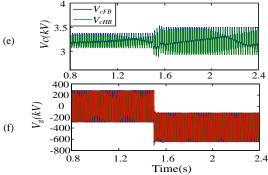

# E. Response to Pole to Ground DC Fault without Fault Ride Through Control

Figs. 11(a)-(f) show the natural response to pole to ground DC fault where a permanent PTG DC fault is applied at the positive pole at 1.5s. Figs. 11(a) and (b) show the DC voltages and currents of both poles. As can be seen, at the instant of DC fault, the DC voltage of negative pole is decreased to be nearly -620kV due to the discharge of transmission line capacitors.

The arm currents and fault current shown in Figs. 11(c) and (d) indicate that they are still within the safe range during transients. Fig. 11(e) shows the average capacitor voltages of the HBSMs and FBSMs on the upper arm of phase a, and they are well balanced. Fig. 11(f) shows the output AC voltage at MMC1 side. Since the fault current flows through the grounding resistance of the interface transformer, a DC bias of -380kV is observed which increases the cost of insulation of the interface transformers.

Fig. 11. Test of the hybrid MMC under pole to ground DC fault without fault ride through control. (a) DC pole voltages. (b) DC pole currents. (c) Arm currents. (d) Fault current. (e) Average capacitor voltages of FBSMs and HBSMs. (f) Output AC voltage.

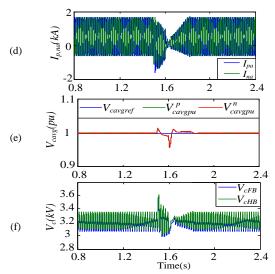

# F. Response to Pole to Ground DC Fault with Fault Ride Through Control

Figs. 12s (a)-(f) show the response to a permanent PTG DC fault applied at 1.5s using the proposed fault ride through control.

Figs. 12(a) and (b) show the DC voltages and currents of both poles. As can be seen, the DC current of the positive pole is controlled to be the same as the un-faulted pole. Therefore, the fault currents  $i_f$  and  $i_{fl}$  can be effectively eliminated, as shown in Figs. 12(c) and (d). Fig. 12(e) shows that the arm currents are still within the safe range during transients. Fig. 12(f) shows the average capacitor voltages of the HBSMs and FBSMs on the upper arm of phase a, and they are well balanced. Fig. 12 (g) shows the output AC voltage at MMC1 side. Since the fault current flowing through the grounding resistance of the interface transformer is eliminated, the DC bias voltage decreases to zero quickly.

Fig. 12. Test of the hybrid MMC under pole to ground DC fault with fault ride through control. (a) DC pole voltages. (b) DC pole currents. (c) Fault current. (d) Current flowing through  $R_{gl}$ . (e) Arm currents. (f) Average capacitor voltages of FBSMs and HBSMs. (g) Output AC voltage.

# G.Response to Three-phase AC Fault

Figs. 13(a)-(f) show the response to a three-phase AC short circuit fault. The temporary AC fault is applied at 1.5s at MMC2 side and lasts for 0.1s. On detecting the AC fault, the order of the active power reference is decreased to zero.

Fig. 13 (a) shows the AC voltage of AC grid 2, and Fig. 13 (b) shows the DC voltages of both poles. Because of the AC fault, the surplus power temporarily increases the DC pole voltages. The DC pole currents and arm currents shown in Figs. 13 (c)-(d) indicate that there is no over-current during the AC fault. The average capacitor voltages of the upper and lower arms as shown in Fig. 13 (e), are all well controlled at 1pu, and the well balanced average capacitor voltages of the FBSMs and HBSMs on the upper arm of phase *a* are shown in Fig. 13 (f).

Fig. 13. Test of the hybrid MMC under AC fault. (a) AC voltage of AC grid 2. (b) DC pole voltages. (c) DC pole currents. (d) Arm currents. (e) Average capacitor voltages of upper and lower arms. (f) Average capacitor voltages of FBSMs and HBSMs on the upper arm of phase a.

#### VI. CONCLUSION

In this paper, an enhanced independent pole control is proposed for hybrid MMC operating under asymmetric DC pole voltages. Six modulation indices including DC modulation indices  $(M_{dc}^p, M_{dc}^n)$  and AC modulation indices  $(M_d^p, M_{dc}^n)$  $M_a^p$ ,  $M_d^n$ ,  $M_a^n$ ) are generated to separately control the upper and lower arms.

With this enhanced independent pole control, the following attributes can be achieved. 1) The hybrid MMC is able to continuously operate under asymmetrical DC pole voltages without bringing DC bias at the neutral point of the interface transformer. 2) the DC voltage region of the hybrid MMC can be significantly extended, where a hybrid MMC based on half FBSM and half HBSM is able to operate within -0.1~1pu DC voltage range. Thus, the hybrid MMC has the ability to actively extinguish the fault arc like the LCC-HVDC system. 3) In case of PTG DC faults, the fault ride through control can effectively eliminate the fault current and the hybrid MMC is able to continuously operate at half of the rated power capacity. No DC bias voltage or current is present at the neutral point of the interface transformers during post-fault steady state.

The proposed control scheme enables a monopole symmetrical hybrid MMC-HVDC system to behave like a bi-pole system, thus provides an attractive approach with high robustness and system availability for applications in future HVDC systems.

# REFERENCES

- [1] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review," IEEE Trans. Power Electron., vol.30, no.1, pp.37-53, Jan. 2015.

- A. Nami, L. Jiaqi, F. Dijkhuizen, and et al, "Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities," *IEEE Trans. Power Electron.*, vol.30, no.1, pp.18-36, Jan. 2015.

- [3] J. Qin, M. Saeedifard, A. Rockhill, and R. Zhou, "Hybrid design of modular multilevel converters for HVDC systems based on various sub-module circuits," IEEE Trans. on Power Del., vol. 30, no. 1, pp. 385-394, Feb. 2015.

- R. Li, J. E. Fletcher, L. Xu, D. Holliday, B. W. Williams, "A hybrid modular multilevel converter with novel three-level cells for DC fault blocking capability," IEEE Trans. Power Del., vol.30, no.4, pp. 2017-2026, Aug. 2015.

- [5] G. P. Adam, I. Abdelsalam, J. E. Fletcher, G. Burt, D. Holliday and S. J. Finney, "New Efficient Sub-module for Modular Multilevel Converter for Multi-terminal HVDC Networks," IEEE Trans. Power Electron., vol.32, no.6, pp. 4258-4278, Jun. 2017.

- W. Xiang, W. Lin, T. An, J. Wen, Y. Wu, "Equivalent electromagnetic transient simulation model and fast recovery control of overhead VSC-HVDC based on SB-MMC," IEEE Trans. Power Del., vol.32, no.2, pp. 778-788, Apr. 2017.

- R. Zeng, L. Xu, L. Yao, and B. W. Williams, "Design and operation of a hybrid modular multilevel converter," IEEE Trans. Power Electron., vol. 30, no. 3, pp. 1137-1146, Mar. 2015.

- S. Lu, L. Yuan, K. Li, and Z. Zhao, "An Improved Phase-Shifted Carrier Modulation Scheme for a Hybrid Modular Multilevel Converter," IEEE Trans. Power Electron., vol. 32, no. 1, pp. 81-97, Feb. 2017.

- [9] C. Wang, J. Meng, Y. Wang, "Modified carrier phase-shifted SPWM for a hybrid modular multilevel converter with HBSMs and FBSMs", presented in 8th IEEE International Power Electron. and Motion Control Conf. (IPEMC-ECCE Asia), May. 2016, pp. 1123-1127.

- [10] R. Zeng, L. Xu, L. Yao, and J. Morrow, "Pre-charging and DC Fault Ride-Through of Hybrid MMC Based HVDC Systems," IEEE Trans. Power Del., vol. 30, no. 3, pp. 1298-1306, Jun. 2015.

- [11] W. Lin, D. Jovcic, S. Nguefeu, and H. Saad, "Full Bridge MMC Converter Optimal Design to HVDC Operational Requirements," IEEE Trans. Power Del., vol.31, no.1, pp. 1342 - 1350, Jun. 2016.

- [12] R. Zeng, L. Xu, L. Yao, and S. J. Finney, "Analysis and Control of Modular Multilevel Converters under Asymmetric Arm Impedance Conditions," IEEE Trans. Ind. Electron., vol.63, no.1, pp. 71-81, Jan. 2016.

- [13] R. Yang, B. Li, G. Wang, C. Cecati, S. Zhou, D. G. Xu, and W. Yu, "Asymmetric mode control of MMC to suppress capacitor voltage ripples in low frequency low voltage condition," IEEE Trans. Power Electron., early access, DOI 10.1109/TPEL.2016.2600762.

- [14] H. Wang, G. Tang, Z. He, and J. Yang, "Efficient Grounding for Modular Multilevel HVDC Converters (MMC) on the AC Side," IEEE Trans. Power Del. vol. 29, no. 3, pp. 1262-1272, Jun. 2014.

- [15] A. Junyent-Ferré, P. Clemow, M. M. Merlin, T. C. Green, "Operation of HVDC Modular Multilevel Converters under DC pole imbalances," presented in 16th European Conf. on Power Electron. and Appli., Aug. 2014, pp. 1-10.

- [16] F. Zhang, J. Xu, C. Zhao, "New control strategy of decoupling the AC/DC voltage offset for modular multilevel converter," IET Gener. Transm. Distrib., Vol. 10, Iss. 6, pp. 1382-1392, 2016.

- [17] J. Hu, K. Xu, L. Lin, R. Zeng, "Analysis and enhanced control of hybrid-MMC-based HVDC systems during asymmetrical DC faults," IEEE Trans. Power Del., early access, DOI: 10.1109/ TPWRD.2016.2568240.

- [18] A. Antonopoulos, L. Angquist, and H.-P. Nee, "On dynamics and voltage control of the modular multilevel converter," presented in Proc. 13th Eur. Conf. Power Electron. Appl., 2009, pp. 1-10.

- [19] G. P. Adam and I. E. Davidson, "Robust and generic control of full-bridge modular multilevel converter high-voltage DC transmission systems," IEEE Trans. Power Del., vol. 30, no. 6, pp. 2468-2476, Dec. 2015.

- [20] Q. Tu, Z. Xu, L. Xu, "Reduced switching-frequency modulation and circulating current suppression for modular multilevel converters," IEEE Trans. Power Del., vol. 26, no. 3, pp. 2009-2017, Jul. 2011.

- [21] D. Jovcic and A. Jamshidifar, "Phasor model of modular multilevel converter with circulating current suppression control," IEEE Trans. Power Del., vol. 30, no. 4, pp. 1889-1897, Aug. 2015.

- [22] W. Huang, Y. Lu, X. Li, Y. Huang, S. Xu and et al, "A calculation method for maximum steady-state loss of VSC-HVDC grounding resistor in Luxi back-back HVDC interconnector. 12th IET International Conference on AC and DC Power Transmission (ACDC 2016). May.

- [23] E. Kontos, P. Bauer, "Reactor Design for DC Fault Ride-through in MMC-based Multi-terminal HVDC Grids," IEEE 2nd Annual Southern Power Electron. Conf., Dec. 2016, pp. 1-6.