# Generation, Performance Evaluation and Control Design of Single-phase Buck-boost Differential-mode Current Source Inverters

| Journal:                      | IET Renewable Power Generation                                                                                                                                                                                                   |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manuscript ID:                | RPG-2015-0343                                                                                                                                                                                                                    |

| Manuscript Type:              | Research Paper                                                                                                                                                                                                                   |

| Date Submitted by the Author: | 23-Jul-2015                                                                                                                                                                                                                      |

| Complete List of Authors:     | Darwish, Ahmed; University of Strathclyde, EEE<br>Holliday, Derrick; University of Strathclyde, Electronic and Electrical<br>Engineering<br>Williams, Barry; UNiversity of Strathclyde, Electrical and electronic<br>engineering |

| Keyword:                      | DC-AC POWER CONVERTORS, SWITCHED MODE POWER SUPPLIES,<br>PHOTOVOLTAIC POWER SYSTEMS, RENEWABLE ENERGY SOURCES,<br>POWER ELECTRONICS, VARIABLE STRUCTURE SYSTEMS                                                                  |

SCHOLARONE<sup>™</sup> Manuscripts

# Generation, Performance Evaluation and Control Design of Singlephase Buck-boost Differential-mode Current Source Inverters

Ahmed Darwish<sup>1\*</sup>, Derrick Holliday<sup>1</sup>, Barry Williams<sup>1</sup>

<sup>1</sup>Electrical and Electronic Engineering, University of Strathclyde, Glasgow, UK \*ahmed.mohamed-darwish-badawy@strath.ac.uk

Abstract: Differential-mode inverter topologies are promising for renewable energy generation as they offer merits such as reduced size of passive elements, high power density, and reduced total cost. Single-phase buck-boost differential-mode current source inverters (DMCSI) can provide flexible output voltage above or below the input dc voltage, which is necessary for higher efficiency of modern renewable energy applications. The continuous input current of a DMCSI is appropriate for maximum power point tracking operation (MPPT) of photovoltaic applications. However, the performance and control of such converters has not been discussed in detail. As a drawback, the total dc side input current of a single-phase inverter consists of a desired dc component and an undesirable ac component. This ac current component frequency is double the output voltage frequency and thus, affects MPPT resulting in reduced total losses, maximum ripple current, total harmonic distortion, devices and passive element ratings. In addition, the sliding mode controller's design and possible methods of eliminating the input 2<sup>nd</sup> harmonic current are discussed. A 2.5kW bidirectional inverter is used to validate the design flexibility of the five inverters topologies.

# 1. Introduction

There is mounting international proclivity to reduce the cost and improve the efficiency of energy conversion systems through modular structured renewable/distributed systems [1]. Therefore, the need for reducing converter size and passive component values is pressing. Moreover, the cost of photovoltaic (PV) systems is affected considerably by installation and maintenance costs [2]. The inverter initial and running costs may reach about half the initial PV system cost [3].

Most dc-ac converters installed in PV systems require large input filtering capacitance, typically wet electrolytic types. Replacing this electrolytic capacitor with a plastic type increases reliability significantly as it is at least thirty times more reliable than electrolytic types, at the same operating conditions [4]. At rated operating conditions, the life time of an electrolytic filter capacitor is short compared with other inverter components [5]. Thus, using this capacitor hampers increased overall system reliability. The life time of a capacitor is halved for every 10°C increase in the operating temperature [6].

For dc-ac conversion, the voltage source inverter (VSI) is the most common converter topology where the output ac voltage peak is always lower than the input dc voltage and the output ac current peak is always greater than the input dc current [7, 8]. Because of the VSI buck nature, a boost dc-dc converter may be installed between the PV and the inverters input for voltage matching and maximum power point tracking (MPPT) control. Consequently, system volume, weight, power losses, and cost are increased [9, 10]. Myrzik [11] classified the single-stage buck and boost inverter topologies, while in [12], buck-boost Z-source inverter topologies were proposed and explained.

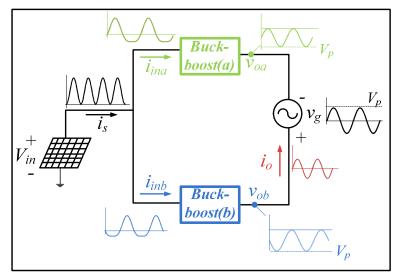

If two power converters are connected in a parallel-series configuration, they form a differential-mode inverter. Some of these differential mode inverters types are shown in [9], [13, 14]. The basic structure of a differential-mode buck-boost single-phase inverter is shown in Fig.1. The differential-mode inverter initially appeared in [13] as a boost inverter, while a differential buck inverter is presented in [15]. Knight et al. [2] proposed the differential six-switch buck-boost inverter based on the Ćuk converter, but its performance was not evaluated.

Of the known two-switch two-diode buck-boost reversible converters, there are five converters that can provide continuous input currents and hence, mitigate the need for large electrolytic input capacitors. These buck-boost converters are shown in [16] as C5, D1, D2, F5 and G5 and can be used as building blocks in a differential-mode current source inverter (DMCSI). Besides eliminating an unreliable large electrolytic capacitor, continuous input current switched mode power supplies (SMPS) enable safe and reliable converter-grid connection and they are attractive solutions for energy conversion systems in terms of: 1) voltage buck-boost operation with a flexible output voltage range, 2) continuous input current, 3) high efficiency, and 4) high frequency transformer coupling possibilities.

Generally, continuous input current converters are time variant systems where the overall transfer function describing the relation between the input and output voltages and currents depend on the switching periods of its switches. This results in a complex stable design because the converter poles and zeros travel through a long Nyquist trajectory [9], [17, 18].

In single-phase inverters, the output power demand reflects into the input side and implies that the input current or voltage, or both, carry a 2<sup>nd</sup> harmonic component [19]. For renewable energy sources, this component would affect MPPT performance and decreases the average power from the system. The conventional solution for the harmonics in the input dc current is to use a large inductor which attenuates the even-order harmonics [20]. However, this is not a practical solution as the inverter produces high dc current which requires a large, bulky input inductor. Research has been conducted into eliminating the oscillating input current of a single-phase PV inverter, and can be classified into two categories: 1) passive elimination with passive circuits and 2) active elimination circuits with semiconductor devices [21]. An example of passive elimination is presented in [22] where a second order LC circuit is used as a notch filter. Although such circuits can reduce the even harmonics from the input side, they have two main drawbacks. Firstly, in time, deviation in the passive element component values results in reduced even harmonic attenuation. Secondly, the capacitor in the PV current path results in a discontinuous current

component which requires another stage of filtering. An active harmonic suppression technique is presented in [23], where the  $2^{nd}$  order harmonic of the input current is eliminated by a series buffer converter topology.

This paper presents the generation of single-phase buck-boost DMCSIs from their building dc-dc blocks, proposes proper control design for each topology, and compares the possible DMCSI topologies in terms of features such as efficiency, input current ripple, output current total harmonic distortion (THD), and device and capacitor ratings. Also the paper presents possible methods for decoupling the 2<sup>nd</sup> order harmonic current components in the proposed DMCSIs with and without extra power electronic switches and discusses their effect on passive element sizes.

Fig.1. Basic structure of a buck-boost DMCSI.

# 2. System description

The input voltage dc source is connected to two bidirectional buck-boost converters as shown in Fig.1. Most buck-boost converters produce an output voltage which has an opposite polarity to the input voltage. Each converter produces unipolar voltage where:

$$v_{oa}(t) = -h_a V_{in}$$

$$h_a = H_{dc} + H_{ac} \sin \omega t$$

$$v_{oa}(t) = -\frac{1}{2} V_p [1 + \sin \omega t]$$

$$v_{ob}(t) = -h_b \cdot V_{in}$$

$$h_b(t) = H_{dc} + H_{ac} \sin(\omega t - \pi)$$

$$v_{ob}(t) = -\frac{1}{2} V_p [1 + \sin(\omega t - \pi)]$$

(1b)

The output voltage  $v_g$  and current  $i_o$  are:

$$v_g(t) = v_{ob} - v_{oa} = V_p \sin \omega t$$

$$i_o(t) = I_o \sin(\omega t + \gamma)$$

(1c)

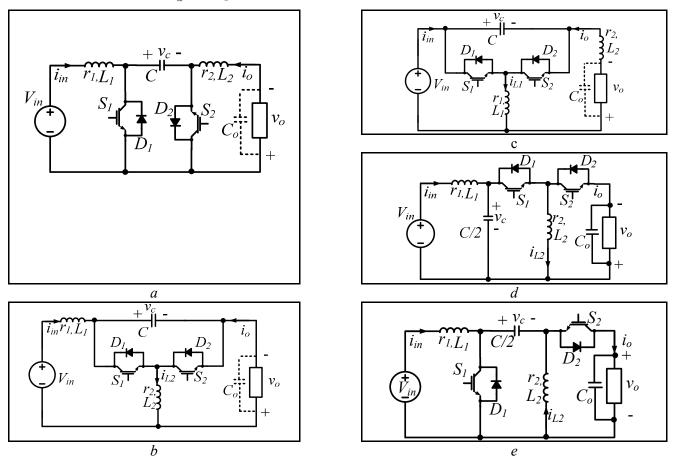

The basic dc-dc converters with continuous input currents are shown in Fig. 2. All are reversible when using two switch-diode pairs. For all these converters, the power is transferred from the input to the output side (or in the opposite direction) through a capacitor C while storing energy in the input and output inductors  $L_1$  and  $L_2$ . For converters C5, D1 and D2, the output shunt capacitor  $C_o$  is optional (converters the output to a voltage source) as the output current is continuous. However,  $C_o$  is mandatory for converters G5 and F5 (in order to average the output voltage). For all the converters, the switch and diode ( $S_1$  and  $D_2$ ) operate alternately when the power is transferred from the input to the output and the switch and diode ( $S_2$  and  $D_1$ ) operate alternately when power is transferred in the opposite direction.  $t_{on}$  is the period when  $S_1$  or  $D_1$  conduct current while  $t_{off}$  is the period where  $S_2$  or  $D_2$  conduct.

Fig. 2. Buck-boost converters with continous input current: (a) C5 ( $\acute{C}uk$ ), (b) D1, (c) D2, (d) F5, and (e) G5 (sepic). The switch on-state duty ratio of the converters  $\delta$  is:

$$\delta = \frac{t_{on}}{t_s} \tag{2a}$$

The voltage conversion ratio between the output and input voltages (h) can be expressed as:

$$h = \frac{v_o}{V_{in}} = \frac{\delta}{1 - \delta} = \frac{i_{in}}{i_o}$$

(2b)

The five buck-boost converters can be inserted into the configuration blocks in Fig.1. The time varying duty ratios of the converters can be deduced from the desired output voltages as:

$$\delta_a(t) = \frac{h_a}{h_a + l} \text{ and } \delta_b(t) = \frac{h_b}{h_b + l}$$

(3)

### 3. Converter performance comparison

In this section, the five single-phase buck-boost DMCSIs are discussed and compared in terms of: 1) overall efficiency, 2) input current ripple, 3) switch and diode currents and voltages, 4) output current THD, and 5) capacitors voltage stresses. To avoid duplication and prolongation, the mathematical analysis for only the C5 ( $\acute{C}uk$ ) converter will be presented in detail while the final conclusions for the remaining four converters will be summarised.

## 3.1. Power Losses

Two significant loss sources will be considered in this analysis. The first is the copper  $(I^2R)$  loss in the input and output inductors and the second is converter semiconductor device losses. Consequently, the root mean square (rms) currents in the inductors as well as the average current in the diodes should be derived. The currents through inductors  $L_1$  and  $L_2$  can be expressed as functions of the output current, voltage and duty ratios as shown in Table 1.

| Topology | Current through $L_1$                    | Current through L <sub>2</sub>      |

|----------|------------------------------------------|-------------------------------------|

| C5       | $i_{in} = \frac{\delta}{1 - \delta} i_o$ | i <sub>o</sub>                      |

| D1       | $i_{in} = \frac{\delta}{1 - \delta} i_o$ | $i_{L2} = \frac{1}{1 - \delta} i_o$ |

| D2       | $i_{L1} = \frac{1}{1 - \delta} i_o$      | $i_{L2} = i_o$                      |

| F5       | $i_{in} = \frac{\delta}{1 - \delta} i_o$ | $i_{L2} = \frac{1}{1 - \delta} i_o$ |

| G5       | $i_{in} = \frac{\delta}{1 - \delta} i_o$ | i <sub>o</sub>                      |

Table 1 Currents through the converter's inductors

$\frac{1}{1-\delta}$  is always greater than 1 while  $\frac{\delta}{1-\delta}$  is greater than 1 when  $\delta > 0.5$  and less than 1 when  $\delta < 0.5$ .

For C5 converters, as an example, the instantaneous input current  $i_{ina}$  and  $i_{inb}$  of each converter is:

$$\frac{i_{ina}(t)}{i_{o}(t)} = \frac{v_{oa}}{V_{in}} = \frac{\delta_{a}}{1 - \delta_{a}}, \quad \frac{i_{inb}(t)}{i_{o}(t)} = \frac{v_{ob}}{V_{in}} = \frac{\delta_{b}}{1 - \delta_{b}}$$

(4a)

$$=\frac{V p^{T} o}{2V} \{\frac{1}{2} \cos \gamma + \frac{1}{2} \cos(2\omega t + \gamma) + \sin(\omega t + \gamma)\}$$

$$i_{inb}(t) = \frac{1}{2} \left[ \frac{V_p}{V_{in}} + \frac{V_p}{V_{in}} \sin(\omega t + \pi) \right] I_o \sin(\omega t + \pi + \gamma)$$

$$= \frac{V_p I_o}{2V_{in}} \left\{ \frac{1}{2} \cos \gamma + \frac{1}{2} \cos(2\omega t + \gamma) + \sin(\omega t + \gamma + \pi) \right\}$$

(4c)

The inputs current  $i_{ina}$  and  $i_{inb}$  are rewritten as:

$$i_{ina}(t) = \overline{I}_{in} + I_{in1}\sin(\omega t + \gamma) + I_{in2}\cos(2\omega t + \gamma)$$

$$i_{inb}(t) = \overline{I}_{in} + I_{in1}\sin(\omega t + \gamma + \pi) + I_{in2}\cos(2\omega t + \gamma)$$

$$\overline{I}_{in} = \frac{1}{4}\frac{V_{p}I_{o}}{V_{in}}\cos\gamma$$

$$I_{in1} = \frac{1}{2}\frac{V_{p}I_{o}}{V_{in}}$$

$$I_{in2} = \frac{1}{4}\frac{V_{p}I_{o}}{V_{in}}$$

(5)

If the parasitic resistances of the inductors ( $L_1$  and  $L_2$ ) are assumed as  $r_1$  and  $r_2$ , the copper losses are:

$$P_{loss\_in} = (\overline{I}_{in}^{2} + \frac{1}{2}I_{in1^{2}} + \frac{1}{2}I_{in2^{2}})r_{1}$$

$$P_{loss\_out} = \frac{1}{2}I_{o}^{2}r_{2}$$

(6)

The power losses through the switches can be approximated as:

$$P_{sw} = V_{DF} \bar{i}_{D} + R_{on} I_{rms}^{2}$$

where

$$I_{rms} \approx \sqrt{\frac{3\delta_{av} I_{o}^{2}}{2}} (\frac{H_{dc}^{2}}{4} + \frac{3H_{ac}^{2}}{16}), \quad \delta_{av} \approx \frac{1.3H_{dc}}{H_{dc} + H_{ac} + 1}$$

$$\bar{i}_{D1} = \frac{I_{in1}}{\pi} - \frac{1}{2} \bar{I}_{in}, \quad \bar{i}_{D2} = \frac{I_{o}}{\pi}$$

(7)

where  $V_{DF}$  is the diode forward threshold voltage and  $R_{on}$  is the device dynamic resistance.

The total power loss of each inverter is:

$$P_{total} = 2[P_{loss in} + P_{loss out} + P_{sw}]$$

(8)

and the inverter efficiency is:

$$\eta = \frac{V_p I_o}{V_p I_o + P_{total}} \times 100 \tag{9}$$

The switches power losses in the five inverter types are the same as they all have identical current and voltage waveforms. The copper losses as well as device average voltage and current are summarized in Table 2.

|           | Copper losses x r                                                 |                                                                   | Switch averages |                                                     |         |                   |

|-----------|-------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------------------------------------|---------|-------------------|

| Туре      | L                                                                 | L <sub>2</sub>                                                    |                 | and D <sub>1</sub>                                  |         | nd D <sub>2</sub> |

|           |                                                                   |                                                                   | Voltage         | Current                                             | Voltage | Current           |

| <i>C5</i> | $\frac{3V_p^2 I_o^2}{1 G V_p^2}$                                  | $\frac{I_o^2}{2}$                                                 | V <sub>in</sub> | $\frac{V_p I_o}{2 - V_o} - \frac{V_p I_o}{2 - V_o}$ | $2V_p$  | $\frac{I_o}{\pi}$ |

|           | $16V_{in}^2$                                                      | _                                                                 |                 | $2\pi V_{in}$ $8V_{in}$                             | π       | π                 |

| <i>G5</i> | $\frac{3V_p^2 I_o^2}{16V_{in}^2}$                                 | $\frac{I_o^2}{2}$                                                 | "               | "                                                   | "       | "                 |

| D1        | $\frac{3V_p^2 I_o^2}{16V_{in}^2}$                                 | $\frac{V_p^2 I_o^2}{8V_{in}^2} + I_o^2 (\frac{V_p}{2V_{in}} + 1)$ | "               | "                                                   | "       | "                 |

| D2        | $\frac{V_p^2 I_o^2}{8V_{in}^2} + I_o^2 (\frac{V_p}{2V_{in}} + 1)$ | $\frac{I_o^2}{2}$                                                 | "               | "                                                   | "       | "                 |

| F5        | $\frac{3V_p^2 I_o^2}{16V_{in}^2}$                                 | $\frac{I_o^2}{2}$                                                 | "               | "                                                   | "       | "                 |

Table 2 Copper losses and switch operating conditions

| Parameter                    | Value                                                     |

|------------------------------|-----------------------------------------------------------|

| Rated power                  | 2.5 kW                                                    |

| Switching frequency          | $f_s = 50 \text{ kHz}$                                    |

| Input inductor               | $L_1 = 1 \mathrm{mH},  r_1 = 80 \mathrm{m\Omega}$         |

| Output inductor              | $L_2 = 1 \mathrm{mH}, \mathrm{r}_2 = 80 \mathrm{m}\Omega$ |

| Input voltage                | $V_{in} = 100 V$                                          |

| Output voltage               | $V_p = 200 V$                                             |

| Output current angle         | $\gamma = 0^{o}$                                          |

| Diode forward voltage        | $V_{DF} = 2V$                                             |

| Transfer capacitor           | $C = 20\mu F$                                             |

| Output capacitor (G5 and F5) | $C_o = 10 \mu F$                                          |

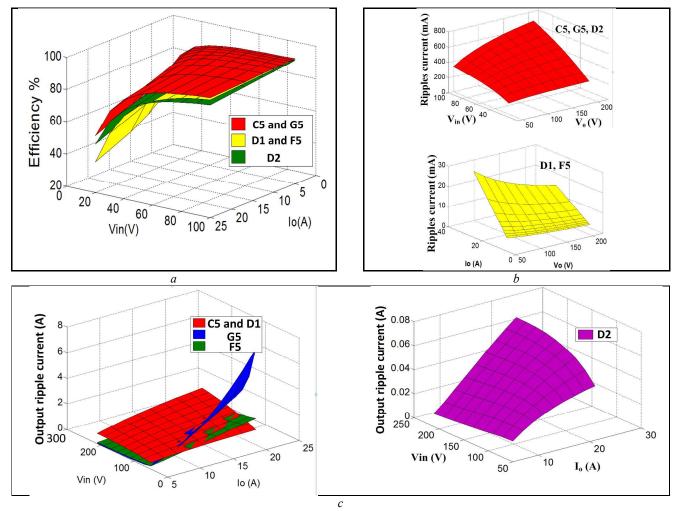

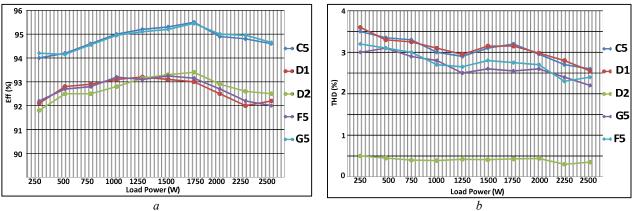

A MATLAB simulation for the efficiencies of the five inverters at different input voltages and output currents with the inverter parasitic values is shown in Fig. 3a. C5 and G5 inverters have the highest efficiency. The efficiencies of D1 and F5 are better than D2 in the high input voltage region while D2 is

better than both when the input voltage is low. Generally, the efficiency of all inverters decreases as the input voltage decreases (since semiconductor voltage drops become more significant).

Fig. 3. MATLAB simulation of DMCSIs: (a) efficiency, (b) input current ripple  $\Delta I_{in}$ , and (c) output current ripple  $\Delta I_o$ 3.2 Input current ripple

Input current ripple is the maximum change of the instantaneous current around its average value. For energy conversion applications like PV, fuel cells, etc., ripple causes harmonics and power loss in the overall system, so should be reduced. Ref [24] demonstrates that input current and voltage ripple inversely affects the total power extracted from PV systems. In the structure in Fig.1, the input current ripple is not constant and changes during the 50/60Hz current cycle. The maximum current ripple occurs at the peak value of the converter's duty ratio. The maximum ripple current for the different inverters are presented in Table 4. Fig. 3b shows plots of maximum ripple currents at different operating conditions. C5, G5 and D2 converters have the same input current ripple versus input and output voltage. Both D1 and F5 have the

same input current ripple versus output current and voltage. As an important advantage, the ripple contents of the input current  $i_{in}$  in D1 and F5 are small compared with the other DMCSIs.

| Topology |                                                                  | normalised                         |

|----------|------------------------------------------------------------------|------------------------------------|

| C5       | $\frac{V_p V_{in} t_s}{L_1 (V_p + V_{in})}$                      | 1                                  |

| D1       | $\frac{V_p V_{in} I_o t_s^2}{4L_1 \mathcal{C} (V_p + V_{in})^2}$ | $\frac{I_o t_s}{4C(V_p + V_{in})}$ |

| D2       | $\frac{V_p V_{in} t_s}{L_1 (V_p + V_{in})}$                      | 1                                  |

| F5       | $\frac{V_p V_{in} I_o t_s^2}{4L_1 C (V_p + V_{in})^2}$           | $\frac{I_o t_s}{4C(V_p + V_{in})}$ |

| G5       | $\frac{V_p V_{in} t_s}{L_1 (V_p + V_{in})}$                      | 1                                  |

Table 4 Maximum Input current ripple

## 3.3 Output current ripple

The output current distortion can be classified into low frequency and high frequency distortion. Low order current distortion appears because of the non-linear nature and high system order of the proposed inverters and can be removed with appropriate control loops as discussed in [9]. The high frequency current and voltage ripple in the output side is because of the switching action. These high frequency ripple components are dependent on the converter topology the differential-inverter descends from. For the same passive element component values, the output current ripple can be expressed as in Table 5. The peak output current ripple  $\Delta I_o$  of the different inverters are simulated in Fig. 3c. The high frequency ripple component of the output current  $I_o$  in D2 is insignificant compared with the other converters, with the same passive element values. This leads the DMCSI emerging from the D2 converter having lower total harmonic distortion (THD) than the other inverters, provided the low order current components are eliminated with proper controllers.

| Topology |                                                        | normalised                            |  |

|----------|--------------------------------------------------------|---------------------------------------|--|

| C5       | $\frac{V_p V_{in} t_s}{L_2 (V_p + V_{in})}$            | 1                                     |  |

| D1       | $\frac{V_p V_{in} t_s}{L_2 (V_p + V_{in})}$            | 1                                     |  |

| D2       | $\frac{V_p V_{in} I_o t_s^2}{4L_2 C (V_p + V_{in})^2}$ | $\frac{I_o t_s}{4C(V_p + V_{in})}$    |  |

| F5       | $\frac{V_{in}I_o^2 t_s}{C_o(V_p + V_{in})V_{in}}$      | $\frac{I_o L_2}{4C_o V_{in}}$         |  |

| G5       | $\frac{V_p {I_o}^2 t_s}{C_o (V_p + V_{in}) V_{in}}$    | $\frac{I_o L_2}{4C_o (V_p + V_{in})}$ |  |

Table 5 Output current ripple

## 3.4 Capacitor C voltage stress

Knowledge of the voltage stresses on the energy transfer capacitor C is important for its selection. For some inverters, the voltage across C consists of a dc-bias plus a sinusoidal voltage component (fundamental) while for other converters, the voltage across C is only dc. Inverters using F5 and G5 have lower capacitor voltages stresses than C5, D1 and D2. Table 6 summarize the capacitor voltages stresses for each converter, in terms of the source voltage and differential sinusoidal output maximum voltage,  $V_p$ .

| Table 6 | Voltage stress | across capacitor | C (see | Fig. 1) |

|---------|----------------|------------------|--------|---------|

|---------|----------------|------------------|--------|---------|

| Topology | dc-bias                   | Sinusoidal voltage (fundamental) | Peak Voltage    |

|----------|---------------------------|----------------------------------|-----------------|

| C5       | $V_{in} + \frac{1}{2}V_p$ | $\frac{1}{2}V_{p}\sin\omega t$   | $V_{in} + V_p$  |

| D1       | $V_{in} + \frac{l}{2}V_p$ | $\frac{1}{2}V_{p}\sin\omega t$   | $V_{in} + V_p$  |

| D2       | $V_{in} + \frac{1}{2}V_p$ | $\frac{1}{2}V_{p} \sin \omega t$ | $V_{in} + V_p$  |

| F5       | V <sub>in</sub>           | ≈0                               | V <sub>in</sub> |

| G5       | V <sub>in</sub>           | ≈0                               | $V_{in}$        |

## 4. Control design

For several applications, buck-boost DMCSIs require robust, efficient and fast control methods. This is because each phase converter produces ac voltage superimposed on a dc bias voltage. Thus, the deviation of the output dc voltage component may cause output dc current components which are undesirable in the inverter systems. Because the proposed systems are of high order, variable structure control [25] (VSR) is an attractive control solution. In this section, sliding mode control (SMC) [25], which belongs to the family of VSR techniques, will be discussed when applied to the proposed DMCSIs. The mathematical

analysis will be presented in detail for the C5 based system and following the same approach, the final block diagrams and control equations will be stated for the other four inverter types. SMC forces the system states to track predefined trajectories which lie on the desired reference values [25]. SMC having fast dynamics and its robustness to system parameter and states variations are important features. The control structure aims to drive the inverter's output current  $i_o$  on a specified surface. First, the large signal average model of C5 converter can be obtained from the converter's differential equations in the *on* and *off* modes as follows (continuous conduction mode (CCM) of all passive reactive components is ensured because the converters are reversible):

*i)*  $S_1 OFF$  and  $S_2 ON$  ( $0 \le t \le t_{off}$ )

$$\frac{di_{in}}{dt} = \frac{1}{L_1} V_{in} - \frac{r_1}{L_1} i_o - \frac{1}{L_1} v_c

= \frac{dv_c}{dt} = \frac{1}{C} i_{in}$$

(10)

$$\frac{di_o}{dt} = -\frac{r_2}{L_2} i_o - \frac{1}{L_2} v_o$$

*ii)*

$$S_1 ON$$

and  $S_2 OFF$  ( $t_{off} < t < t_s$ )

$$\frac{di_{in}}{dt} = \frac{1}{L_I} V_{in} - \frac{r_I}{L_I} i_{in}$$

$$\frac{dv_c}{dt} = \frac{1}{C} i_o$$

(11)

$$\frac{di_o}{dt} = -\frac{1}{L_2} v_c - \frac{r_2}{L_2} i_o - \frac{1}{L_2} v_o$$

The equations can be averaged over the switching time  $t_s$  as:

$$\frac{di_{in}}{dt} = \frac{1}{L_1} V_{in} - \frac{r_1}{L_1} i_{in} - \frac{1 - u}{L_1} v_c

\frac{dv_c}{dt} = \frac{u}{C} i_{in} + \frac{1 - u}{C} i_o

\frac{di_o}{dt} = -\frac{u}{L_2} v_c - \frac{r_2}{L_2} i_o - \frac{1}{L_2} v_o

u = \begin{cases} 1 & S_1 \text{ on} \\ 0 & S_1 \text{ off} \end{cases}$$

(12)

By averaging the discrete variable u on  $t_s$  as  $u_{eq} = \delta$ , the average state space model in the continuous conduction mode CCM is:

$$\begin{bmatrix} \frac{di_{in}}{dt} \\ \frac{dv_c}{dt} \\ \frac{di_o}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{r_I}{L_I} & -\frac{(I-\delta)}{L_I} & 0 \\ \frac{(I-\delta)}{C} & 0 & \frac{\delta}{C} \\ 0 & \frac{\delta}{L_2} & -\frac{r_2}{L_2} \end{bmatrix} \begin{bmatrix} i_{in} \\ v_c \\ i_o \end{bmatrix} + \begin{bmatrix} \frac{I}{L_I} & 0 \\ 0 & 0 \\ 0 & -\frac{I}{L_2} \end{bmatrix} \begin{bmatrix} V_{in} \\ v_o \end{bmatrix}$$

(13)

The C5 converter is not able to be controlled directly from the output current; only the input current can be directly controlled. This can be understood from the effect of the two switches  $S_1$  and  $S_2$  on the converters currents. For all the converters in Fig. 2,  $S_1$  affects the input current  $i_{in}$  directly while  $S_2$  has no direct effect on  $i_o$ . For this reason, the reference value of the converter output current is written in terms of  $i_{in}$ . The sliding surface 'S' can be chosen as:

$$S = \alpha_1 e_1 + \alpha_2 e_2 + \alpha_3 e_3$$

(14a)

$$S = \alpha_1 \dot{e}_1 + \alpha_2 \dot{e}_2 + \alpha_3 \dot{e}_3 = 0 \tag{14b}$$

where  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$  are constants and  $e_1$ ,  $e_2$  and  $e_3$  are the controller error signals, written as:

$$e_{1} = i_{in}^{*} - i_{in}$$

$$e_{2} = i_{o}^{*} - i_{o}$$

$$e_{3} = \int (e_{1} + e_{2})dt$$

(15a)

$$\dot{e}_{1} = \frac{di_{in}^{*}}{dt} - \frac{di_{in}}{dt}$$

$$\dot{e}_{2} = \frac{di_{o}^{*}}{dt} - \frac{di_{o}}{dt}$$

$$\dot{e}_{3} = e_{4} + e_{3}$$

(15b)

For the pre-stated controllability issues, the reference input current  $i_{in}^{*}$  is re-written as:

$$i_{in}^* = K(i_o^* - i_o) \tag{16}$$

where K is a control constant. If the frequency of  $i_o^*$  is assumed small compared to the switching frequency,  $i_o^*$  can be considered constant during one switching period and its derivative can be considered as zero. Substituting (13) and (16) into (15a) yields:

$$\dot{e}_{1} = \frac{-1}{L_{1}} V_{in} + i_{in} \frac{r_{1}}{L_{1}} + v_{c} \left( -\frac{K\delta}{L_{2}} + \frac{(1-\delta)}{L_{1}} \right) + i_{o} \frac{K}{L_{2}} + v_{o} \frac{K}{L_{2}} + v_{o} \frac{K}{L_{2}}$$

$$\dot{e}_{2} = -\frac{\delta}{L_{2}} v_{c} + i_{o} \frac{r_{2}}{L_{2}} + v_{o} \frac{1}{L_{2}}$$

$$\dot{e}_{3} = (K+1) \left( i_{o}^{*} - i_{o} \right) - i_{in}$$

(17)

Substituting (17) into (14a) and solving for  $\delta$  gives:

$$u_{eq} = \delta = \frac{-V_{in} + i_{in}(r_1 - K_1) + v_c + i_o(K_2 r_2) + v_o K_2 + K_3(i^*_o - i_o)}{v_c(1 + K_2)}$$

$$K_1 = \frac{\alpha_3}{\alpha_1} L_1, \quad K_2 = \frac{K\alpha_1 + \alpha_2}{L_2 \alpha_1} L_1, \text{ and } K_3 = \frac{(K+1)\alpha_3}{\alpha_1} L_1$$

(18)

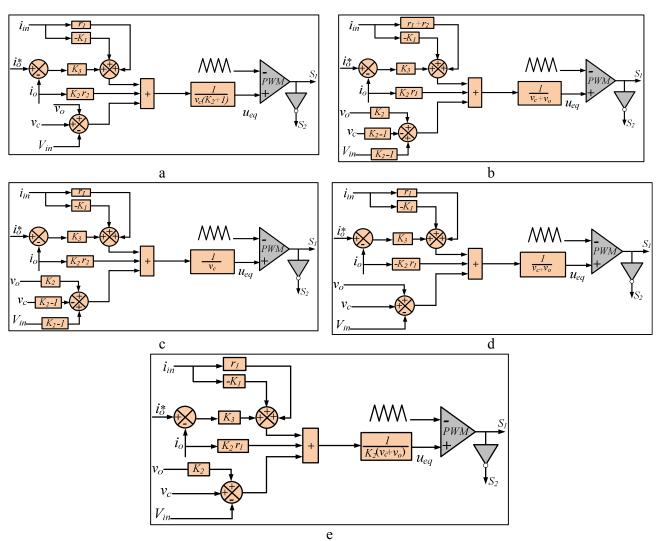

The resultant sliding mode controller from (18) is shown in Error! Reference source not found.a.

The controller gains  $K_1$ ,  $K_2$  and  $K_3$  are responsible for steady state regulation, oscillation and settling time. The designer has three degrees of freedom to choose the gain values. However, it must be confirmed that these values ensure tracking of the predefined trajectory. This is confirmed by fulfilling two existence conditions [26]:

Condition 1(Lyapunov): when S>0 then  $\dot{S}<0$  and u=1

From (18):

$$-V_{in} + i_{in}(r_{in} - K_1) + v_c + i_o(K_2 r_o) + v_o K_2 + K_3(i^*_o - i_o) < v_c(K_2 + 1)$$

(19)

This implies that:

$$-\dot{V}_{in} + r_1 \,\hat{i}_{in} - K_1 \,\dot{i}_{in} - \dot{v}_c \,K_2 + K_2 \,r_2 \,\hat{i}_o + K_2 \,\hat{v}_o + K_3 (i_o^* - i_o) < 0$$

<sup>(20)</sup>

Condition 2: when S < 0 then  $\dot{S} > 0$  and u = 0

From (18):

$$-V_{in} + i_{in}(r_1 - K_1) + v_c + i_o(K_2 r_2) + v_o K_2 + K_3(i_o^* - i_o) > 0$$

(21)

This implies that:

$$-\dot{V}_{in} + r_1 \dot{i}_{in} - K_1 \dot{i}_{in} + \dot{v}_c + K_2 r_2 \dot{i}_o + K_2 \dot{v}_o + K_3 (\dot{i}_o^* - i_o) > 0$$

(22)

Equations (20) and (22) are referred to as existence equations. The sliding mode controllers for the other inverters are similarly obtained. The block diagrams of the other four buck-boost DMCSIs are shown in Fig. 4 while the associated existence equations are listed in Table 7.

## 5. Experimental results

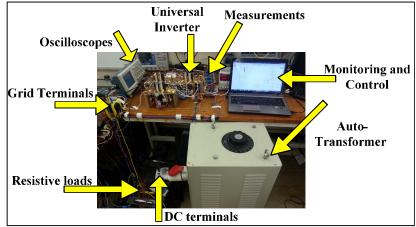

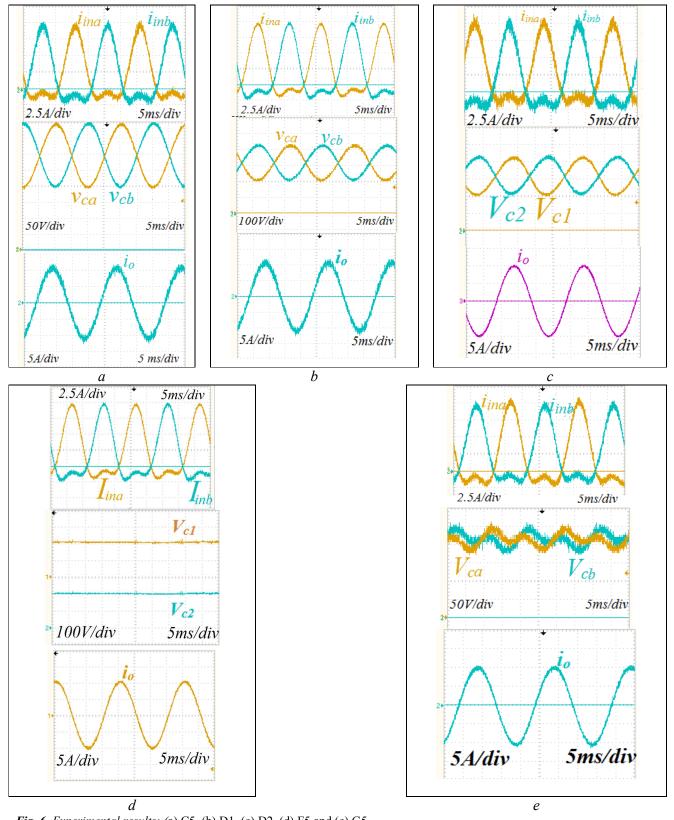

The system concept, presented mathematical analysis, and simulations, are validated with a 2.5kW DMCSI as in Fig.1, with the parameters in Table 3, controlled with TMS320F280335 DSP. Fig. 5 shows the experimental rig, while Fig. 6 shows the experimental results for the presented analysis and discussion for the buck-boost DMCSIs when controlled by sliding mode control and connected to the grid ( $V_p = 200V$ ) at unity power factor ( $\gamma=0$ ). The efficiencies of the five buck-boost DMCSIs at different output power are shown in Fig. 7a. As from the simulation in Fig. 3, the efficiencies of the C5 and G5 are the highest. D1 and F5 have efficiencies higher than D2 for lower output power while D2 has a higher efficiency at higher output power. Fig. 7b shows the THD of the five inverters with respect to output power.

Fig. 4. Block diagrams of DMCSI sliding mode controllers: (a) C5, (b) D1, (c) D2, (d) F5, and (e) G5

Fig. 5. Experimental setup

Table 7 Control and existence equations

|    | $u_{eq} = \delta = \frac{-V_{in} + i_{in}(r_1 - K_1) + v_c + i_o(K_2 r_2) + v_o K_2 + K_3(i_o^* - i_o)}{v_c(1 + K_2)}$                                                                                                                                                                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5 |                                                                                                                                                                                                                                                                                                                          |

|    | $ \hat{V}_{in} + r_1 \hat{i}_{in} - K_1 \hat{i}_{in} - \hat{v}_c K_2 + K_2 r_2 \hat{i}_o + K_2 \hat{v}_o + K_3 (\hat{i}_o^* - \hat{i}_o) < 0 $                                                                                                                                                                           |

|    | $-\hat{V}_{in} + r_1 \dot{i}_{in} - K_1 \dot{i}_{in} + \dot{v}_c + K_2 r_2 \dot{i}_o + K_2 \dot{v}_o + K_3 (\dot{i}_o^* - i_o) > 0$                                                                                                                                                                                      |

|    | $u_{eq} = \frac{V_{in}(K_2 - 1) + i_{in}(r_1 - K_1) - v_c(K_2 - 1) + i_o(K_2 r_2) + v_o K_2 + K_3(i_o^* - i_o)}{V_0 - V_0 - V_0}$                                                                                                                                                                                        |

|    | $v_c$                                                                                                                                                                                                                                                                                                                    |

| D1 | $K_{2} \overset{\vee}{V}_{in} - \overset{\vee}{V}_{in} + r_{1} \overset{\vee}{i}_{in} - K_{1} \overset{\vee}{i}_{in} - K_{2} \overset{\vee}{v_{c}} + \overset{\vee}{v_{c}} + K_{2} r_{2} \overset{\vee}{i}_{o} + K_{2} \overset{\vee}{v_{o}} + K_{3} (i^{*}_{o} - i_{o}) > 0$                                            |

|    | $K_{2}\hat{V}_{in}-\check{V}_{in}+r_{1}\hat{i}_{in}-K_{1}\check{i}_{in}-K_{2}\check{v}_{c}+K_{2}r_{2}\hat{i}_{o}+K_{2}\hat{v}_{o}+K_{3}(i^{*}_{o}-i_{o})<0$                                                                                                                                                              |

|    | $u_{eq} = \frac{V_{in}(K_2 - 1) + i_{in}(r_1 + r_2 - K_1) - v_c(K_2 - 1) + i_o(K_2 r_2) + v_o K_2 + K_3(i_o^* - i_o)}{v_c + v_c}$                                                                                                                                                                                        |

|    | $v_c + v_o$                                                                                                                                                                                                                                                                                                              |

| D2 | $K_{2} \overset{\vee}{V}_{in} - \overset{\vee}{V}_{in} + (r_{1} + r_{2}) \overset{\vee}{i}_{in} - K_{1} \overset{\vee}{i}_{in} - K_{2} \overset{\vee}{v}_{c} + \overset{\vee}{v}_{c} + K_{2} r_{2} \overset{\vee}{i}_{o}) + K_{2} \overset{\vee}{v}_{o} + K_{3} (i^{*}_{o} - i_{o}) > 0$                                 |

|    | $K_{2} \stackrel{\wedge}{V}_{in} - \stackrel{\vee}{V}_{in} + (r_{1} + r_{2}) \stackrel{\wedge}{i}_{in} - K_{1} \stackrel{\vee}{i}_{in} - K_{2} \stackrel{\vee}{v}_{c} + K_{2} \stackrel{\wedge}{r_{2}} \stackrel{\vee}{i}_{o} + K_{2} \stackrel{\wedge}{v}_{o} - \stackrel{\vee}{v}_{o} + K_{3} (i^{*}_{o} - i_{o}) < 0$ |

|    | $u_{eq} = \frac{-V_{in} + i_{in}(r_1 - K_1) + v_c + i_o(K_2 r_2) + v_o K_2 + K_3(i_o^* - i_o)}{K_2(v_c + v_o)}$                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                          |

| F5 | $-\dot{V}_{in} + r_1 i_{in}(min) - K_1 i_{in} + v_c + K_2 r_2 i_o + K_2 v_o + K_3 (i_o^* - i_o) > 0$                                                                                                                                                                                                                     |

|    | $-V_{in} + r_1 \dot{i}_{in} - K_1 \dot{i}_{in} - K_2 \dot{v}_c - \dot{v}_c + K_2 r_2 \dot{i}_o + K_3 (i_o^* - i_o) < 0$                                                                                                                                                                                                  |

|    | $u_{eq} = \frac{-V_{in} + i_{in}(r_1 - K_1) + v_c - i_o(K_2 r_2) + v_o + K_3(i_o^* - i_o)}{1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -$                                                                                                                                                                                      |

| G5 | $v_{eq} = v_c + v_o$                                                                                                                                                                                                                                                                                                     |

|    | $-\hat{V}_{in} + r_1 \dot{i}_{in} - K_1 \dot{i}_{in} + \dot{v}_c - K_2 r_2 \dot{i}_o + \dot{v}_o + K_3 (i_o^* - i_o) > 0$                                                                                                                                                                                                |

|    | $-V_{in} + r_1 \dot{i}_{in} - K_1 \dot{i}_{in} - K_2 r_2 \dot{i}_o + K_3 (i_o^* - i_o) < 0$                                                                                                                                                                                                                              |

D2 has the lowest THD while C5 and D1 have the highest. Both D1 and F5 have the lowest input current ripple. However F5 and G5 require output capacitor  $C_o$ , while the voltage stresses across the intermediate capacitors in F5 and G5 are lower than the stresses in the other inverters. The relationship between the input current ripple and the total efficiency for the PV systems are to be considered in further publications.

Fig. 6. Experimental results: (a) C5, (b) D1, (c) D2, (d) F5 and (e) G5.

Fig. 7. Experimental plots of DMCSIs: (a) efficiency and (b) THD.

## 6. Dc side harmonic filtering

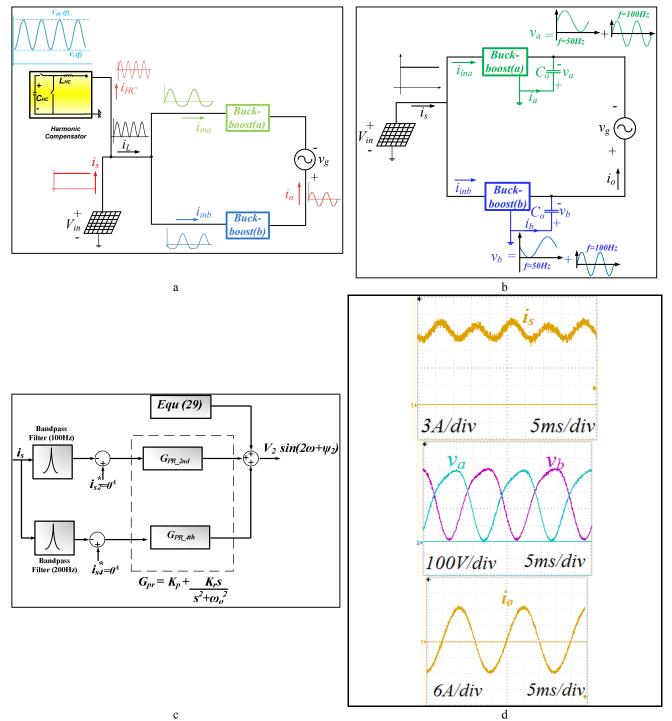

Single-phase inverters draw and deliver oscillating power, with the second-order current harmonic (superimposed on an average dc current) in the dc link (the dc side), independent of the power flow direction. In low power applications, such as small-scale PV systems for micro-grids, filtering is required at the dc side because the harmonic current components will significantly affect PV MPPT. In [21], a two-switch two-diode reversible boost converter can actively eliminate the second order harmonic component from the input of the PV or EV system currents as shown in Fig. 8a and the energy can be stored temporarily in an output capacitor  $C_{HC}$ . However, this harmonic compensator (HC) method requires an additional power electronic converter which adds to the total cost and control complexity.

The instantaneous power equation of the differential buck-boost inverter with an HC can be written as:

$$P_{in}(t) = P_{HC}(t) + P_{o}(t)$$

$$V_{in}I_{s} = i_{HC}(t) V_{in} + v_{g}(t) i_{o}(t)$$

$$I_{s} = \frac{1}{2} \frac{V_{o} I_{o}}{V_{in}}$$

$$i_{HC}(t) = I_{s} - \frac{v_{g}(t) i_{o}(t)}{V_{in}}$$

$$i_{HC} = \frac{1}{2} \frac{V_{p} I_{o}}{V_{in}} \cos 2\omega t$$

$$I_{HC}^{peak} = \frac{1}{2} \frac{V_{p} I_{o}}{V_{in}}$$

(23)

*Fig. 8.*  $2^{nd}$  harmonic elimination of DMCSI: (a) active elimination with additional power electronic converter [21], (b) active elimination without additional power electronic converter, (c) control for the proposed method, and (d) experimental results for C5 DMCSI with the proposed method.

The energy ( $P_{HC} dt$ ) flows from the input side and is stored in the output capacitor  $C_{HC}$  in the +ve half cycle of  $i_{HC}$  and  $v_{HC}(t)$  increases from  $V_{HC}(i)$  to  $V_{HC}(f)$ . In the -ve half cycle of  $i_{HC}$ , the same energy flows from  $C_{HC}$  back to the dc supply leading  $v_{HC}(t)$  to decrease from  $V_{HC}(f)$  to  $V_{HC}(i)$ . This energy cycling can be expressed as:

$$V_{in} \int_{0}^{\frac{1}{2}t_{HC}} i_{HC}(t) dt = \frac{1}{2}C_{HC} [v_{HC}^{2}(f) - v_{HC}^{2}(i)]$$

where  $t_{HC} = \frac{1}{2}f$  and  $v_{HC}(i) = V_{in}$

$v_{HC}^{2}(f) = V_{in}^{2} + \frac{V_{p} I_{o}}{2\pi f C_{HC}}$

$v_{HC}(f) = \sqrt{v_{in}^{2} + \frac{V_{p} I_{o}}{2\pi f C_{HC}}}$  (24)

The proposed single-phase buck-boost DMCSIs have the capability to decouple the  $2^{nd}$  order harmonic current component without additional power electronic devices. From Fig. 8b, an additional controller forces energy oscillating at 100/120 Hz to be stored instantaneously in the output capacitors  $C_o$  (which are necessary for F5 and G5 inverters and optional for C5, D1 and D2 inverters). The controller must ensure that this stored energy does not affect the output voltages and currents. Therefore, two voltages with the same magnitude, phase-shift and 100/120 Hz frequency are superimposed across the output capacitors. Without decoupling the double-frequency power, the output instantaneous power is:

$$p(t) = \underbrace{S \cos \gamma}_{P} \underbrace{-S \cos(2\omega t - \gamma)}_{Q}$$

where  $S = \frac{1}{2}V_{p}I_{o}$

(25)

where Q is the reactive power absorbed by the load

The converter output voltages,  $v_a$  and  $v_b$  shown in Fig. 8b, can be expressed as:

$$v_{a}(t) = \frac{1}{2}V_{p} + \frac{1}{2}V_{p} \sin \omega t + V_{2} \sin(2\omega t + \psi_{2})$$

$$v_{b}(t) = \frac{1}{2}V_{p} + \frac{1}{2}V_{p} \sin(\omega t + \pi) + V_{2} \sin(2\omega t + \psi_{2})$$

(26)

Because they are of same magnitude  $V_2$ , frequency 2f, and phase shift  $\psi_2$ , the second order components in the output voltages  $v_a$  and  $v_b$  do not affect and are not seen by the load voltage  $v_g$  and current  $i_o$ . That is, the second order component is eliminate in the output  $v_a - v_b$ .

For the C5 DMCSI example, the total reactive power stored in the inductors ( $L_1$  and  $L_2$ ) and capacitors (C and  $C_o$ ) in the differential inverter can be written as:

$$Q_{s}(t) = L_{1}\left(\frac{di_{ina}}{dt}i_{ina} + \frac{di_{inb}}{dt}i_{inb}\right) + 2L_{2}\frac{di_{o}}{dt}i_{o} + C\left(\frac{dv_{ca}}{dt}v_{ca} + \frac{dv_{cb}}{dt}v_{cb}\right) + C_{o}\left(\frac{dv_{a}}{dt}v_{a} + \frac{dv_{b}}{dt}v_{b}\right)$$

(27)

To eliminate the 2<sup>nd</sup> order harmonic current supplied from the input dc source, the total stored energy in the inverter should be zero. Equating Q to  $Q_s$  in equations (25) and (27) and solving for  $V_2$  and  $\psi_2$  leads to:

$$\psi_{2} = \tan^{-1} \frac{\omega C_{d} V_{p}^{2}}{4S \cos \gamma}$$

$$V_{2} = \frac{S \cos \gamma}{2 \omega C_{o} V_{p} \cos \psi_{2}}$$

(28)

where  $C_d = C + C_o$

However, eliminating the double frequency oscillating power will generate 4<sup>th</sup> order oscillating power  $Q_{4th}$ :

$$Q_{4th} = 2\omega V_2^2 \sin(4\omega t + 2\psi)$$

<sup>(29)</sup>

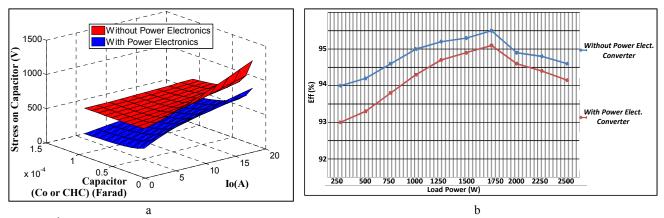

The emerging 4<sup>th</sup> order oscillating power will generate 4<sup>th</sup> order oscillating current in the input side and needs an additional control loop for elimination. In Fig. 8c, a proportional-resonant (PR) controller is implemented in order to ensure suppression of the 2<sup>nd</sup> and 4<sup>th</sup> order harmonics from the input current. As the controller's fast dynamics are not important, the gain values of the PR controller ( $K_p$  and  $K_r$ ) can be selected much lower than the main loop values in order to avoid interaction. Fig. 8d shows the performance of this controller with  $C_o = 150\mu$ F where it removes 75% of the 2<sup>nd</sup> order harmonic component in the input current. Fig. 9a shows the voltage stress across the decoupling capacitors ( $C_{HC}$  and  $C_o$ ) for the two active methods, with and without power electronic devices, at different output current and capacitor values.

*Fig. 9.*  $2^{nd}$  harmonic elimination of DMCSI: (a) voltage stress across the decoupling capacitor ( $C_o$  or  $C_{HC}$ ) for active elimination methods and (b) differential-mode C5 inverter efficiency with  $2^{nd}$  order harmonic currents active elimination techniques.

Using additional power electronics results in lower stress on the capacitor  $C_{HC}$  (lower plane in Fig. 9a) than on  $C_o$  with the second method (upper plane in Fig. 9a). However, Fig. 9b shows that the efficiency of the second method is higher, since device power losses of the additional power electronic converter decrease efficiency.

# 7. Conclusion

The paper investigated single-stage single-phase inverters based on two differentially connected reversible buck-boost converters which have advantages when embedded in renewable energy generation systems. The inverters have a low dc side ripple current, without recourse to electrolytic capacitor filtering. The buck-boost converters have nonlinear high order transfer functions where the dynamics depend on the operation point and the duty ratio, which complicates control design. A 2<sup>nd</sup> order harmonic dc side input current component disturbs MPPT, hence reduces total efficiency. In this paper, five topologies for DMCSIs were proposed. With their operation, features, and control design using sliding mode control were investigated and verified.

The C5 and G5 based inverters have the lowest power loss, hence the highest efficiencies. However, they experience high input current ripple and may require higher input inductors values. The D1 and F5 converters have good efficiency at higher input dc voltages while the efficiency deteriorates at lower input voltages. The efficiency of the D2 inverter is lower than D1 and F5 at high input voltage but is better at lower input voltages. From the devices rating point of view, the five inverters topologies have the same performance. Using the same passive element values, D2 is found to have the lowest THD in the output voltage and current waveforms. D1 and F5 inverters have low input ripple current which is attractive feature for PV systems. F5 and G5 inverters have the lowest capacitor voltage stresses, hence smaller and cheaper capacitors can be used.

A new active method to suppress the  $2^{nd}$  order harmonic input current from the DMCSIs without additional power electronic converters is proposed. The  $2^{nd}$  order reactive power is decoupled using the inverter output capacitors in the ac side. Comparing the proposed technique with a power electronic based active elimination method, the proposed method avoids the power losses associated with an additional power electronic converter, which reduces system efficiency.

An experimental universal single-phase inverter was used to validate the theoretical and mathematical analysis. Detailed overall control analysis, including MPPT operation, as well as the effect of grid side imbalance, common mode voltage, and low order harmonics are yet to be considered.

## 8. References

- [1] Thomson, M., Infield, D.G.: 'Impact of widespread photovoltaics generation on distribution systems', *Renewable Power Generation, IET*, vol.1, no.1, pp.33–40, March 2007

- [2] Knight, J., Shirsavar. S., and Holderbaum, W.: 'An improved reliability Cuk based solar inverter with sliding mode control', *IEEE Transactions on Power Electronics*, vol. 21, pp. 1107-1115, 2006.

- [3] Naik, R., Mohan, N., Rogers, M., and Bulawka, A.: 'A novel grid interface, optimized for utility-scale applications of photovoltaic, wind-electric, and fuel-cell systems', *IEEE Transactions on Power Delivery*, vol. 10, pp. 1920-1926, 1995.

- [4] 'Reliability Prediction for Electronic Equipment', Doc. MIL-HDBK- 217X, Dec. 1991.

- [5] Hongbo, M., Jih-Sheng, L., Quanyuan, F., Wensong, Y., Cong, Z., and Z. Zheng: 'A Novel Valley-Fill SEPIC-Derived Power Supply without Electrolytic Capacitor for LED Lighting Application', *IEEE Transactions on Power Electronics*, vol. 27, pp. 3057-3071, 2012.

- [6] Hui, S., Si, L., Xue Hui, T., Wu, C., and Ng, W.: 'A Novel Passive Offline LED Driver With Long Lifetime' IEEE Transactions on Power Electronics, vol. 25, pp. 2665-2672, 2010.

- [7] Puukko, J., Suntio, T.: 'Dynamic properties of a voltage source inverter-based three-phase inverter in photovoltaic application' *Renewable Power Generation*, *IET*, vol.6, no.6, pp.381,391, November 2012

- [8] Guo, X.Q., Wu, W.Y.: 'Improved current regulation of three-phase grid-connected voltage-source inverters for distributed generation systems' *Renewable Power Generation*, *IET*, vol.4, no.2, pp.101,115, March 2010

- [9] Darwish, A., Holliday, D., Ahmed, S., Massoud, A.M., and Williams, B.W.: 'A Single-Stage Three-Phase Inverter Based on Ćuk Converters for PV Applications' *Emerging and Selected Topics in Power Electronics*, *IEEE Journal of*, vol. 2, pp. 797-807, 2014.

- [10] Kjaer, S.B., Pedersen, J.K., and Blaabjerg, F.: 'A review of single-phase grid-connected inverters for photovoltaic modules' *IEEE Transactions on Industry Applications*, vol. 41, pp. 1292-1306, 2005.

- [11] Myrzik, J.:'Novel inverter topologies for single-phase stand-alone or grid-connected photovoltaic systems' in *Power Electronics and Drive Systems*, 2001. Proceedings., 2001 4th IEEE International Conference on, 2001, pp. 103-108 vol.1.

- [12] Peng, F.Z.: 'Z-source inverter' in *Industry Applications Conference, 2002. 37th IAS Annual Meeting. Conference Record of the, 2002, pp. 775-781 vol.2.*

- [13] Mehrnami, S. and Mazumder, S.K.: 'Discontinuous Modulation Scheme for a Differential-Mode Cuk Inverter' *Power Electronics, IEEE Transactions on*, vol. 30, pp. 1242-1254, 2015.

- [14] Caceres, R.O., Barbi, I.: 'A boost DC-AC converter: analysis, design, and experimentation' *IEEE Transactions on Power Electronics*, vol. 14, pp. 134-141, 1999.

- [15] Daolian, C., Guoling, W.: 'Differential Buck DC-DC Chopper Mode Inverters With High-Frequency Link' IEEE Transactions on Power Electronics, vol. 26, pp. 1444-1451, 2011.

- [16] Williams, B.W.: 'Generation and Analysis of Canonical Switching Cell DC-to-DC Converters' *IEEE Transactions on Industrial Electronics*, vol.61, no.1, pp.329-346, Jan. 2014

- [17] Prasanna, P.R, Rathore, A.K.: 'Analysis, Design, and Experimental Results of a Novel Soft-Switching Snubberless Current-Fed Half-Bridge Front-End Converter-Based PV Inverter'*IEEE Transactions on Power Electronics*, vol. 28, pp. 3219-3230, 2013.

- [18] Middlebrook, R.D, Cuk, S.:'Isolation and multiple output extensions of a new optimum topology switching DC-to-DC converter' in *Power Electronics Specialists Conference, 1978 IEEE*, 1978, pp. 256-264.

- [19] Darwish, A., Abdelsalam, A.K., Massoud, A.M., and Ahmed, S.: 'Single phase grid connected curent source inverter: Mitigation of oscillating power effect on the grid current' in *Renewable Power Generation (RPG 2011), IET Conference on*, 2011, pp. 1-7.

- [20] Dash, P. and Kazerani, K.: 'Dynamic Modeling and Performance Analysis of a Grid-Connected Current-Source Inverter-Based Photovoltaic System' *Sustainable Energy, IEEE Transactions on*, vol. 2, pp. 443-450, 2011.

- [21] Kyritsis, A.C., Papanikolaou, N.P., and Tatakis, E.C.: 'A novel Parallel Active Filter for Current Pulsation Smoothing on single stage grid-connected AC-PV modules' in *Power Electronics and Applications, 2007 European Conference on*, 2007, pp. 1-10.

- [22] Nonaka, S.:'A utility-connected residential PV system adapted a novel single-phase composite PWM voltage source inverter' in *Photovoltaic Energy Conversion, 1994., Conference Record of the Twenty Fourth. IEEE Photovoltaic Specialists Conference 1994, 1994 IEEE First World Conference on,* 1994, pp. 1064-1068 vol.1.

- [23] Ohnuma, Y., Orikawa, K., and Itoh, J.:'A Single-Phase Current-Source PV Inverter With Power Decoupling Capability Using an Active Buffer' *Industry Applications, IEEE Transactions on*, vol. 51, pp. 531-538, 2015.

- [24] A. H. El Khateb, N. Abd.Rahim, J. Selvaraj, and B. W. Williams, "DC-to-DC Converter With Low Input Current Ripple for Maximum Photovoltaic Power Extraction," *Industrial Electronics, IEEE Transactions on*, vol. 62, pp. 2246-2256, 2015.

- [25] V. Utkin, J. Guldner, and J. X. Shi, "Sliding Mode Control in Electromechanical Systems.," *London, U.K.: Taylor and Francis,*, 1999.

- [26] N. Li, "Digital control strategies for DC/DC SEPIC converters towards integration.," INSA de Lyon, 2012.