# Cascaded Commutation Circuit for a Hybrid DC Breaker with Dynamic Control on Fault Current and DC Breaker Voltage

Yunhai Shan<sup>1</sup> Tee C. Lim<sup>2</sup> Stephen J. Finney<sup>3</sup> Weixiao Guang<sup>1</sup>

yunhai.shan@geiri.sgcc.com.cn

Barry W. Williams<sup>3</sup> Derrick Holliday<sup>3</sup> Xiao Ding<sup>1</sup>

barry.williams@strath.ac.uk derrick.holliday@strath.ac.uk dingxiao@geiri.sgcc.com.cn

<sup>1</sup>Global Energy Interconnection Research Institute, Floor 9, Building B, Future Technology Park, Changping District, Beijing 102200, People's Republic of China

<sup>2</sup>Supply Design Ltd, Rosyth Business Centre, 16 Cromarty Campus, Rosyth, Fife, UK

<sup>3</sup>Department of Electronic & Electrical Engineering, Institute for Energy & Environment, University of Strathclyde, Royal College Building,

This paper has not been submitted for journal or conference publication.

#### **ABSTRACT**

This paper proposed a cascaded commutation circuit based on current commutation approach for low-to-medium voltage DC fault current interruption, without snubber circuits, which slows the fault current di/dt prior to current-zero and the rate of rise of the transient recovery voltage dv/dt across the mechanical breaker contacts after current zero. The proposed dynamic control of the fault current di/dt and circuit breaker voltage  $dV_{VCB}/dt$  increase the fault current interruption capability at the first and second current-zeros. Detailed mathematical equations are presented to evaluate the operational waveform profile and the validity of the cascaded commutation principle is confirmed by simulation and experimental results at  $600V_{dc}$ , 110A and 330A.

Keywords: Hybrid DC Breaker, current commutation, current-zero, and fault interruption.

# List of abbreviations

| ABB | Asea Brown Boveri Ltd |

|-----|-----------------------|

| AC  | Alternating current   |

| CBs | Circuit breakers      |

| C   | $Capacitance\ (F)$    |

$C_C$  Commutation capacitance (F)

$C_{C1,2,3}$  Cascaded commutation capacitance (F)

$C_s$  Snubber capacitance (F)  $C_{bank}$  Capacitor bank (F)

di/dt Decline rate of current before current-zero (kA/μs)

dv/dt Rise rate of voltage across the opening contacts immediately

after current-zero (kV/μs)

$dV_{VCB}/dt$  Rise rate of voltage across the VCB immediately after

*current-zero* (kV/μs)

DC Direct current

HVDCHigh voltage direct current $i_{C1/2/3}$ Cascaded counter current (A)

$i_T$  Current through the solid-state switches

n Number of devices  $T_1$ - $T_2$ - $T_3$ - $T_4$ - $T_5$ - $T_6$  Solid-state switches

$T_{C1/2/3/4/5/6}$  Cascaded time intervals (µs)

$V_{C_{C1}}$  Voltage cross the commutation capacitor  $C_{C1}$

$V_{C_{C1.2}}$  Voltage cross the series-connected commutation capacitor

$C_{C1}$  and  $C_{C2}$

$V_{C_{C_{1,2,3}}}$  Voltage cross the series-connected commutation capacitor

$C_{C1}$ ,  $C_{C2}$  and  $C_{C3}$ .

#### I. INTRODUCTION

The necessity of DC breaker topologies in low to medium voltage applications is paramount to the success of developing full DC systems either in localised grid infrastructure [1, 2] or commercial applications in avionics, automotive and telecommunications [3]. Fast interruption time, reliable and successful fault interruption are the main factors that contributes to the system rating of the downstream power electronics. Over de-rating on the power electronics to compromise on slow-switching DC breakers contributes to higher cost and lower efficiency [4]. Arc-flash hazard analysis in low and medium voltage DC systems has been extensively evaluated in [5, 6]. In particular to DC circuit breaker, arcing will occur when current-zero is not achieved during the breaker interruption process [7, 8].

#### (a) Mechanical circuit breaker techniques

DC fault current limitation through helical arc control and mechanical circuit breaker has been proposed in [9] and [10] respectively. Both studies utilise specific design on the mechanical circuit breaker to either control the arc formation [9] or use of Thomson coil [10] to limit and interrupt the fault current. However, the mechanical circuit breaker in [9] need to factor in the large internal blades structure to enhance arc and fault current control. Allowing arc formation can lead to subsequent structure failure and higher maintenance requirement. Although the response time of the mechanical breaker in [10] is lesser than 2ms, the full interruption time that is associated with the coil damping duration are larger than 10ms. This damping duration need to be considered in rapid fault current interruption. The mechanical circuit breaker technique in [11] demonstrated fast interruption time in micro-seconds range. The technique is based on generating a reverse current and an intense axial magnetic field by two helical flux compression generators. Although fast interruption time is achievable, the technique is limited by low probability of successful fault interruption due to single current-zero generation and reliability constraint by the requirement of significant magnetic field.

## (b) Solid-state circuit breaker techniques

Alternate DC circuit breaker approaches that provide rapid fault current interruption has been reviewed in [12-14]. These approaches are based on solid-state circuit breakers which depend on the turning-off of the semiconductors to interrupt DC fault current. Fault current interruption time lesser than 1ms can be achieved and the system structures are normally simple with lesser components count. However, the main limiting factors that incurred with these approaches are the on-state power losses and the cooling requirements that are associated with the semiconductors. Although wide-band gap devices in [15, 16] has been proposed to reduce the

losses and cooling requirements, the semiconductors position on the DC line will need to sustain the DC input voltage and the induced inductive voltage during fault current interruption. High di/dt due to rapid fault current interruption will result in significant induced inductive voltage. The semiconductors will have to be series-connected to sustain these overvoltage and dynamic voltage sharing techniques [17] need to be integrated to prevent device failure.

#### (c) Hybrid circuit breaker techniques

The hybrid DC circuit breaker based on forced commutation principle has been extensively research in HVDC applications [18-21]. The main principle underlying these approaches is to introduce a current-zero to the mechanical circuit breaker before it attempts to interrupt the fault current, thereby reducing the possibility of arcing and decreases the fault current interruption time. Current-zero is achieved either through the series-connected semiconductor device [18] with the mechanical circuit breaker or the forced current commutation from the shunt-connected circuitry across the mechanical circuit breaker [19, 20]. The two stage operation demonstrated in [21] commutated the fault current into the capacitor in a controlled approach to achieve low voltage across the DC breaker during initial contact separation. Although successful fault interruption can be achieved with reduce voltage across the DC breaker as stated in [22], the semiconductors used in [21] need to be rated with respect to the Metal Oxide Varistor (MOV) clamping voltage. MOV is used in the final stage to limit the voltage across the DC breaker, which its clamping voltage can be twice of the DC input source. The fault current interruption time from hybrid DC circuit breaker is dependent on the mechanical circuit breaker opening under arc-less condition. These are generally longer than solid-state circuit breaker techniques and also consists of circuitry with more components count to achieve the current-zero condition. However, in DC applications where fault current interruption time is between the range of 2 to 5ms [23], hybrid DC circuit breaker techniques is preferred as the conduction loss is primarily dependent on the mechanical circuit breaker if forced current commutation circuitry is shunt across the circuit breaker. This is much lower than solid-state DC breaker and the physical disconnection of the current path is more reliable with mechanical circuit breaker. Also, the cooling requirement for the semiconductors are less as they are only operational during the fault condition.

The conditions associated with successful fault current interruption on DC circuit breaker has been evaluated in [22]. A lower fault current di/dt or  $dV_{VCB}/dt$  across the circuit breaker increase the successful interruption probability. This paper enhances the work carried out in [22] and proposed a cascaded forced current commutation circuitry that slows the fault current di/dt prior to current-zero and a low  $dV_{VCB}/dt$  voltage profile across the circuit breaker during the

interruption process. The volume and cost of the proposed commutation circuit can be reduced with recent technological advances in power semiconductors devices [24, 25]. The availability of 6.5kV IGBTs [26] allows lesser cascaded voltage stages and this made the proposed hybrid DC circuit breaker well-suited in low to medium voltage level (1.2kV to 15kV) applications. Applications in high voltage level (>15kV) can still be established with increased cascaded voltage stages or utilizing next generation wide-band gap devices capable in excess of 10kV voltage rating [16, 25, 27, 28]. However, the cost comparisons on the proposed approach with others techniques and devices are not evaluated in this paper. The economic comparison on DC breaker topologies is presented in [29].

This paper focus and evaluate on the approach and technique that allows the control of the fault current di/dt and circuit breaker voltage  $dV_{VCB}/dt$ . The test-rigs involved in the evaluation are presented in [30].

Section II in this paper defines the operating principles of the proposed commutation circuit with associated mathematical equations to confirm the waveform profiles. Section III presents the simulation and experimental results of successful current interruption at 110A and 330A.

# II. Basic principles of the cascaded commutation circuit

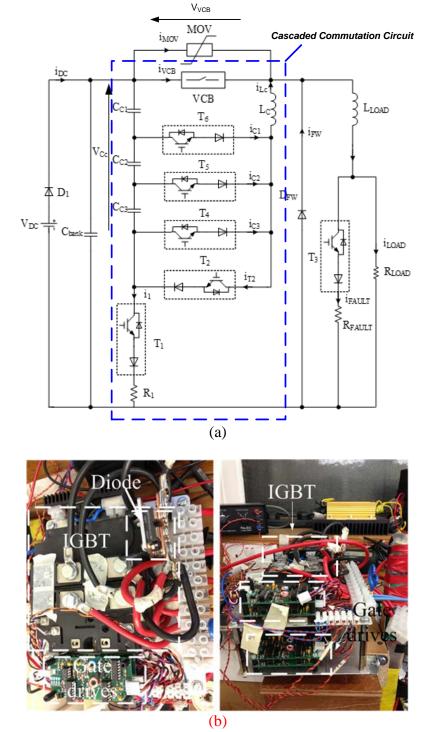

Operation of the proposed cascaded commutation circuit in Fig. 1 involves three sequential processes, namely the preparation (or reset) of commutation circuit, the introduction of fault current, and initiation of the commutation circuit.

Fig. 1: The cascaded commutation circuit of the hybrid breaker; VCB: vacuum circuit breaker and  $T_{1,2,3,4,5,6}$ : series diode and IGBT combination.

- (a) Cascaded commutation circuit diagram

- (b) Pictorial view of the commutation circuit

The circuit consist of series-connected capacitors, such that  $C_{C1} = C_{C2} = C_{C3}$  are in connection with solid-state switches  $T_4$ - $T_5$ - $T_6$ . The proposed circuitry allow n+1 capacitors to be connected in series for higher DC voltage application and/or refined control of the dynamic dV/dt across the VCB. In this paper, three capacitors are series-connected for the circuit analysis and evaluation.

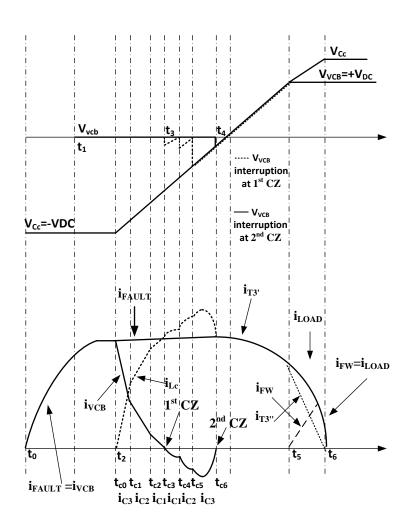

The three solid-state switches are controlled by sequential time intervals, overlapping for a short duration (1µs in this paper) to ensure commutation current continuity, as shown in Fig. 3(H). Under normal load conditions, only the VCB and  $T_1$  are closed, transmitting power to load and to charge the commutation capacitors  $C_{C1} - C_{C2} - C_{C3}$  with an initial voltage totalling  $V_{DC}$ , respectively while the other switches,  $T_2$  to  $T_6$ , are open. A DC fault is emulated by turning on  $T_3$ , so that the energy stored in the capacitor bank  $C_{bank}$  is released through the load inductor  $L_{LOAD}$  into the fault resistor  $R_{FAULT}$ , to produce a high current through the VCB before the electrodes open. For commutation preparation, the commutation capacitors  $C_{C1,2,3}$  are reversed charged by turning on  $T_2$  after receiving the trip signal. Since  $C_{C1} = C_{C2} = C_{C3}$ , the voltage cross each capacitor is equal ( $V_{Cc1} = V_{Cc2} = V_{Cc3}$ ). The fault clearance interruption procedure is shown in Fig. 2. For analysis convenience, the VCB are voltage is ignored, being a low voltage.

#### (i) Time interval, $t_0 - t_{c0}$

At time  $t_1$ , the electrodes started to open introducing an arc voltage across the VCB. When a specific gap distance had been reached, at  $t_2 = t_{c0}$  the solid-state switch  $T_4$  is closed. Then, the resonant counter-current  $i_{L_C} = i_{C3}$  produced by  $L_C C_{C1,2,3}$  rises and forces the current  $i_{VCB} = i_{FAULT}$  through the VCB to decrease. See loop  $C_{C1,2,3} - VCB - L_C - T_4$ .

#### (ii) Time interval, $t_{c0} - t_{c3}$

At  $t_{c1}$ , the counter-current  $i_{L_C}=i_{C2}$  is switched into the loop  $C_{C1,2}-VCB-L_C-T_5$  by turning on switch  $T_5$ , then  $T_4$  off; after obtaining energy from  $L_CC_{C1,2}$  the current continues to rise until  $t_{c2}$ . Then the counter-current transfers into the next loop  $C_{C1}-VCB-L_C-T_6$  as the solid-state switch  $T_6$  is fired and  $T_5$  is turned off, such that  $i_{L_C}=i_{C1}$  is produced by  $L_CC_{C1}$ . When the counter-current reaches the fault current  $i_{FAULT}$  level (after a specifiable commutation time from  $t_{c0}$  to  $t_{c3}$ ), the first VCB current-zero occurs at  $t_{c3}$  and  $i_{FAULT}$  is commutated into the loop  $C_{bank}-C_{C1}-T_6-L_C-L_{LOAD}-T_3-R_{FAULT}$ .

### (iii) Time interval, $t_{c3}$ - $t_{c6}$

Since only capacitor  $C_{C1}$  is operational, the voltage  $V_{VCB}$  across the VCB is forced to equal and track the residual capacitor voltage of  $V_{C_{C1}}$  until voltage  $V_{C_{C1}}$  approaches zero at  $t_{C4}$ . Then  $i_{FAULT}$  switches into the loop  $C_{bank} - C_{C1,2} - T_5 - L_C - L_{LOAD} - T_3 - R_{FAULT}$  by turning on solid-state switch  $T_5$ , then is  $T_6$  turned off.  $V_{VCB}$  tracks the residual voltage of  $V_{C_{C1}}$  plus  $V_{C_{C2}}$  until  $t_{C5}$  when the residual voltage  $V_{C_{C1}} + V_{C_{C2}}$  approaches zero. Then the solid-state switch  $T_4$  is fired and  $T_5$  turned off, and  $i_{FAULT}$  enters the loop  $C_{bank} - C_{C1,2,3} - T_4 - L_C - L_{LOAD} - T_3 - R_{FAULT}$ . The VCB voltage starts to increase following the residual voltage  $V_{C_{C1}} + V_{C_{C2}} + V_{C_{C3}}$ . For a failed interruption at the first current-zero,  $i_{VCB}$  repeats the timing sequence to produce a second current-zero. A second commutation failure is deemed to specify interruption failure.

Fig. 2: Operational sequence waveforms for the cascaded circuit; CZ current-zero crossing in the VCB.

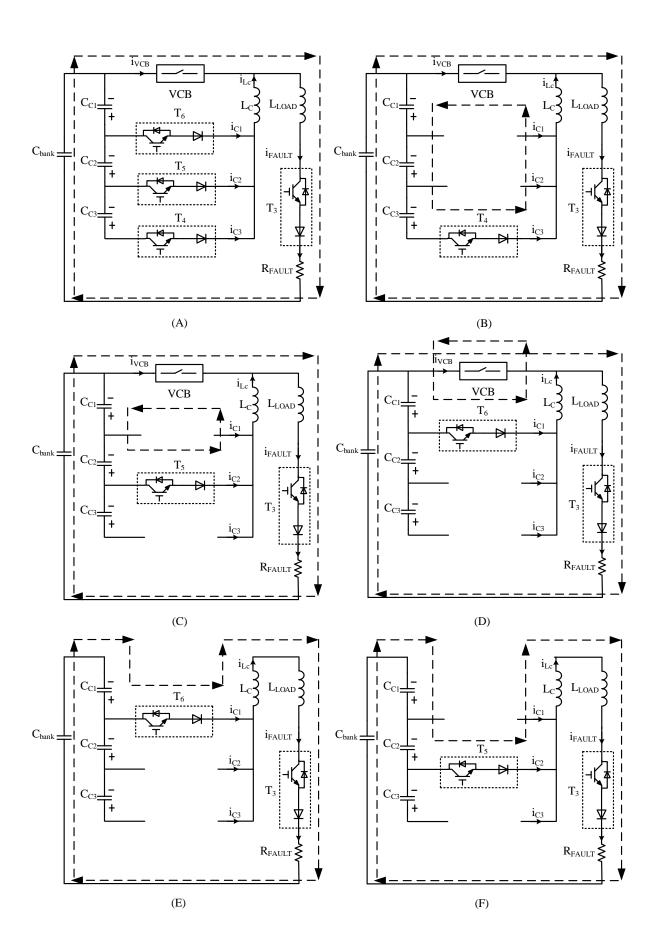

Fig. 3: Interruption sequence of the cascaded commutation circuit.

The mathematical description of the interruption sequences during commutation is based on the timing diagram in Fig. 3. For simplified analysis, the inductors are assumed linear, the voltage drops across all solid-state switches and the VCB state are zero during the on-state; due to large  $C_{bank}$ , its voltage is considered constant, charged to  $V_{DC}$ ; the commutation capacitors have no circuit leakage paths when inactive; and finally, the VCB fault current  $i_{FAULT}$  is unchanged during the commutation process, since the commutation time is shorter than the fault-path time constant. A detailed solution is obtained by solving the differential equations corresponding to each interval; while the end state of one interval is the initial state of the following interval, thereby maintaining continuity between successive intervals.

#### (A) Prior to commutation circuit operation

Fig. 3(A) depicts the cascaded circuit when the VCB fault current has reached its expected value. The VCB electrodes have separated a specific distance. The commutation capacitor  $C_{C1,2,3}$  has been reversed charging, so that the commutation circuit is ready to produce a counter-current through the VCB. In Fig. 3(H), to maintain cascaded commutation circuit continuity, solid-state switches  $T_4$ - $T_5$ - $T_6$  are controlled through a sequence of six intervals with 1µs overlapping (intervals  $T_{C1}$ - $T_{C2}$ - $T_{C3}$ - $T_{C4}$ - $T_{C5}$ - $T_{C6}$ ). Intervals  $T_{C3}$  and  $T_{C4}$  use the same signal. Overlap ensures continuity, that is  $t_{c1} = t_{c1}$ ,  $t_{c2} = t_{c2}$ ,  $t_{c4} = t_{c4}$ ,  $t_{c5} = t_{c5}$ .

## (B) Time interval, $t_{c0} \le t \le t_{c1}$

At time  $t_2 = t_{c0}$ , switch  $T_4$  is turned on to introduce counter-current  $i_{L_C}$  through the VCB, forcing the current  $i_{VCB}$  through the VCB to decrease. The relationships between  $i_{FAULT}$ ,  $i_{VCB}$  and  $i_C$  is:

$$i_{FAULT} = i_{VCB} + i_{L_C} \qquad (A) \tag{1}$$

where  $i_{C_0} = i_{C_0}$  and  $C_{C_1} = C_{C_2} = C_{C_2}$ , thus the current  $i_{C_0}$  through circuit loop  $C_{C_{1,2,3}} - VCB - L_C - T_4$  is defined by:

$$\frac{1}{C_{C1,2,3}} \int i_{C3} dt + L_C \frac{di_{C3}}{dt} = 0 \tag{2}$$

with the initial conditions

$$i_{C3}(t_{c0}) = 0$$

(A) and  $V_{Cc}(t_{c0}) = -V_{DC}$  (V)

which yield:

$$i_{C3}(t) = \frac{V_{DC}}{Z} \sin \omega_0 t \quad (A)$$

and

$$V_{C_{C_{1,2,3}}}(t) = -V_{DC}\cos\omega_0 t \text{ (V)}$$

(4)

$$0 \le \omega_0 t \le \pi$$

(rad)

where  $\omega_0 = 1/\sqrt{L_C C_{C1,2,3}}$  (rad/s)

$$Z = \sqrt{L_C/C_{C1,2,3}} \qquad (\Omega)$$

$$C_{C1,2,3} = \frac{1}{3}C_{C1} = \frac{1}{3}C_{C2} = \frac{1}{3}C_{C3}$$

(F)

At the end of this interval, the voltage across the commutation capacitors  $C_{C1,2,3}$  is  $V_{C_{C1,2,3}} = V_{C_{C1,2,3}}(t_{c1})$ , that is  $V_{C_{C1}} = V_{C_{C2}} = V_{C_{C3}} = \frac{1}{3}V_{C_{C1,2,3}}(t_{c1})$ ; and the commutation current is  $i_C = i_{C3}(t_{c1})$ ; thus the equation describing this interval  $T_{C1}$  is:

$$T_{C1} = t_{c1} - t_{c0} = \frac{-\sin^{-1} \frac{i_{C3}(t_{c1})Z}{V_{DC}}}{\omega_0}$$

(5)

# (C) Time interval, $t_{c1} \le t \le t_{c2}$

$T_5$  is turned on and  $T_4$  off at  $t_{c1}$ , then the commutation current  $i_{L_C}$  diverts into the loop  $C_{C1,2} - VCB - L_C - T_5$ ; thus equalling current  $i_{C2}$  which can be expressed by the differential equation:

$$\frac{1}{C_{C12}} \int i_{C2} dt + L_C \frac{di_{C2}}{dt} = 0 \tag{6}$$

with initial conditions

$$i_{C2}(t_{c1}) = i_{C3}(t_{c1})$$

(A) and  $V_{C_{C1,2}}(t_{c1}) = \frac{2}{3}V_{C_{C1,2,3}}(t_{c1})$  (V)

which yield:

$$i_{C2}(t) = i_{C3}(t_{c1})\cos\omega_{0'}t - \frac{2V_{C_{C1,2,3}}(t_{c1})}{3Z'}\sin\omega_{0'}t \text{ (A)}$$

(7)

and

$$V_{C_{C_{1,2,}}}(t) = Z'^{i_{C_3}}(t_{c_1}) \sin \omega_{0'} t + \frac{2}{3} V_{C_{C_{1,2,3}}}(t_{c_1}) \cos \omega_0 t$$

(8)

$$0 \le \omega_0 t \le \pi$$

(rad)

where  $\omega_{0}$ , =  $1/\sqrt{L_C C_{C1,2}}$  (rad/s)

$$Z' = \sqrt{L_C/C_{C1,2}} \quad (\Omega)$$

$$C_{C1,2} = \frac{1}{2}C_{C1} = \frac{1}{2}C_{C2} = \frac{1}{2}C_{C3}$$

(F)

At the end of this interval, the voltage across the commutation capacitor  $C_{C1,2}$  is  $V_{C_{C1,2}} = V_{C_{C1,2}}(t_{c2})$ , where  $V_{C_{C1}} = V_{C_{C2}} = \frac{1}{2}V_{C_{C1,2}}(t_{c2})$ ,  $V_{C_{C3}} = \frac{1}{3}V_{C_{C1,2,3}}(t_{c1})$ ; and the commutation current is  $i_{L_C} = i_{C2}(t_{c2})$ ; thus the equation for the time of this interval  $T_{C2}$  is:

$$T_{C2} = t_{c2} - t_{c1} = \frac{-\sin^{-1} \frac{v_{C_{C1,2}}(t_{c1}) \times i_{C2}(t_{c2}) + L_C \times i_{C2}(t_{c1}) \times \omega_{0}' \times A}{(C_{C1,2} \times \left(v_{C_{C1,2}}(t_{c1})\right)^2 + L_C \times \left(i_{C2}(t_{c1})\right)^2) \times \omega_{0}'}}{\omega_{0}}$$

where  $A = \sqrt{\frac{C_{C1,2} \times (v_{C_{C1,2}}(t_{c1}))^2 + L_C \times (i_{C2}(t_{c1}))^2 - L_C \times (i_{C2}(t_{c2}))^2}{L_C}}}{L_C}}$  (9)

# (D) Time interval, $t_{c2} \le t \le t_{c3}$

Solid-state switch  $T_6$  is fired and  $T_5$  is turned off at time  $t_{c2}$ , then the commutation current  $i_{L_C}$  enters the loop  $C_{C1} - VCB - L_C - T_6$ . The resulting current  $i_{C1}$  is defined by:

$$\frac{1}{C_{C1}} \int i_{C1} dt + L_C \frac{di_{C1}}{dt} = 0 \tag{10}$$

with the initial conditions

$$i_{C1}(t_{c2}) = i_{C2}(t_{c2})$$

(A) and  $V_{Cc_1}(t_{c2}) = \frac{V_{Cc_{1,2}}(t_{c2})}{2}$  (V)

which yield:

$$i_{C1}(t) = i_{C2}(t_{c2})\cos\omega_{0''}t - \frac{v_{C_{C1,2}}(t_{c2})}{2Z''}\sin\omega_{0''}t \text{ (A)}$$

and

$$V_{C_{C1}}(t) = Z'' i_{C2}(t_{c2}) \sin \omega_{0''} t + \frac{V_{C_{C1,2}}(t_{c2})}{2} \cos \omega_{0''} t$$

(V) (12)

$$0 \le \omega_0 t \le \pi$$

(rad)

where  $\omega_{0"} = 1/\sqrt{L_C C_{C1}}$  (rad/s)

$$Z^{\prime\prime}=\sqrt{L_C/C_{C1}}~(\Omega)$$

$$C_{C1} = C_{C2} = C_{C3}$$

(F)

When the commutation current  $i_{C1}$  rises to equal the fault current, in the commutation period  $t_{c0}$  to  $t_{c3}$ , there is sufficient time for vacuum recovery, having introduced a VCB current-zero. Since the period of each interval has been calculated, it is possible to achieve the first current-zero occurring at time  $t_{c3}$ . This means  $i_{C1}(t_{c3})=i_{FAULT}(t_{c3})$  and the commutation capacitor  $C_{C1}$  voltage is  $V_{Cc_1}=V_{Cc_1}(t_{c3})$ , and the other capacitor voltages are  $V_{Cc_2}=\frac{1}{2}V_{Cc_{1,2}}(t_{c2})$  and  $V_{Cc_3}=\frac{1}{3}V_{Cc_{1,2,3}}(t_{c1})$ . The period of this interval  $T_{C3}$  is:

$$T_{C3} = t_{c3} - t_{c2} = \frac{-\sin^{-1} \frac{V_{C_{C1}}(t_{c1}) \times i_{FAULT}(t_{c3}) + L_{C} \times i_{C1}(t_{c2}) \times \omega_{0}'' \times A'}{(c_{C1} \times \left(V_{C_{C1}}(t_{c2})\right)^{2} + L_{C} \times \left(i_{C1}(t_{c2})\right)^{2}) \times \omega_{0}''}}{\omega_{0}''}$$

where  $A' = \sqrt{\frac{c_{C1} \times (V_{C_{C1}}(t_{c1}))^{2} + L_{C} \times (i_{C1}(t_{c2}))^{2} - L_{C} \times (i_{FAULT}(t_{c3}))^{2}}{L_{C}}}$  (13)

In summary, the commutation current  $i_{L_C}$ , before current-zero, can be described by the piecewise function:

$$i_{C} = \begin{cases} i_{C3}(t)i_{C3}(t) = \frac{V_{DC}}{Z}\sin\omega_{0}t & (t_{c0} \leq t \leq t_{c1}) \\ i_{C2}(t) = i_{C3}(t_{c1})\cos\omega_{0'}t - \frac{2V_{CC_{1,2,3}}(t_{c1})}{3Z'}\sin\omega_{0'}t & (t_{c1} \leq t \leq t_{c2}) \\ i_{C1}(t) = i_{C2}(t_{c2})\cos\omega_{0''}t - \frac{V_{CC_{1,2}}(t_{c2})}{2Z''}\sin\omega_{0''}t & (t_{c2} \leq t \leq t_{c3}) \end{cases}$$

$$(14)$$

### (E) Time interval, $t_{c3} \le t \le t_{c4}$

$i_{FAULT}$  is commutated into the loop  $C_{bank} - C_{C1} - T_6 - L_C - L_{LOAD} - T_3 - R_{FAULT}$ ; but is still equal to  $i_{C1}$  which can be expressed by the differential equation:

$$\frac{1}{C_{C1}} \int i_{C1} dt + L_C \frac{di_{C1}}{dt} + L_{LOAD} \frac{di_{C1}}{dt} + i_{C1} R_{FAULT} = V_{DC}$$

(15)

where the voltage across  $C_{bank}$  can be considered a DC source due to large  $C_{bank}$ , with the initial conditions

$$i_{C1}(t_{c3}) = i_{FAULT}(t_{c3})(A)$$

and  $V_{C_{C1}} = V_{C_{C1}}(t_{c3})$  (V)

Practically  $R_{FAULT} < 2\sqrt{\frac{L_{LOAD}}{C_{C1}}}$ , which yields:

$$i_{C1}(t) = 2K_{1'}e^{-\delta_2 t}\cos(\omega_{3'}t - \theta')$$

(A)

$$V_{C_{C_1}}(t) = \frac{2K_{1\prime}}{C_{C_1}\omega_{4\prime}} \left[\cos(\beta_{2\prime} - \theta') - e^{-\delta_2 t}\cos(\omega_{3\prime} t - \theta' + \beta_{2\prime})\right] + V_{C_{C_1}}(t_{c_3}) \quad (V) \quad (17)$$

where

$$\delta_2 = \frac{R_{FAULT}}{2(L_{LOAD} + L_C)}$$

;  $\omega_{3'}^2 = \frac{1}{(L_{LOAD} + L_C)C_{C1}} - \left(\frac{R_{FAULT}}{2(L_{LOAD} + L_C)}\right)^2$

$$\omega_{4\prime} = \sqrt{{\delta_2}^2 + {\omega_{3\prime}}^2}; \beta_{2\prime} = \tan^{-1} \frac{{\omega_{3\prime}}}{{\delta_2}}$$

$$K_{1,i} = \sqrt{\left(\frac{i_{FAULT}(t_{c3})}{2}\right)^{2} + \left(\frac{\frac{V_{DC} - V_{Cc_{1}}(t_{c3})}{L_{LOAD} + L_{C}} - \delta_{2}i_{FAULT}(t_{c3})}{2\omega_{3},}\right)^{2}}$$

$$\theta' = \tan^{-1}\frac{\frac{V_{DC} - V_{Cc_{1}}(t_{c3})}{L_{LOAD} + L_{C}} - \delta_{2}i_{FAULT}(t_{c3})}{\omega_{3}, i_{FAULT}(t_{c3})}$$

Only capacitor  $C_{C1}$  is introduced into this circuit, the VCB voltage  $V_{VCB}$  is clamped to the residual voltage  $V_{Cc_1}$  until the end of this interval,  $t_{c4}$ .

# (F) Time interval, $t_{c4} \le t \le t_{c5}$

After turning switch  $T_5$  on and  $T_6$  off, the fault current  $i_{FAULT}$  diverts into loop  $C_{bank} - C_{C1,2} - T_5 - L_C - L_{LOAD} - T_3 - R_{FAULT}$ . This means  $i_{C2}$  becomes the continuity energy, and is defined by:

$$\frac{1}{C_{C1,2}} \int i_{C2} dt + L_C \frac{di_{C2}}{dt} + L_{LOAD} \frac{di_{C2}}{dt} + i_{C2} R_{FAULT} = V_{DC}$$

(18)

where the voltage across  $C_{bank}$  can be considered a constant DC source due to large  $C_{bank}$ , with the initial conditions

$$i_{C2}(t_{c4}) = i_{FAULT}(t_{c4})(A)$$

$$V_{C_{C1,2}}(t_{c4}) = V_{C_{C1}}(t_{c4}) + V_{C_{C2}}(t_{c4}) \qquad (V)$$

where  $V_{C_{C2}}(t_{c4}) = \frac{1}{2}V_{C_{C1,2}}(t_{c2})$ , which yields

$$V_{C_{C_{1,2}}}(t_{c4}) = V_{C_{C_1}}(t_{c4}) + \frac{1}{2}V_{C_{C_{1,2}}}(t_{c2})$$

(V)

for  $R_{FAULT} < 2\sqrt{\frac{L_{LOAD}}{C_{C_{1,2}}}}$  , thus:

$$i_{C12}(t) = 2K_{111}e^{-\delta_2 t}\cos(\omega_{3''}t - \theta'') \text{ (A)}$$

(19)

$$V_{C_{C_{1,2}}}(t) = \frac{2K_{1,\prime\prime}}{C_{C_{1,2}}\omega_{4,\prime\prime}} \left[\cos(\beta_{2,\prime\prime} - \theta^{\prime\prime}) - e^{-\delta_2 t}\cos(\omega_{3^{\prime\prime\prime}}t - \theta^{\prime\prime} + \beta_{2\prime\prime})\right]$$

$$+V_{C_{C_{1,2}}}(t_{c4})$$

(V) (20)

where

$$\delta_2 = \frac{R_{FAULT}}{2(L_{LOAD} + L_C)}$$

;  $\omega_{3''}^2 = \frac{1}{(L_{LOAD} + L_C)C_{C1,2}} - \left(\frac{R_{FAULT}}{2(L_{LOAD} + L_C)}\right)^2$

$$\omega_{4''} = \sqrt{\delta_2^2 + \omega_{3''}^2}; \beta_{2''} = \tan^{-1} \frac{\omega_{3''}}{\delta_2}$$

$$K_{1,\prime\prime} = \sqrt{(\frac{i_{FAULT}(t_{c4})}{2})^2 + (\frac{V_{DC} - V_{CC_{1,2}}(t_{c4})}{L_{LOAD} + L_C} - \delta_2 i_{FAULT}(t_{c4})})^2}$$

$$\theta'' = \tan^{-1} \frac{V_{DC} - V_{C_{C1,2}}(t_{c4})}{\frac{L_{LOAD} + L_C}{\omega_{3''} i_{FAULT}(t_{c4})}} - \delta_2 i_{FAULT}(t_{c4})$$

Now,  $V_{VCB}$  tracks the residual voltage  $V_{C_{C1}}$  plus  $V_{C_{C2}}$  until time  $t_{c5}$ .

## (G) Time interval, $t_{c5} \le t \le t_{c6}$

In this interval,  $i_{FAULT}$  enters loop  $C_{bank} - C_{C1,2,3} - T_4 - L_C - L_{LOAD} - T_3 - R_{FAULT}$  by switching the  $T_4$  on and  $T_5$  off. By considering  $C_{C1,2,3}$  as one effective capacitor the topology is the test circuit. The current  $i_{C3}$  for describing the fault current can be expressed by the differential equation:

$$\frac{1}{C_{C123}} \int i_{C3} dt + L_C \frac{di_{C3}}{dt} + L_{LOAD} \frac{di_{C3}}{dt} + i_{C3} R_{FAULT} = V_{DC}$$

(21)

where the voltage across  $C_{bank}$  is considered DC due to large  $C_{bank}$ . with the initial conditions

$$i_{C3}(t_{c5}) = i_{FAULT}(t_{c5})(A)$$

$$V_{C_{C1,2,3}}(t_{c5}) = V_{C_{C1,2}}(t_{c5}) + V_{C_{C3}}(t_{c5}) \text{ (V)}$$

where  $V_{C_{C3}}(t_{c5}) = \frac{1}{3}V_{C_{C1,2,3}}(t_{c1})$ , which yields

$$V_{C_{C1,2,3}}(t_{c5}) = V_{C_{C1,2}}(t_{c5}) + \frac{1}{3}V_{C_{C1,2,3}}(t_{c1})(V)$$

for  $R_{FAULT} < 2\sqrt{\frac{L_{LOAD}}{C_{C1,2,3}}}$ :

$$i_{C3}(t) = 2K_{1m}e^{-\delta_2 t}\cos(\omega_{3}mt - \theta^m) \quad (A)$$

$$V_{C_{C1,2,3}}(t) = \frac{2K_{1m}}{C_{C1,2,3}\omega_{4m}}\cos(\beta_{2m} - \theta^m)$$

$$-\frac{2K_{1m}}{C_{C1,2,3}\omega_{4m}}e^{-\delta_2 t}\cos(\omega_{3mt} - \theta^m + \beta_{2m})] + V_{C_{C1,2,3}}(t_{c5}) \quad (V)$$

where  $\delta_2 = \frac{R_{FAULT}}{2(L_{LOAD} + L_C)}$ ;  $\omega_{3m}^2 = \frac{1}{(L_{LOAD} + L_C)C_{C1,2,3}} - \left(\frac{R_{FAULT}}{2(L_{LOAD} + L_C)}\right)^2$

$$\omega_{4m} = \sqrt{\delta_2^2 + \omega_{3m}^2}$$

;  $\beta_{2m} = \tan^{-1}\frac{\omega_{3m}}{\delta_2}$

$$K_{1m} = \sqrt{(\frac{i_{FAULT}(t_{c5})}{2})^2 + (\frac{V_{DC} - V_{C1,2,3}(t_{c5})}{L_{LOAD} + L_C} - \delta_2 i_{FAULT}(t_{c5})}{2\omega_{3m}}})^2$$

$$\theta''' = \tan^{-1}\frac{V_{DC} - V_{C1,2,3}(t_{c5})}{L_{LOAD} + L_C} - \delta_2 i_{FAULT}(t_{c5})}{2\omega_{3m}}$$

The VCB voltage tracks the residual voltage  $V_{Cc_1} + V_{Cc_2} + V_{Cc_3}$  until interruption finishes. Then the commutation capacitors are reset, ready for the next interruption. The VCB voltage is dominated by the commutation capacitor voltage, thus it can be expressed by the following piecewise function:

$$V_{CC1} = \begin{cases} V_{C_{C1}}(t) = \frac{2K_{1'}}{C_{C1}\omega_{4'}} [\cos(\beta_{2'} - \theta') - e^{-\delta_{2}t}\cos(\omega_{3'}t - \theta' + \beta_{2'})] + V_{C_{C1}}(t_{c3}) & (t_{c3} \leq t \leq t_{c4}) \\ V_{C_{C1,2}}(t) = \frac{2K_{1''}}{C_{C1,2}\omega_{4''}} [\cos(\beta_{2''} - \theta'') - e^{-\delta_{2}t}\cos(\omega_{3''}t - \theta'' + \beta_{2''})] + V_{C_{C1,2}}(t_{c4}) & (t_{c4} \leq t \leq t_{c5}) \\ V_{C_{C1,2,3}}(t) = \frac{2K_{1'''}}{C_{C1,2,3}\omega_{4'''}} [\cos(\beta_{2'''} - \theta''') - e^{-\delta_{2}t}\cos(\omega_{3'''}t - \theta''' + \beta_{2'''})] + V_{C_{C1,2,3}}(t_{c5}) & (t_{c5} \leq t \leq t_{c6}) \end{cases}$$

$$(23)$$

The fault current also can be represented by a piecewise function:

$$i_{FAULT} = \begin{cases} i_{C1}(t) = 2K_{1'}e^{-\delta_2 t}\cos(\omega_{3'}t - \theta') & (t_{c3} \le t \le t_{c4}) \\ i_{C1,2}(t) = 2K_{1''}e^{-\delta_2 t}\cos(\omega_{3''}t - \theta'') & (t_{c4} \le t \le t_{c5}) \\ i_{C3}(t) = 2K_{1'''}e^{-\delta_2 t}\cos(\omega_{3'''}t - \theta''') & (t_{c5} \le t \le t_{c6}) \end{cases}$$

$$(24)$$

In order to define the time intervals after VCB current zero, the performance of commutation capacitor voltage and current is investigated further. By comparing equations (23) to (24); they are similar expression except the initial conditions, including  $i_{FAULT}$ , commutation capacitance  $C_C$ , and initial capacitor voltage  $V_C$ . Since the fault path has a large time constant compared to the commutation circuit, the fault current  $i_{FAULT}$  can be considered constant during the commutation period.

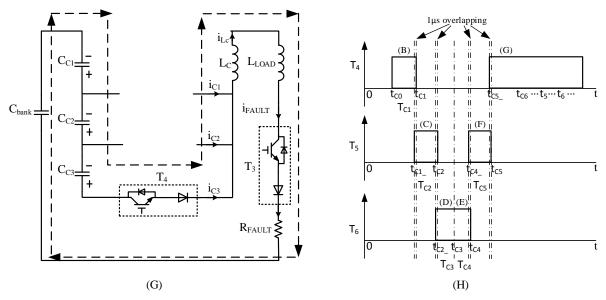

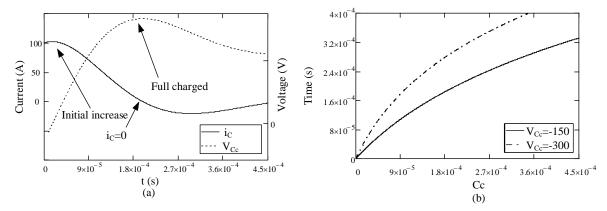

Fig. 4(a) shows the commutation capacitor voltage and current. The current  $i_C$  through the commutation capacitor equals the fault current  $i_{FAULT}$ . Due to the stored magnetic energy transfer and the residual voltage of the commutation capacitor, there is an initial increase in  $i_C$  after the current-zero. Since the solid-state switches offer uni-directional conduction, the commutation capacitor should be fully charged and is kept unchanged when  $i_C$  reduces to zero.

Fig. 4: Commutation capacitor voltage and current profiles.

(a) The performance of commutation capacitor current and voltage after current-zero and

(b) Maximum discharge time with two initial commutation capacitor voltages as a function of commutation capacitance.

$$(I_{FAULT} = 100\text{A}, V_{DC} = 600\text{V}, L_C = 49.4 \mu\text{H}, L_{LOAD} = 1.7 \text{mF}, R_{FAULT} = 6\Omega)$$

The most significant design aspect is the period immediately following the current-zero in the VCB. Thus it is convenience to specify the duration from the initial residual capacitor voltage to when it retains zero charge. Due to the complexity of the commutation capacitor voltage equation, it is difficult to directly define a time interval equation. Capacitor voltage  $V_C$  approaches zero when  $i_C$  increases to its maximum. The approximate equation for the time interval after current-zero is obtained by equating the current differential equation (24) with zero, which gives:

$$T_C = -\frac{\ln(-\frac{e^{2j\theta}(\delta_2 + \omega_3 j)}{\delta_2 - \omega_3 j})j}{2\omega_3}$$

(25)

where  $j = \sqrt{-1}$

Hence

$$T_{C4} = t_{c4} - t_{c3} = -\frac{\ln(-\frac{e^{2j\theta'}(\delta_2 + \omega_3, j)}{\delta_2 - \omega_3, j})j}{2\omega_3, i}$$

(26)

$$T_{C5} = t_{c5} - t_{c4} = -\frac{\ln(-\frac{e^{2j\theta''}(\delta_2 + \omega_3 \eta j)}{\delta_2 - \omega_3 \eta j})j}{2\omega_3 \eta}$$

(27)

The plots in Fig. 4(b) are for equation (26) with two initial residual capacitor voltages. The time interval increases with an increase in commutation capacitance and its initial residual voltage.

Since these time intervals are based on maximum discharge ability for each commutation capacitor voltage, it ensures  $i_{VCB}$  produces second current-zero if interruption failure occurs at the first current-zero.

There are six sequential time intervals,  $T_{CI}$ - $T_{C2}$ - $T_{C3}$ - $T_{C4}$ - $T_{C5}$ - $T_{C6}$ , in the operation cycle of the cascaded commutation circuit.  $T_{C3}$  and  $T_{C4}$  are from the same signal impulse, which triggers switches  $T_3$ - $T_4$ - $T_5$  in the correct sequence. The first three time intervals  $T_{CI}$ - $T_{C2}$ - $T_{C3}$  involve the di/dt reduction while the remainder are for improving the re-applied  $dv_{VCB}/dt$ . Since  $T_{C3}$  and  $T_{C4}$  are derived from the same signal, they can be considered 'joined', linking the reducing current before current-zero and the increasing voltage after current-zero. They maintain continuity during commutation. This means, commutation current  $i_{L_C}$  has to rise to  $i_{FAULT}$  in first two time intervals. Assuming the fault current is commutated into the VCB at the end of the first interval; the interruption process can be expressed as follows:

$$T_{C10} = t_{c1} - t_{c0} = \frac{-\sin^{-1} \frac{i_{FAULT}(t_{c1})Z}{v_{DC}}}{\omega_0}$$

(28)

where

$$\omega_0 = 1/\sqrt{L_C C_{C1,2,3}}$$

(rad/s)

If  $i_{FAULT}$  is commutated at  $t_{c2}$ , equation (9) for describing the time interval  $T_{C2}$  can be rewritten as:

$$T_{C20} = t_{c2} - t_{c1} = \frac{-\sin^{-1} \frac{V_{C_{C1,2}}(t_{c1}) \times i_{FAULT}(t_{c2}) + L_{C} \times i_{FAULT}(t_{c2}) \times \omega_{0'} \times A}{(c_{C1,2} \times \left(V_{C_{C1,2}}(t_{c1})\right)^{2} + L_{C} \times \left(i_{FAULT}(t_{c2})\right)^{2}) \times \omega_{0'}}}{\omega_{0'}}$$

where  $A = \sqrt{\frac{c_{C1,2} \times (V_{C_{C1,2}}(t_{c1}))^{2} + L_{C} \times (i_{FAULT}(t_{c2}))^{2} - L_{C} \times (i_{FAULT}(t_{c2}))^{2}}{L_{C}}}}$

$$V_{C_{C1,2}}(t_{c1}) = -\frac{2}{3}V_{DC}\cos\omega_{0}t_{c1}$$

$$(29)$$

$i_{FAULT}(t_{c1}) = i_{FAULT}(t_{c2})$  due to large time constant of the fault path. Now considering  $t_{c0}$  as a start point,  $T_{c1} = t_{c1} - t_{c0} = t$ , the total duration can be defined as:

$$T_{C1,2} = t_{c2} - t_{c0} = T_{C2} + T_{C1} = T_{C20} + t$$

(30)

To specify the time interval becomes a trade-off between  $T_{C1}$  and  $T_{C2}$ .

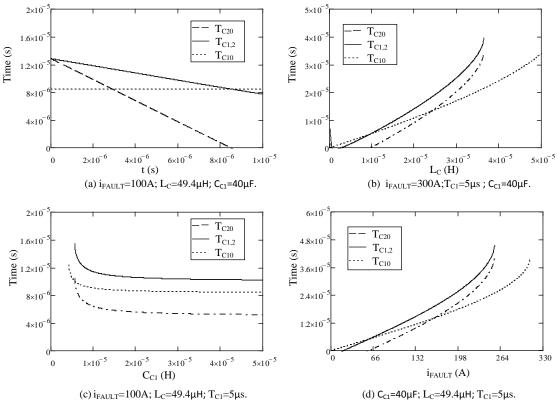

The graphs in Fig. 5 represent equations (29) to (31) for the different conditions but at a fixed 600V DC source. Based on the fixed fault current of 100A and commutation parameters including  $L_C = 49.4 \mu \text{H}$  and  $C_{C1} = 40 \mu \text{F}$ , Fig. 5(a) compares the total duration  $T_{C1,2}$  and second time interval  $T_{C20}$ , as well as the first current-zero time  $T_{C10}$  of the test circuit. It reveals how the di/dt is reduced by the cascaded circuit. The horizontal axis represents the first time interval,  $T_{C1} = t_{C1} - t_{C0} = t$ . The second time interval reduces as the first time interval increases, meaning a longer first time interval will result in less time for the second interval, thereby reducing  $T_{C1,2}$ . To maximise the cascaded circuit commutation time, the second time

interval should dominate commutation until current-zero. This means the switch  $T_5$  turns on before  $T_4$ . However, since there is energy loss during capacitor voltage reversal, it is prudent to initialise the commutation current with maximum energy, then switch into the second path.

Fig. 5: Time interval maximum values as a function of circuit parameters, with a 600V DC source

- (a) First time interval

- (b) Commutation inductance

- (c) Commutation capacitance

- (d) Interruption current

With fixed 300A fault current,  $C_{C1} = 40\mu\text{F}$  and first time interval  $T_{C1} = 5\mu\text{s}$ , Fig. 5(b) shows the relationship between the time intervals and the commutation inductance  $L_C$ . With an increase in  $L_C$  the time intervals are increased. At low inductance, the time intervals have similar values. At higher inductance, the commutation time differences become tens of  $\mu\text{s}$ , which is significant with respect to the VCB, since the vacuum arc has a fast recovery rate [6, 31, 32]. It is not possible for interruption with low inductance, which corresponds to large di/dt. The objective of the cascaded circuit is to increase the interruption probability with relatively small commutation inductance at a short gap distance.

After utilizing a fixed fault current of 100A,  $L_C = 49.4 \mu\text{H}$ , and a first time interval  $T_{C1} = 5 \mu\text{s}$ , Fig. 5(c) shows that the commutation capacitance has little effect on the commutation time thereby does not influence the di/dt.

With a first time interval of  $5\mu$ s and commutation parameters  $L_C = 49.4\mu$ H and  $C_{C1} = 40\mu$ F, the relationship between the time intervals and the fault current is shown in Fig. 5(d). The time intervals display an ever-increasing trend with an increase in the fault current; but are similar at low  $i_{FAULT}$ .

In summary, although there are six time intervals,  $T_{CI}$ - $T_{C2}$ - $T_{C3}$ - $T_{C4}$ - $T_{C5}$ - $T_{C6}$ , in the cascaded circuit, only  $T_{CI}$ - $T_{C2}$ - $T_{C3}$ - $T_{C4}$ - $T_{C5}$  need to be specified because  $T_{C6}$  is a long signal impulse lasting until the end of the interruption.  $T_{C3}$ - $T_{C4}$  are from same signal, thus there are only four signals to be processed. In order to specify these time intervals, the first two intervals should be defined first by utilizing equations (29) and (30). The remaining two can be obtained from equation (26) in terms of different initial conditions.

# III. Simulation and experimental results

The cascaded hybrid circuit was PSPICE simulated with the results post-processed in MATLAB. For comparison convenience, the simulation and experimental results are presented side by side, left and right respectively.

An AC vacuum breaker is used as the circuit breaker in the experiment. The breaker characteristics are shown in Table 1.

Table 1: Technical data on triple-pole vacuum circuit breaker [24].

| Operating voltage, kV     | 1.2               |

|---------------------------|-------------------|

| Current rating, A         | 150               |

| Max motor duty, kW        | 225               |

| Max transformer duty, kVA | 250               |

| Closing coil closing, W   | 250               |

| 110A ac hold in, W        | 12                |

| Weight of contactor, kg   | 4                 |

| Thermal rating (1s), kA   | 4                 |

| Mechanical life, cycles   | $5 \times 10^{6}$ |

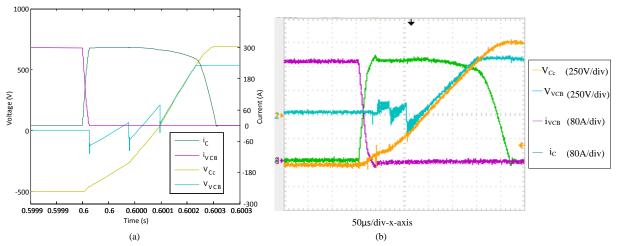

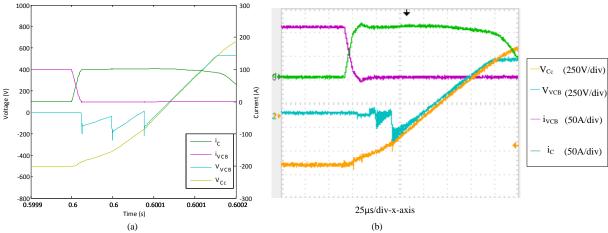

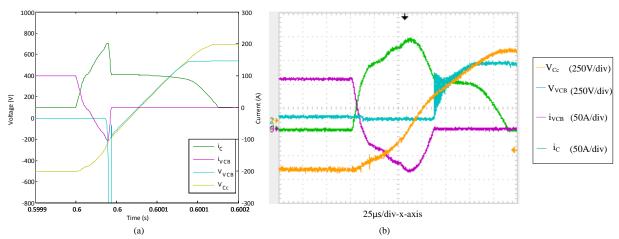

Fig. 6 and Fig. 7 show a successful interruption at first current-zero with 110A and 330A fault currents respectively. The general form and shape are the same in both cases. The VCB current  $i_{VCB}$  is reduced as the counter-current  $i_C$  rises, then the decline rate of  $i_{VCB}$  is modified when the commutation path is switched. After the current-zero the VCB experiences a stepped-shaped pulse, since the residual voltages across each commutation capacitor,  $V_{C_{C1}} - V_{C_{C2}} - V_{C_{C3}}$ , are charged step by step.

A successful interruption at a second current-zero with a 110A fault is shown in Fig. 8.  $i_{VCB}$  reaches a second current-zero with a lower amplitude due to the capacitors progressively discharging. The primary objective for the cascaded circuit is to improve the di/dt by increasing the commutation time, thereby increasing the interruption probability at the first current-zero.

Fig. 6: *Cascaded commutation circuit voltage and current at first current-zero interruption* (a) Simulation results

(b) Experimental results

$$(V_{DC}=600\rm{V},~C_{bank}=7\rm{mF},~C_{C1,2,3}=120\mu F,~R_1=200\Omega,~L_C=49.4\mu H,~L_{LOAD}=1.7\rm{mH},~R_{LOAD}=600\Omega,~R_{FAULT}=1.7\Omega)$$

Fig. 7: Cascaded commutation circuit voltage and current at first current-zero interruption (a) Simulation result

(b) Experimental result

$$(V_{DC}=600\rm{V},~C_{bank}=7\rm{mF},~C_{C1,2,3}=12.81\mu F,~R_1=200\Omega,~L_C=49.4\mu H,~L_{LOAD}=1.7\rm{mH},~R_{LOAD}=600\Omega,~R_{FAULT}=5.5\Omega)$$

Fig. 8: Cascaded commutation circuit voltage and current in a successful interruption at the second current-zero interruption

- (a) Simulation results

- (b) Experimental results

$$(V_{DC}=600\mathrm{V},~C_{bank}=7\mathrm{mF},~C_{C1,2,3}=12.81\mu\mathrm{F},~R_1=200\Omega,~L_C=49.4\mu\mathrm{H},~L_{LOAD}=1.7\mathrm{mH},~R_{LOAD}=600\Omega,~R_{FAULT}=5.5\Omega)$$

#### IV. CONCLUSION

This paper proposed a cascaded commutation circuit, without snubber circuits, inspiration by a saturable reactor which slowed the *di/dt* prior to current-zero and then produced a low voltage amplitude pulse. The validity of cascaded commutation principle was confirmed by simulation and experimentally. The experimental results are conducted at a lower power level in order to validate the commutation circuit performance.

Successful fault current interruption at the first and second current-zeros is achieved with decreased di/dt and  $dv_{VCB}/dt$ . The proposed cascaded commutation circuitry shows only three cascaded voltage stages but this can be increased, depending on the voltage resolution of the  $dV_{VCB}/dt$  and the DC system voltage.  $T_2$  and  $T_4$  in Fig. 1 can be combined into a single back-to-back configuration, saving two diodes, but is not shown in this paper to give circuit analysis simplicity. The proposed circuit architecture consist of a single IGBT device in each cascaded voltage stage, which its voltage rating is associated with its capacitor voltage level. Lower IGBT voltage devices can be used to reduce the power losses during the commutation process but will result in more cascaded voltage stages. However, the voltage resolution of  $dV_{VCB}/dt$  is increased.

Conventional series connected capacitors required shunted resistors for voltage balancing and discharge of the capacitors energy when the power system is disconnected. However, when this technique is employed in the proposed circuit, the capacitors voltage need to be trickled charge by T1 to maintain its DC voltages as DC fault does not occur frequently. This approach is currently employed in the proposed circuit. The alternative approach in the proposed technique is not using shunt resistor but overrate the capacitor voltage rating according to the capacitor tolerances. This eliminates the trickle charge process but required auxiliary circuit to discharge the capacitor energy when repair or maintenance work to the system is necessary.

Timing control on the respective gate signals in the three level cascaded voltage stages are accomplished by a mid-range 16-bit micro-controller (dsPIC30F2020), utilizing only 60% of the controller capability. The controller algorithm is not presented as the primary focus is to demonstrate the proposed commutation circuit performance. Isolation of the IGBT gate drives between each voltage stages can be accomplished by utilizing fibre-optic technologies, greatly enhancing the reliability of the cascaded commutation circuit.

The proposed technique is analysed and demonstrated under uni-directional DC current flow system. However, its feasibility in bidirectional DC current flow system is possible by replacing the diodes (*T2*, *T4*, *T5* and *T6*) in the cascaded commutation circuit with IGBTs. This

allows bidirectional current flow in the commutation circuit. Alternative control mechanism is needed for bidirectional DC current fault interruption. Detailed operational structure of the proposed technique for bidirectional current interruption is not presented in this paper.

Total failure in operation of the devices during fault condition can result DC arcing in the mechanical DC breaker. Failure Mode Evaluation Analysis (FMEA) on the proposed commutation circuit is not presented in this paper and is proposed for future works.

## V. ACKNOWLEDGEMENT

The authors gratefully acknowledge the support of EPSRC grant EP/K035096/1: Underpinning Power Electronics 2012 – Converters theme.

#### REFERENCE

- [1] C. Meyer, S. Schroder, and R. W. D. Doncker, "Solid-state circuit breakers and current limiters for medium-voltage systems having distributed power systems," *IEEE Transactions on Power Electronics*, vol. 19, pp. 1333-1340, 2004.

- [2] R. Sirsi, S. Prasad, A. Sonawane, and A. Lokhande, "Efficiency comparison of AC distribution system and DC distribution system in microgrid," in 2016 International Conference on Energy Efficient Technologies for Sustainability (ICEETS), 2016, pp. 325-329.

- [3] R. Mehl and P. Meckler, "Comparison of advantages and disadvantages of electronic and mechanical Protection systems for higher Voltage DC 400 V," in *Telecommunications Energy Conference 'Smart Power and Efficiency' (INTELEC)*, *Proceedings of 2013 35th International*, 2013, pp. 1-7.

- [4] M. Corti, E. Tironi, and G. Ubezio, "DC Networks Including Multiport DC/DC Converters: Fault Analysis," *IEEE Transactions on Industry Applications*, vol. 52, pp. 3655-3662, 2016.

- [5] J. C. Das, "Arc-Flash Hazard Calculations in LV and MV DC Systems Part—II: Analysis," *Industry Applications, IEEE Transactions on*, vol. 50, pp. 1698-1705, 2014.

- [6] M. Walter and C. Franck, "Improved Method for Direct Black-Box Arc Parameter Determination and Model Validation," *Power Delivery, IEEE Transactions on*, vol. 29, pp. 580-588, 2014.

- [7] M. B. Schulman and P. G. Slade, "Sequential modes of drawn vacuum arcs between butt contacts for currents in the 1 kA to 16 kA range," *Components, Packaging, and Manufacturing Technology, Part A, IEEE Transactions on*, vol. 18, pp. 417-422, 1995.

- [8] R. Zhigang, M. Ruiguang, S. Hao, N. Jiaqi, C. Zhexin, and N. Chunping, "Experimental investigation of arc characteristics in medium-voltage DC circuit breaker," in *TENCON* 2013 2013 IEEE Region 10 Conference (31194), 2013, pp. 1-4.

- [9] H. Y. Elzagzoug, J. W. Spencer, and A. G. Deakin, "DC Current Limitation Principle Using a Helical Arc Arrangement," *Power Delivery, IEEE Transactions on*, vol. 30, pp. 122-128, 2015.

- [10] P. Chang, I. Husain, A. Huang, B. Lequesne, and R. Briggs, "A fast mechanical switch for medium voltage hybrid DC and AC circuit breakers," in *Energy Conversion Congress and Exposition (ECCE)*, 2015 IEEE, 2015, pp. 5211-5218.

- [11] J. Jadidian, "A Compact Design for High Voltage Direct Current Circuit Breaker," *IEEE Transactions on Plasma Science*, vol. 37, pp. 1084-1091, 2009.

- [12] K. A. Corzine and R. W. Ashton, "A New Z-Source DC Circuit Breaker," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 2796-2804, 2012.

- [13] M. Kempkes, I. Roth, and M. Gaudreau, "Solid-state circuit breakers for Medium Voltage DC power," in *Electric Ship Technologies Symposium (ESTS)*, 2011 IEEE, 2011, pp. 254-257.

- [14] S. Juvekar, B. Compton, and S. Bhattacharya, "A fast acting DC solid state fault isolation device (FID) with Si and SiC devices for MVDC distribution system," in *Energy Conversion Congress and Exposition (ECCE), 2012 IEEE*, 2012, pp. 2005-2010.

- [15] Z. J. Shen, G. Sabui, M. Zhenyu, and S. Zhikang, "Wide-Bandgap Solid-State Circuit Breakers for DC Power Systems: Device and Circuit Considerations," *Electron Devices, IEEE Transactions on*, vol. 62, pp. 294-300, 2015.

- [16] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, "A Survey of Wide Bandgap Power Semiconductor Devices," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 2155-2163, 2014.

- [17] T. C. Lim, B. W. Williams, S. J. Finney, and P. R. Palmer, "Series-Connected IGBTs Using Active Voltage Control Technique," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 4083-4103, 2013.

- [18] P. Chang, A. Q. Huang, and S. Xiaoqing, "Current commutation in a medium voltage hybrid DC circuit breaker using 15 kV vacuum switch and SiC devices," in *Applied Power Electronics Conference and Exposition (APEC)*, 2015 IEEE, 2015, pp. 2244-2250.

- [19] W. Yifei, R. Mingzhe, W. Yi, Y. Fei, L. Mei, and L. Yang, "Development of a new topology of dc hybrid circuit breaker," in *Electric Power Equipment Switching Technology (ICEPE-ST)*, 2013 2nd International Conference on, 2013, pp. 1-4.

- [20] L. Luhui, Z. Jinwu, W. Chen, J. Zhuangxian, W. Jin, and C. Bo, "A Hybrid DC Vacuum Circuit Breaker for Medium Voltage: Principle and First Measurements," *Power Delivery, IEEE Transactions on*, vol. 30, pp. 2096-2101, 2015.

- [21] Y. W. Yifei Wu, Mingzhe Rong, Fei Yang, Chunping Niu, Mei Li, Yang Hu "Research on a novel two-stage direct current hybrid circuit breaker," *AIP Review of Scientific Instruments*, vol. 85, 2014.

- [22] Y. Shan, T. C. Lim, B. W. Williams, and S. J. Finney, "Successful fault current interruption on DC circuit breaker," *IET Power Electronics*, vol. 9, pp. 207-218, 2016.

- [23] ABB, "The Hybrid HVDC Breaker An innovation breakthrough enabling reliable HVDC grids."

- [24] K. Shenai, "Power Electronic Module: Enabling the 21st-century energy economy," *Power Electronics Magazine, IEEE*, vol. 1, pp. 27-32, 2014.

- [25] J. Dries, "SiC Research and Development at United Silicon Carbide Inc.?Looking Beyond 650?1,200 V Diodes and Transistors [Happenings]," *Power Electronics Magazine, IEEE*, vol. 2, pp. 12-15, 2015.

- [26] J. F. Donlon, E. R. Motto, E. Wiesner, E. Thal, K. Hatori, Y. Sakai, S. Kitamura, T. Motomiya, K. Ota, Y. Kitajima, S. Iura, H. Yamaguchi, and K. Kurachi, "The next generation 6.5kV IGBT," in *Energy Conversion Congress and Exposition (ECCE)*, 2014 IEEE, 2014, pp. 2897-2900.

- [27] L. Zhenxian, N. Puqi, and F. Wang, "Development of Advanced All-SiC Power Modules," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 2289-2295, 2014.

- [28] S. Madhusoodhanan, K. Hatua, S. Bhattacharya, S. Leslie, R. Sei-Hyung, M. Das, A. Agarwal, and D. Grider, "Comparison study of 12kV n-type SiC IGBT with 10kV SiC MOSFET and 6.5kV Si IGBT based on 3L-NPC VSC applications," in *Energy Conversion Congress and Exposition (ECCE)*, 2012 IEEE, 2012, pp. 310-317.

- [29] C. Meyer, M. Kowal, and R. W. De Doncker, "Circuit breaker concepts for future high-power DC-applications," in *Industry Applications Conference*, 2005. Fourtieth IAS Annual Meeting. Conference Record of the 2005, 2005, pp. 860-866 Vol. 2.

- [30] Y. Shan, "Direct Current Hybrid Vacuum Breaker," *PhD thesis, University of Strathclyde*, 2014.

- [31] M. M. Walter and C. M. Franck, "Optimal Test Current Shape for Accurate Arc Characteristic Determination," *Power Delivery, IEEE Transactions on*, vol. 29, pp. 1798-1805, 2014.

- [32] G. A. Farrall, "Recovery of Dielectric Strength after Current Interruption in Vacuum," *Plasma Science, IEEE Transactions on*, vol. 6, pp. 360-369, 1978.