# Power conversion for a modular lightweight direct-drive wind turbine generator

Max Alexander Parker

A Thesis presented for the degree of Engineering Doctorate

School of Electrical, Electronic and Computer Engineering

University of Newcastle upon Tyne

England

July 2009

#### Power conversion for a modular lightweight direct-drive wind turbine generator

#### Max Parker

Submitted for the degree of Engineering Doctorate

July 2009

#### Abstract

A power conversion system for a modular lightweight direct-drive wind turbine generator has been proposed, based on a modular cascaded multilevel voltage-source inverter. Each module of the inverter is connected to two generator coils, which eliminates the problem of DC-link voltage balancing found in multilevel inverters with a large number of levels.

The slotless design of the generator, and modular inverter, means that a high output voltage can be achieved from the inverter, while using standard components in the modules. Analysis of the high voltage issues shows that isolating the modules to a high voltage is easily possible, but insulating the generator coils could result in a significant increase in the airgap size, reducing the generator efficiency.

A boost rectifier input to the modules was calculated to have the highest electrical efficiency of all the rectifier systems tested, as well as the highest annual power extraction, while having a competitive cost. A rectifier control system, based on estimating the generator EMF from the coil current and drawing a sinusoidal current in phase with the EMF, was developed. The control system can mitigate the problem of airgap eccentricity, likely to be present in a lightweight generator.

A laboratory test rig was developed, based on two 2.5kW generators, with 12 coils each. A single phase of the inverter, with 12 power modules, was implemented, with each module featuring it's own microcontroller. The system is able to produce a good quality AC voltage waveform, and is able to tolerate the fault of a single module during operation.

A decentralised inverter control system was developed, based on all modules estimating the grid voltage position and synchronising their estimates. Distributed output current limiting was also implemented, and the system is capable of riding through grid faults.

### **Declaration**

The work in this thesis is based on research carried out in the New and Renewable Energy Group, the School of Engineering, Durham University, England, in conjunction with the New and Renewable Energy Centre (NAREC), Blyth, Northumberland and the University of Newcastle Upon Tyne. No part of this thesis has been submitted elsewhere for any other degree or qualification and it all my own work unless referenced to the contrary in the text.

#### Copyright © 2009 by Max Parker.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

## Acknowledgements

I would like to thank my supervisor, Dr. Li Ran, for his endless patience in supervising me, and his knowledge and enthusiasm. I would also like to thank Professor Peter Tavner for his role in my supervision, for introducing me to the joy of Microsoft Project, and inspiring me with many stories of his time in the Royal Navy and the electrical engineering industry. At Newcastle University Professor Alan Jack has provided much constructive criticism of the high voltage aspects of the project, and without his input chapter 5 would never have been written, and this thesis would have been much the poorer.

The test rig would never have been built without the amazing work of the electrical and mechanical workshop technicians, with special thanks to David Jones for wiring everything up, Neil Clarey for manufacturing the control boards, Tony Collinson for building the mechanical systems and Ian Hutchinson for ordering components and running everything smoothly. I am also greatful to Cleveland Circuits, who manufactured the power boards.

From NaREC, I would like to thank Kevin Hanley for his kind assistance in explaining the company structure and finances for my Eng Doc business case study. I would also like to thank Steve McDonald, Adrian Wilson and Stephen Wilson for their support during the project.

Acknowledgements must go out to my fellow postgraduate students in the New and Renewable energy group at Durham, including, but not limited to, Richard Martin, Michael Wilkinson, Nick Stannard, Fabio Spinato and Padraig Lyons. Much merriment was had over the years, as well as much discussion about engineering.

Finally I would like to thank the past and present members of the Durham University Karate-do Shotokai club, including Grant Ingram, Aidan Rhodes, Thomas Butts, Andrew Egan, James Holloway, Will Black, Philippa Wilcox and Angharad Kenway. Practicing karate with these people has provided an outlet for the anger and frustration which frequently arises throughout the course of academic research, and has helped keep me sane.

|   | Abs  | stract  |                                                     | ii           |

|---|------|---------|-----------------------------------------------------|--------------|

|   | Dec  | laratio | on                                                  | iii          |

|   | Ack  | nowle   | dgements                                            | $\mathbf{v}$ |

| 1 | Intr | oducti  | ion                                                 | 1            |

|   | 1.1  | Variab  | ole Speed Concepts                                  | . 2          |

|   |      | 1.1.1   | Geared Doubly Fed Induction Generator               | . 2          |

|   |      | 1.1.2   | Direct Drive Synchronous Machine                    | . 4          |

|   |      | 1.1.3   | Alternative Systems                                 | . 6          |

|   | 1.2  | Turbir  | ne Scalability                                      | . 7          |

|   | 1.3  | Lightv  | weight Direct Drive Generators                      | . 7          |

|   | 1.4  | Power   | Electronic Interface                                | . 9          |

|   |      | 1.4.1   | Marine Drive and Other Multiphase Applications      | . 10         |

|   |      | 1.4.2   | Power Conversion Issues with Lightweight Generators | . 12         |

|   |      | 1.4.3   | Proposed Power Electronic Interface                 | . 13         |

|   | 1.5  | Scope   | of this Project                                     | . 14         |

| 2 | The  | e Savor | nius Project                                        | 16           |

|   | 2.1  |         | ling of the System                                  |              |

|   | 2.2  |         | ation Results                                       |              |

|   | 2.3  | Propo   | sed Power Tracking Solution                         |              |

|   |      | 2.3.1   | Converter Topology                                  |              |

|   |      | 2.3.2   | Tracking Algorithm                                  |              |

|   |      | 2.3.3   | Operating Range                                     |              |

|   | 2.4  | Implei  | mentation of the Power Interface                    |              |

|   |      | 2.4.1   | Boost Converter Implementation                      | . 25         |

|   |      | 2.4.2   | Controller Hardware Implementation                  |              |

|   |      | 2.4.3   | Controller Software Implementation                  | . 27         |

|   | 2.5  | Testin  | ıg                                                  | . 27         |

|   |      | 2.5.1   | Converter Operation                                 | . 28         |

|   |      | 2.5.2   | Tracking Algorithm Operation                        | . 29         |

|   | 2.6  | Simula  | ation and Analysis of System Operation              |              |

|   |      | 2.6.1   | Simulation of the Tracking Algorithm                | . 31         |

|   |      | 2.6.2   | Estimate of Annual Energy Capture                   | . 32         |

|   | 2.7  | Concl   | usion                                               | 37           |

| 3 | Pov  | ver Electronic Architecture and Turbine Control            | 40 |

|---|------|------------------------------------------------------------|----|

|   | 3.1  | Wind Turbine Characteristics                               | 41 |

|   |      | 3.1.1 Stall Regulation                                     | 41 |

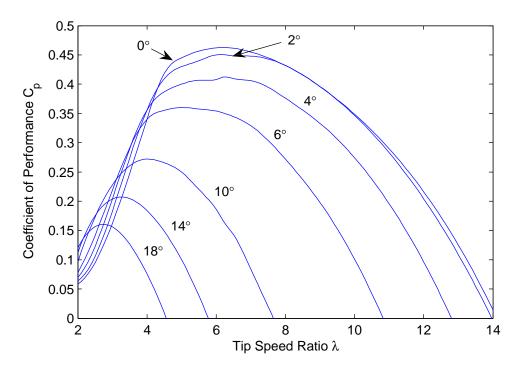

|   |      | 3.1.2 Pitch Regulation                                     | 43 |

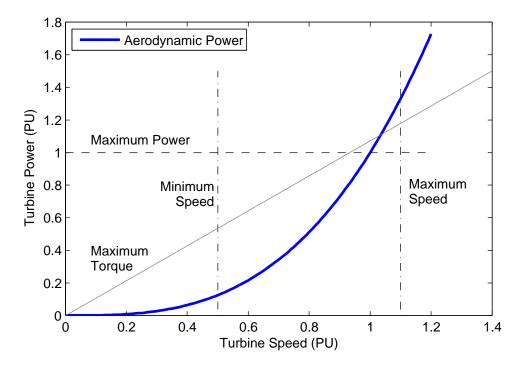

|   | 3.2  | Variable Speed Turbine Operating Regions                   | 44 |

|   |      | 3.2.1 Power Limited Operating Region                       | 45 |

|   |      | 3.2.2 Speed Limited Operating Region                       | 46 |

|   |      | 3.2.3 Torque Limited Operating Region                      | 48 |

|   |      | 3.2.4 Choice of Operating Region                           | 50 |

|   | 3.3  | Power Electronic Interface Architecture                    | 51 |

|   | 3.4  | Calculation of System Power Curve                          | 53 |

|   |      | 3.4.1 Turbine and Generator for Analysis                   | 53 |

|   |      | 3.4.2 Fundamental Inverter Switching and Passive Rectifier | 54 |

|   |      | 3.4.3 PWM Switching and Passive Rectifier                  | 58 |

|   |      | 3.4.4 Fundamental Switching and Boost Rectifier            | 59 |

|   | 3.5  | Calculation of Annual Energy Extraction                    | 62 |

| 4 | Pov  | ver Electronic Components, Costs and Performance           | 64 |

|   | 4.1  | Fault Tolerance Considerations                             | 66 |

|   |      | 4.1.1 IGBT Failure Modes                                   | 66 |

|   |      | 4.1.2 Grid Side – Module Bypassing Methods                 | 67 |

|   |      | 4.1.3 Machine Side – Input Protection                      | 67 |

|   | 4.2  | System Modelling                                           | 67 |

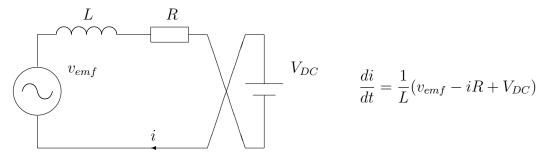

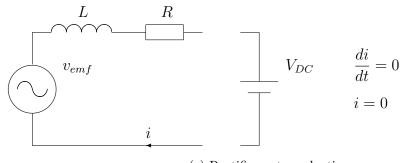

|   |      | 4.2.1 Simulation of the Rectifier                          | 68 |

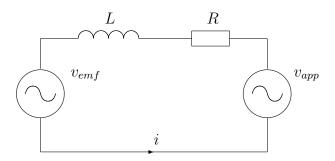

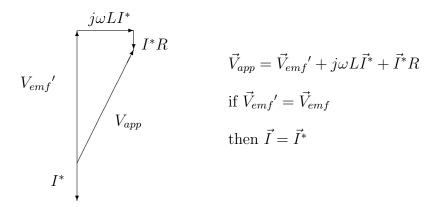

|   |      | 4.2.2 Control of the Boost Rectifier                       | 70 |

|   |      | 4.2.3 Boost rectifier switching frequency                  | 71 |

|   | 4.3  | Component Selection                                        | 72 |

|   |      | 4.3.1 Output H-Bridge                                      | 73 |

|   |      | 4.3.2 Input Rectifier                                      | 74 |

|   |      | 4.3.3 DC-Link Capacitors                                   | 75 |

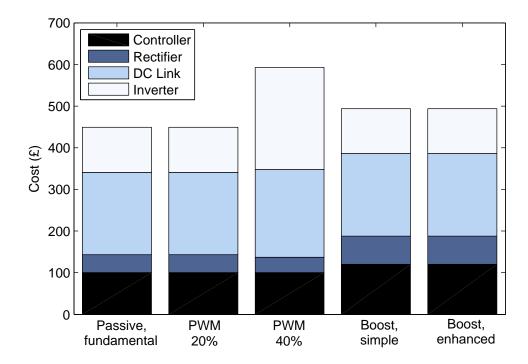

|   | 4.4  | Estimates of Module Cost                                   | 78 |

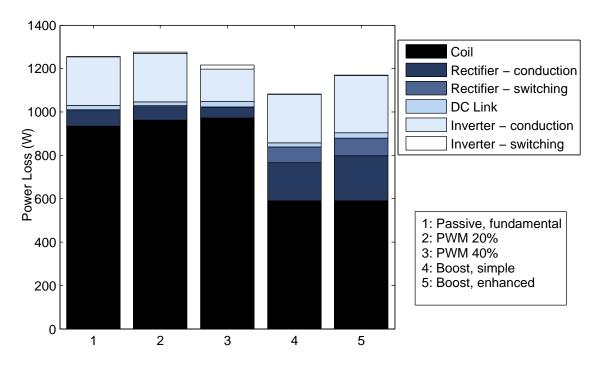

|   | 4.5  | Estimates of Losses                                        | 79 |

|   | 4.6  | Module Design Choice                                       | 82 |

| 5 | Ana  | alysis of Generator High Voltage Issues                    | 84 |

|   | 5.1  | Machine Geometry                                           | 85 |

|   | 5.2  | Normal Conditions                                          | 85 |

|   | ٠٠_  | 5.2.1 Insulation Requirements                              | 85 |

|   |      | 5.2.2 Insulation of Generator Coils                        | 87 |

|   |      | 5.2.3 Insulation of Power Modules                          | 90 |

|   | 5.3  | Lightning Strike Protection                                | 96 |

|   | 0.0  | 5.3.1 Protection of Conventional Turbines                  | 97 |

|   |      | 5.3.2 Issues Specific to the Proposed Generator            | 97 |

|   | 5.4  | Summary of Insulation Issues                               |    |

|   | J. I | ~ ~                                                        | 50 |

| 6 | $\mathbf{Dev}$ | relopment of a Control Strategy                         | 100 |

|---|----------------|---------------------------------------------------------|-----|

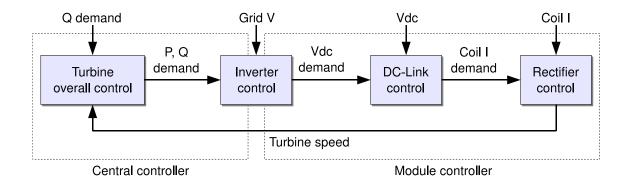

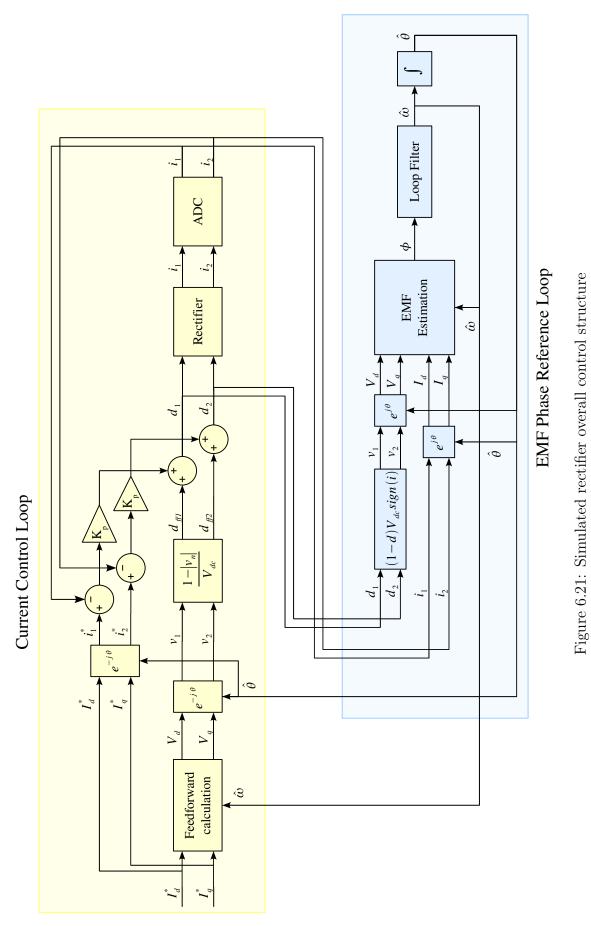

|   | 6.1            | Control System Structure                                | 100 |

|   | 6.2            | Machine and Rectifier Model                             | 102 |

|   |                | 6.2.1 Effects of Airgap Eccentricity                    | 103 |

|   | 6.3            | Control of Coil Current                                 | 106 |

|   |                | 6.3.1 Simulation of Coil Current                        |     |

|   |                | 6.3.2 Airgap Eccentricity Considerations                | 111 |

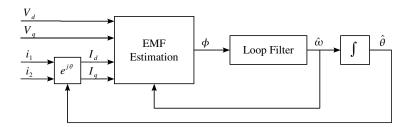

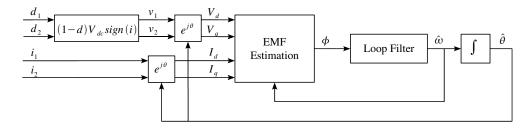

|   | 6.4            | Estimation of Generator EMF                             | 113 |

|   |                | 6.4.1 Phaselock Loop for EMF Position Estimation        | 113 |

|   |                | 6.4.2 Phase Detector                                    | 114 |

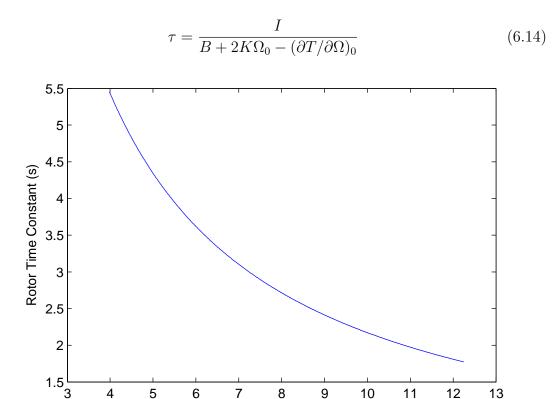

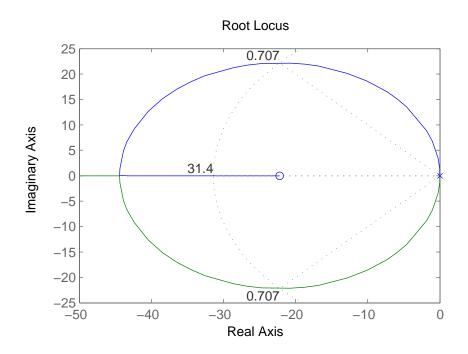

|   |                | 6.4.3 Loop Filter                                       | 116 |

|   |                | 6.4.4 Simulation of EMF Position Tracking               | 120 |

|   |                | 6.4.5 Airgap Eccentricity and EMF Magnitude Calculation | 124 |

|   | 6.5            | Inverter Control                                        | 125 |

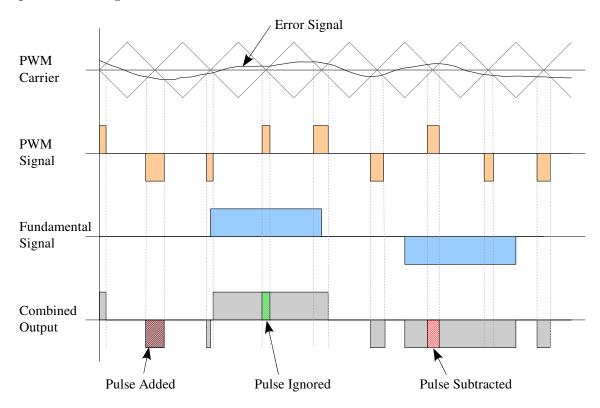

|   |                | 6.5.1 Basic Inverter Switching                          | 127 |

|   |                | 6.5.2 Harmonic Compensation Switching                   | 128 |

|   | 6.6            | DC-Link Voltage Control                                 | 133 |

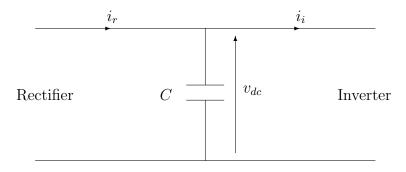

|   |                | 6.6.1 Modelling the DC-Link                             | 133 |

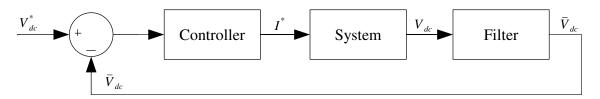

|   |                | 6.6.2 Controller Structure                              |     |

|   |                | 6.6.3 Simulation of DC-Link Voltage Control             |     |

|   |                | 6.6.4 Airgap Eccentricity Considerations                | 138 |

|   | 6.7            | Conclusion                                              | 139 |

| 7 | Dev            | relopment of Prototype System                           | 141 |

| • | 7.1            | Aims of the Experiment                                  |     |

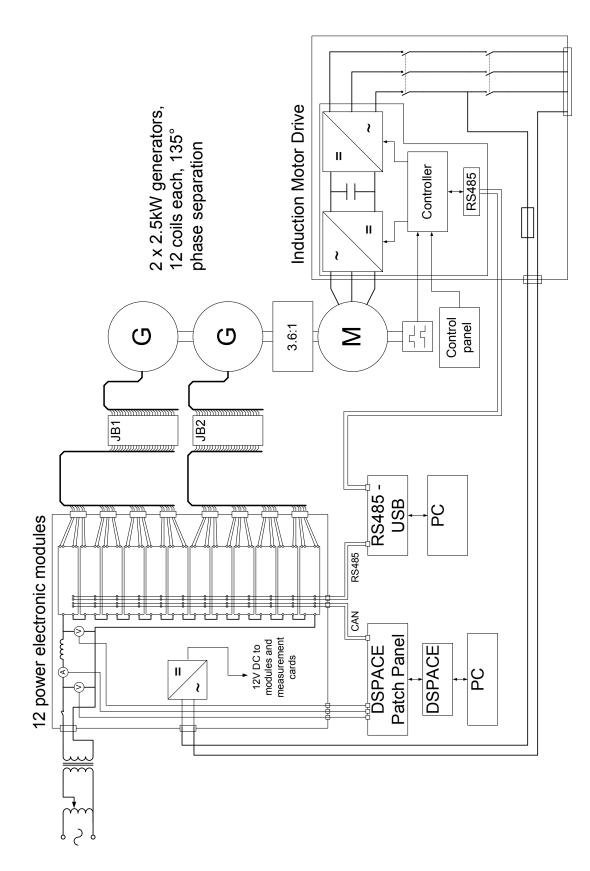

|   | 7.2            | Motor-Generator Test Rig                                |     |

|   | 7.3            | Prototype System Parameters                             |     |

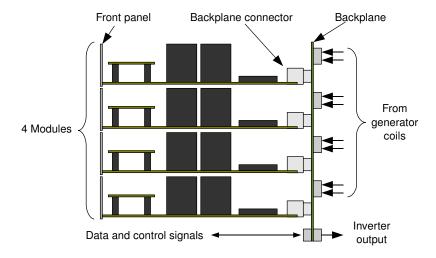

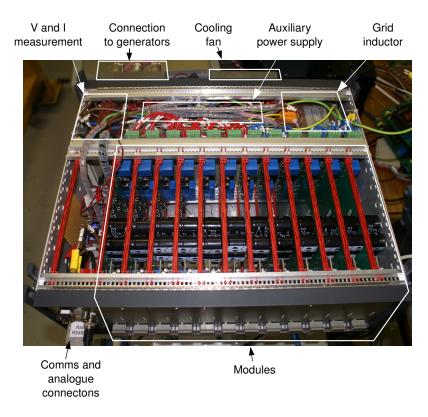

|   | 7.4            | Module Rack System                                      |     |

|   | 7.5            | EMC Considerations                                      |     |

|   |                | 7.5.1 Controlling EMI Emissions                         | 146 |

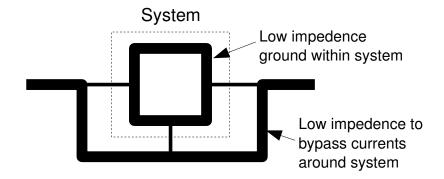

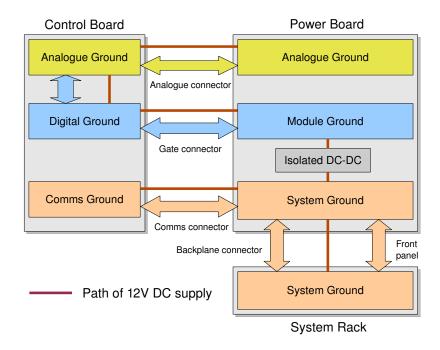

|   |                | 7.5.2 System Grounding and Shielding                    |     |

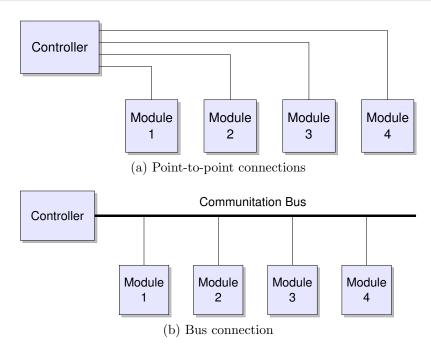

|   |                | 7.5.3 Communications                                    |     |

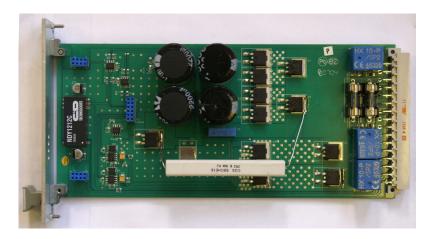

|   | 7.6            | Power Electronic Board Design                           | 148 |

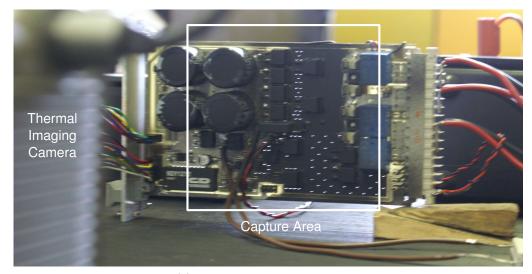

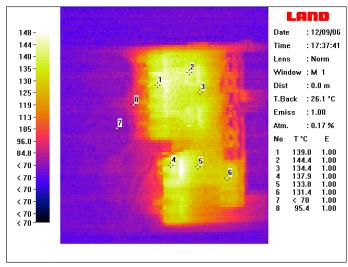

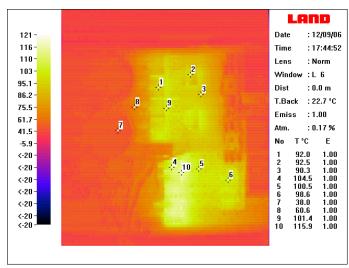

|   |                | 7.6.1 Transistor Cooling                                | 149 |

|   |                | 7.6.2 Prototype Power Board                             | 150 |

|   |                | 7.6.3 Evaluation of Cooling Capability                  |     |

|   |                | 7.6.4 Final Power Board Design                          | 153 |

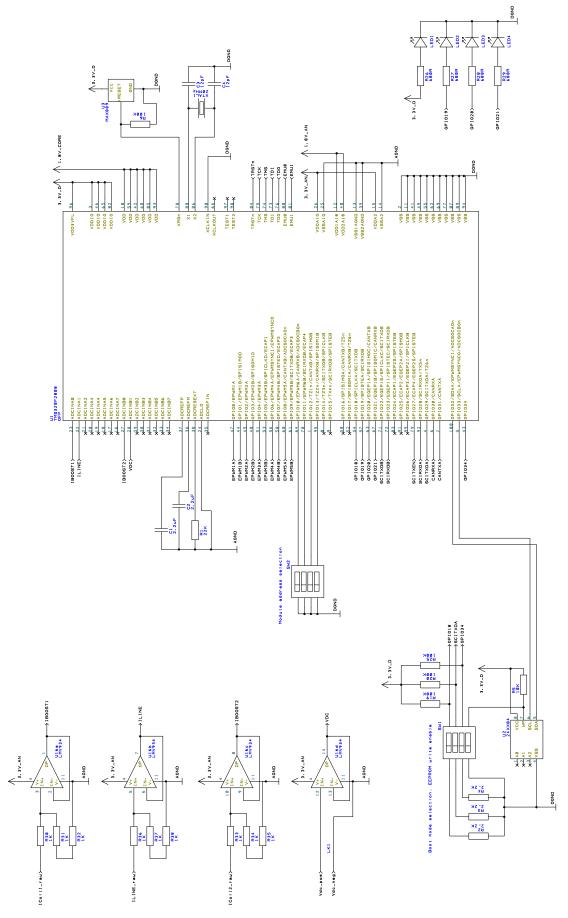

|   | 7.7            | Control Board Design                                    | 153 |

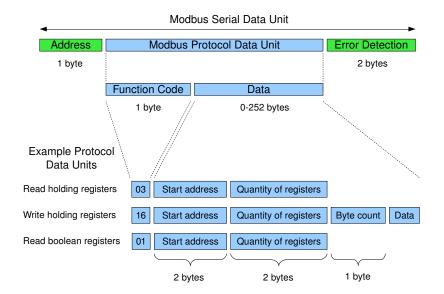

|   |                | 7.7.1 Communication and Synchronisation                 | 154 |

|   |                | 7.7.2 Choice of Microcontroller                         | 159 |

|   |                | 7.7.3 Other Control Board Components                    | 159 |

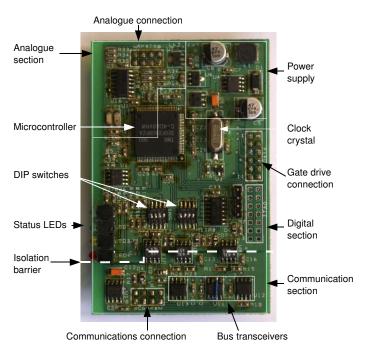

|   |                | 7.7.4 Board Layout                                      | 160 |

|   | 7.8            | Test System Hardware Overview                           | 161 |

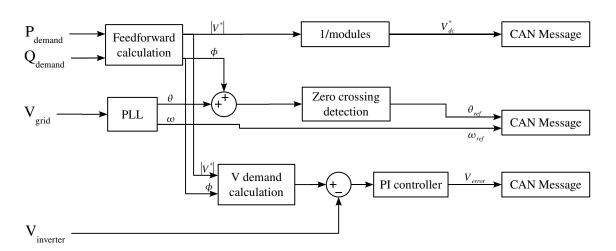

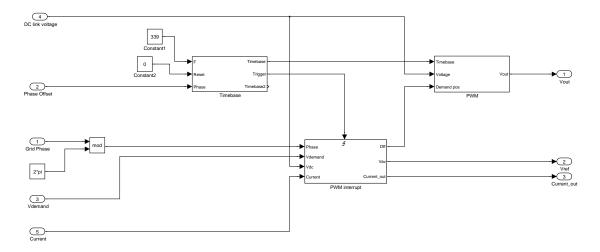

|   | 7.9            | Central Controller Operation                            | 162 |

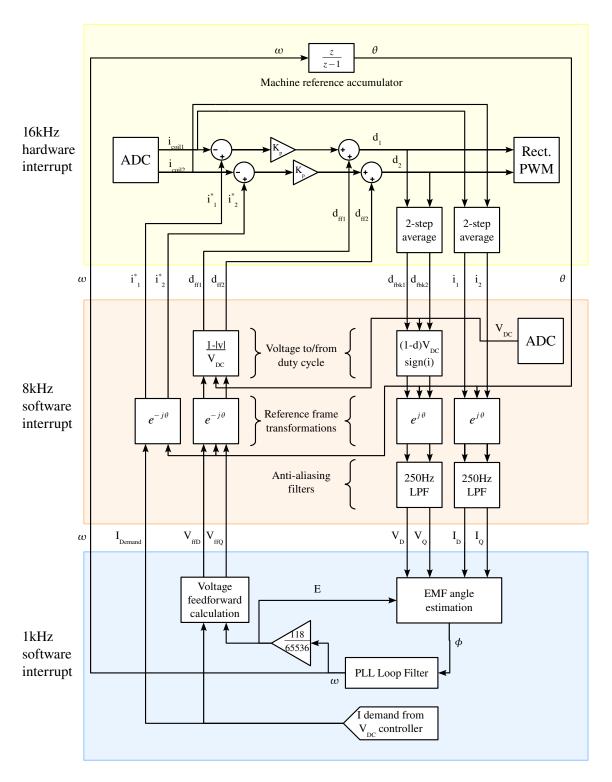

|   | 7.10           | Module Control Software Implementation                  | 166 |

|   |                | 7.10.1 Representation of Control Variables              |     |

|   |                | 7.10.2 Rectifier Controller                             | 168 |

|   |      | 7.10.3 Inverter and DC-link Voltage Controller              | . 171 |

|---|------|-------------------------------------------------------------|-------|

|   |      | 7.10.4 Communications Functions                             | . 175 |

|   | 7.11 | Conclusions                                                 | . 177 |

| 8 | Test | ting of the Basic Control System                            | 179   |

| O | 8.1  | Rectifier Current Control                                   |       |

|   | 8.2  | Machine EMF Estimation and Tracking                         |       |

|   | 8.3  | Machine EMF Position Acquisition, and Rectifier Startup     |       |

|   | 8.4  | DC-Link Voltage Control                                     |       |

|   | 0.1  | 8.4.1 Steady State Testing                                  |       |

|   |      | 8.4.2 Operation With Low Inverter Output Current            |       |

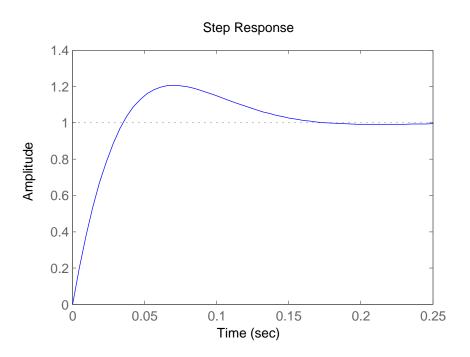

|   |      | 8.4.3 Voltage Demand Step Response                          |       |

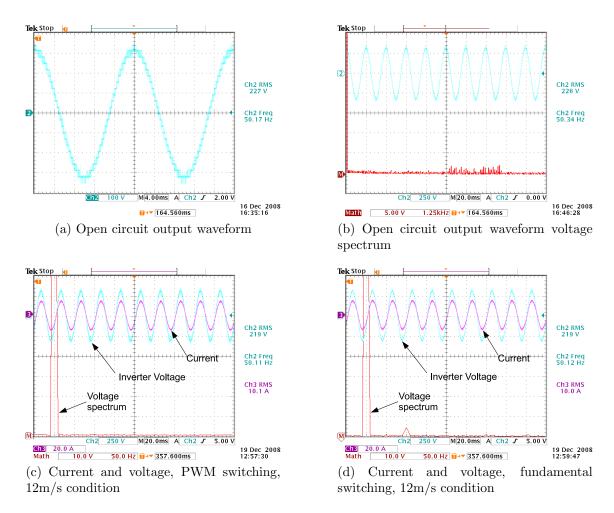

|   | 8.5  | Inverter Basic Operation                                    |       |

|   |      | 8.5.1 Testing with a Resistive Load                         |       |

|   |      | 8.5.2 Testing with the Grid Connection                      |       |

|   | 8.6  | Inverter Power Sharing                                      |       |

|   | 8.7  | Inverter Voltage Harmonic Distortion Correction             |       |

|   | 8.8  | Inverter Fault Tolerance                                    |       |

|   | 8.9  | Conclusion                                                  |       |

|   |      | 8.9.1 Rectifier Control                                     | . 204 |

|   |      | 8.9.2 DC-Link Voltage Control                               | . 207 |

|   |      | 8.9.3 Inverter Control                                      |       |

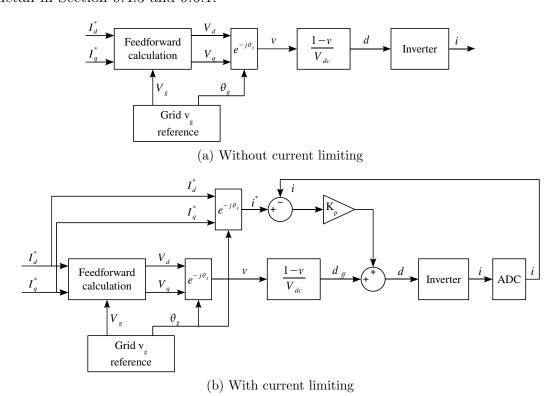

| 9 | ۸ds  | vanced Inverter Control Theory, Implementation, and Testing | . 200 |

| J | 9.1  | Proposed Solution                                           |       |

|   | 0.1  | 9.1.1 Design Tasks                                          |       |

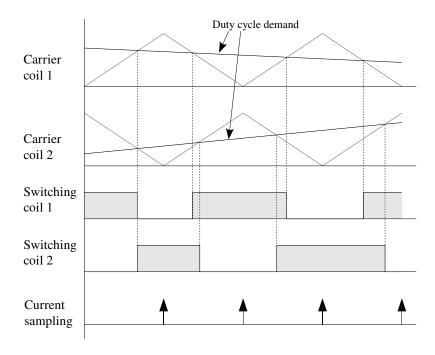

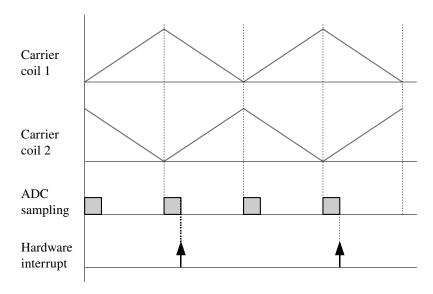

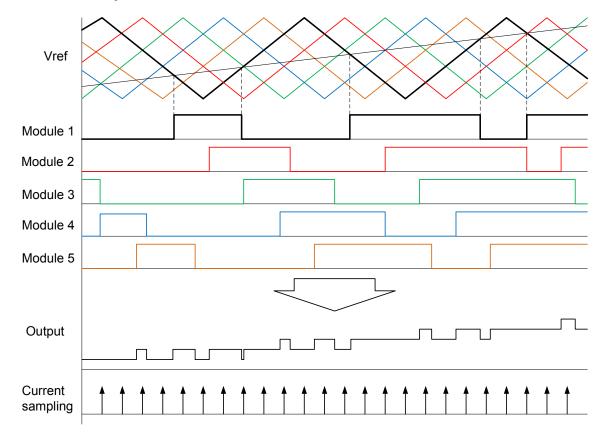

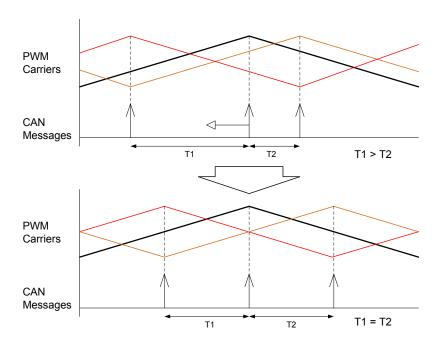

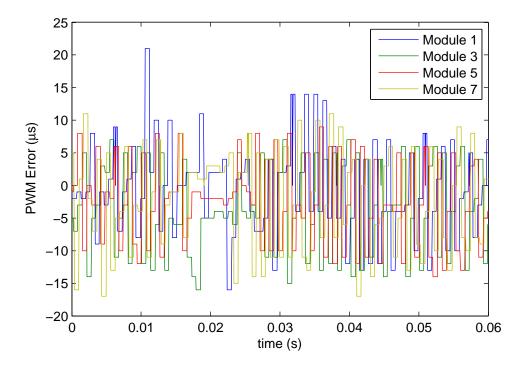

|   | 9.2  | Module PWM Interleaving and Sampling Synchronisation        |       |

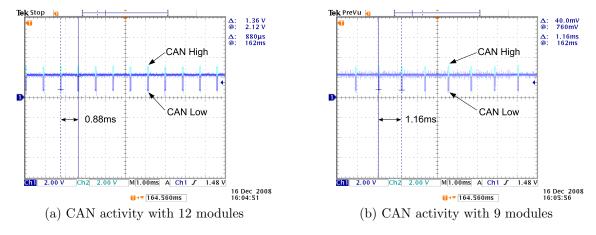

|   | 0.2  | 9.2.1 Verification of Interleaving System Operation         |       |

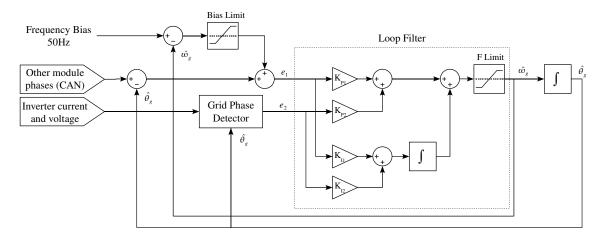

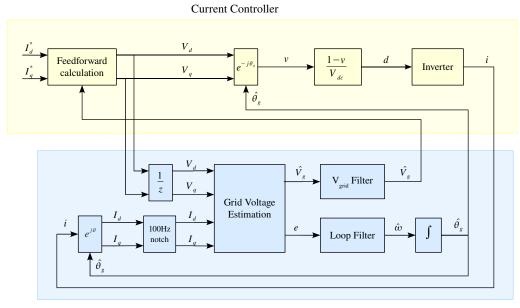

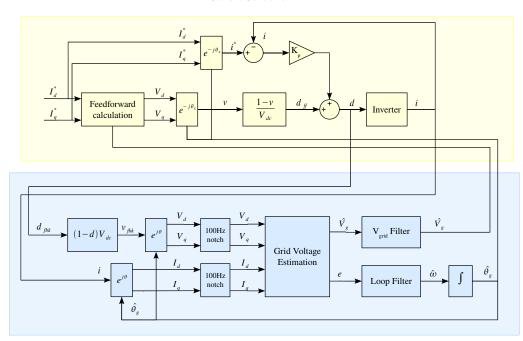

|   | 9.3  | Inverter Grid Angle Reference PLL                           |       |

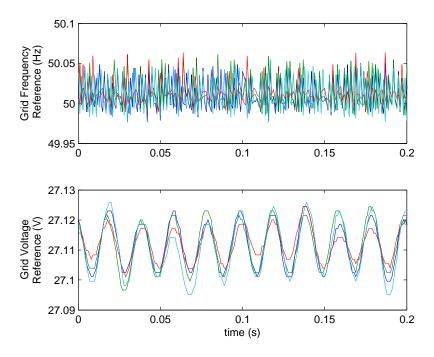

|   | 0.0  | 9.3.1 Verification of Module Grid Reference Synchronisation |       |

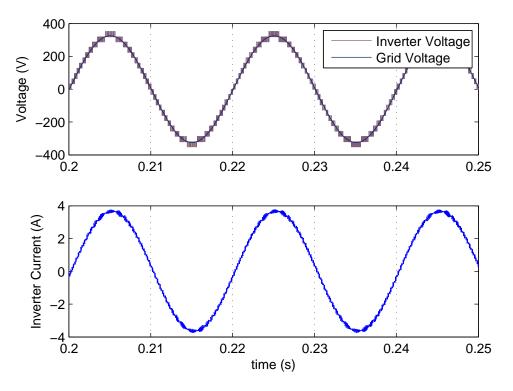

|   |      | 9.3.2 Verification of Inverter Output Waveform              |       |

|   | 9.4  | Inverter Current Controller and Current Limiting            |       |

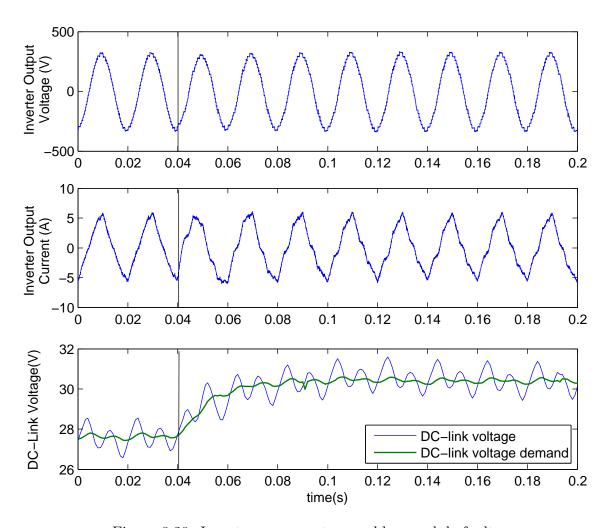

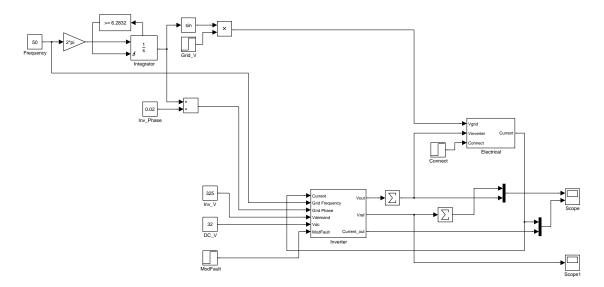

|   |      | 9.4.1 Simulation of Inverter Current Limiting               |       |

|   |      | 9.4.2 Current Control Simulation Results                    |       |

|   |      | 9.4.3 Testing of Inverter Current Limiting                  |       |

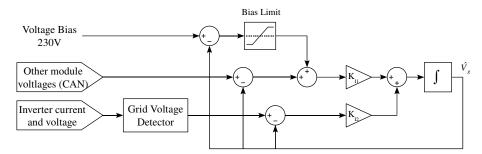

|   | 9.5  | Grid Voltage Estimation and Loop Filter Characteristics     |       |

|   |      | 9.5.1 Reference Frame Transformation and Filtering          |       |

|   |      | 9.5.2 Grid Voltage Estimation                               |       |

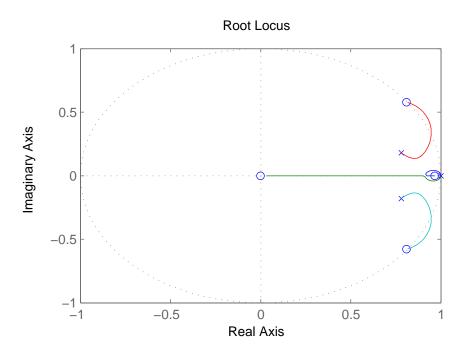

|   |      | 9.5.3 Loop Filter Design                                    |       |

|   |      | 9.5.4 Grid Voltage Magnitude Estimation Filter              |       |

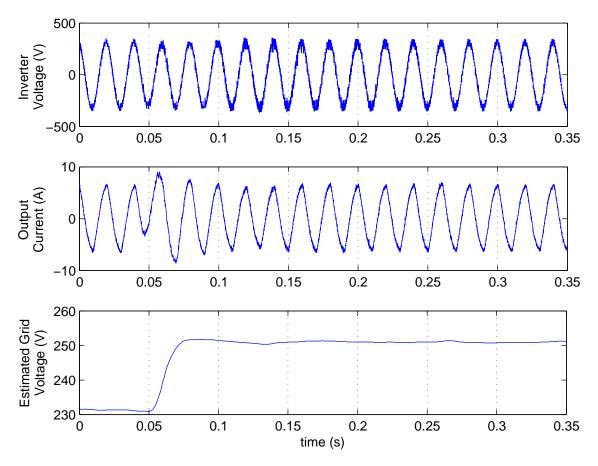

|   |      | 9.5.5 Testing of Inverter Grid Voltage Tracking             |       |

|   | 9.6  | Additional System Testing                                   |       |

|   | - 0  | 9.6.1 Grid Connection Steady State Operation                |       |

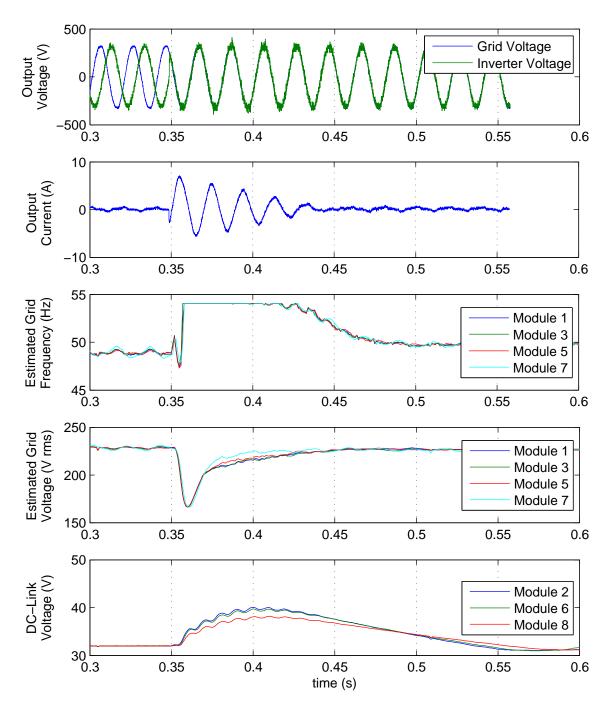

|   |      | 9.6.2 Fault Ridethrough Operation                           |       |

|   |      | 9.6.3 Power Sharing                                         |       |

|   |      | 9.6.4 Module Fault Tolerance                                |       |

|   | 9.7  | Conclusion                                                  |       |

|   |      |                                                             |       |

| 10           | Conclusion and Discussion                       | 248   |

|--------------|-------------------------------------------------|-------|

|              | 10.1 Summary of the Project Findings            | . 248 |

|              | 10.2 Power Conversion Architecture Viability    | . 251 |

|              | 10.3 Generator System Viability                 | . 253 |

|              | 10.4 Further Work                               | . 254 |

|              | Bibliography                                    | 256   |

|              | Appendix                                        | 262   |

| $\mathbf{A}$ | Published Work                                  | 262   |

| В            | Prototype Module Schematics                     | 263   |

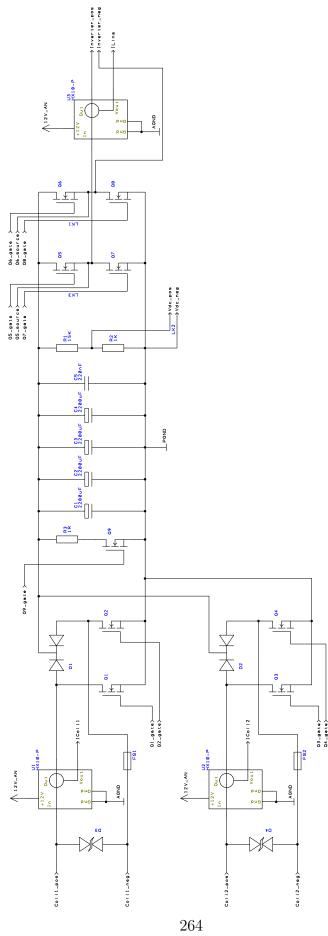

|              | B.1 Electrical Board                            | . 263 |

|              | B.2 Control Board                               |       |

| $\mathbf{C}$ | Microcontroller Code                            | 270   |

|              | C.1 Rectifier Hardware ISR                      | . 270 |

|              | C.2 8kHz Software ISR                           |       |

|              | C.3 1kHz Software ISR                           |       |

|              | C.4 Inverter Fundamental Switching Hardware ISR |       |

# List of Figures

| 1.1  | The Gedser wind turbine                                                         | 1  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Turbine Drive Systems                                                           | 3  |

| 1.3  | A Nordex wind turbine, using a geared generator                                 | 3  |

| 1.4  | Some Direct Drive Turbines                                                      | 5  |

| 1.5  | Cross section of a slotted generator, with electrical excitation                | 8  |

| 1.6  | Cross section of a slotless generator, with permanent magnet excitation         | 9  |

| 1.7  | Marine Drive Systems                                                            | 11 |

| 1.8  | Alstom/Converteam advanced induction motor                                      | 11 |

| 1.9  | Direct-drive generator with CMVSI grid interface                                | 13 |

| 2.1  | The savonius wind turbine                                                       | 17 |

| 2.2  | Small scale wind turbine battery connection                                     | 18 |

| 2.3  | Turbine $C_p$ - $\lambda$ curve                                                 | 19 |

| 2.4  | Simplorer model for the system                                                  | 20 |

| 2.5  | Electrical power vs. turbine speed at different wind speeds                     | 21 |

| 2.6  | Electrical power vs. wind speed                                                 | 22 |

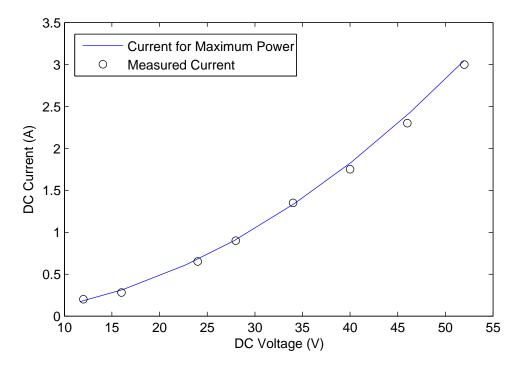

| 2.7  | $V_{dc}$ vs. $I_{dc}$ relationship at maximum power                             | 24 |

| 2.8  | Boost Converter Circuit                                                         | 26 |

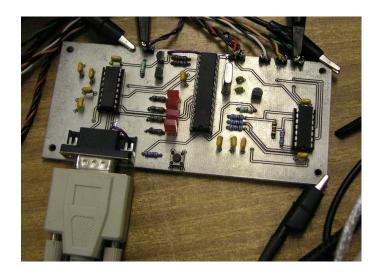

| 2.9  | Completed Converter                                                             | 26 |

| 2.10 | Completed Control Board                                                         | 26 |

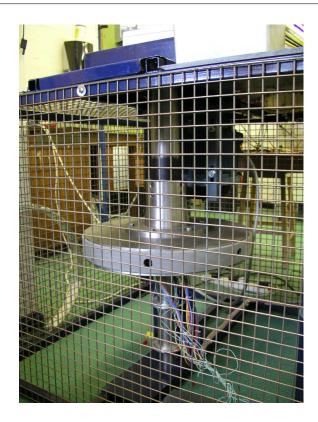

| 2.11 | Generator Prototype                                                             | 28 |

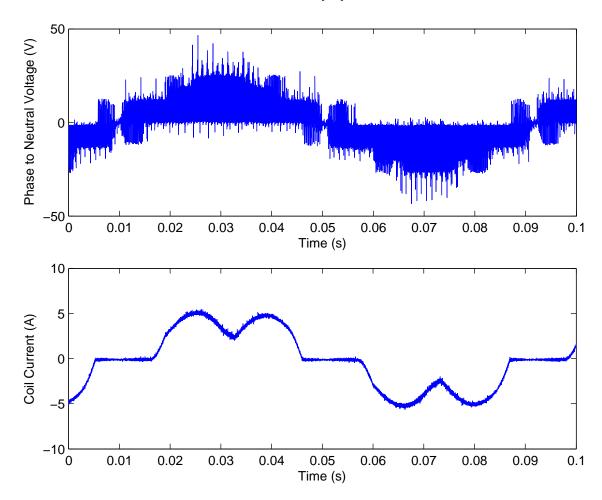

|      | Coil voltage and current for one machine EMF cycle                              | 29 |

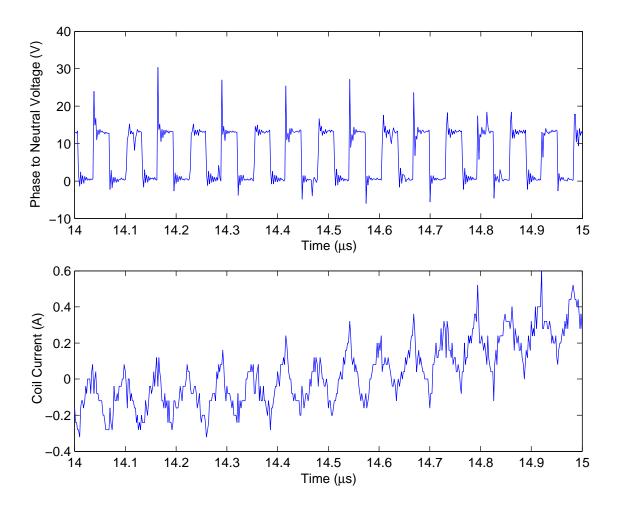

|      | Coil voltage and current at PWM switching scale                                 | 30 |

|      | Measured and desired current vs. voltage                                        | 31 |

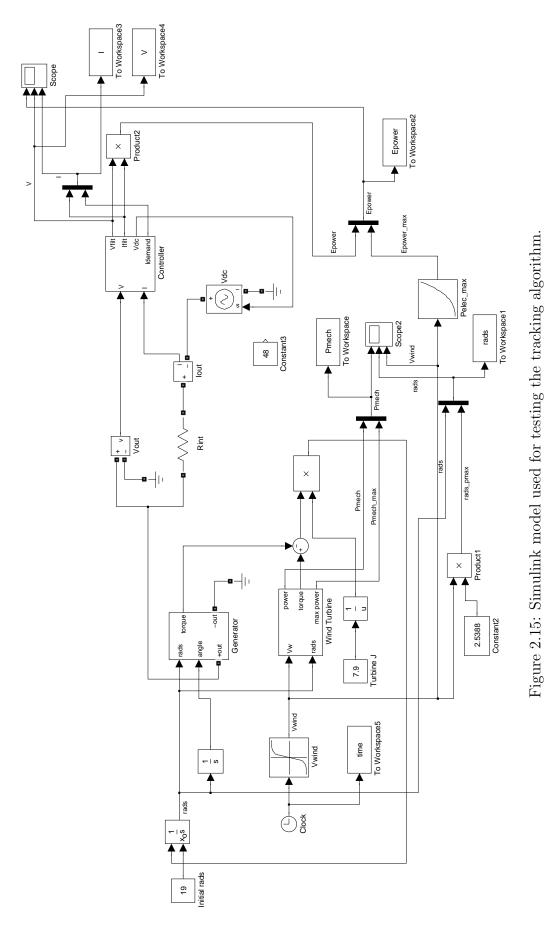

|      | Simulink model used for testing the tracking algorithm                          | 33 |

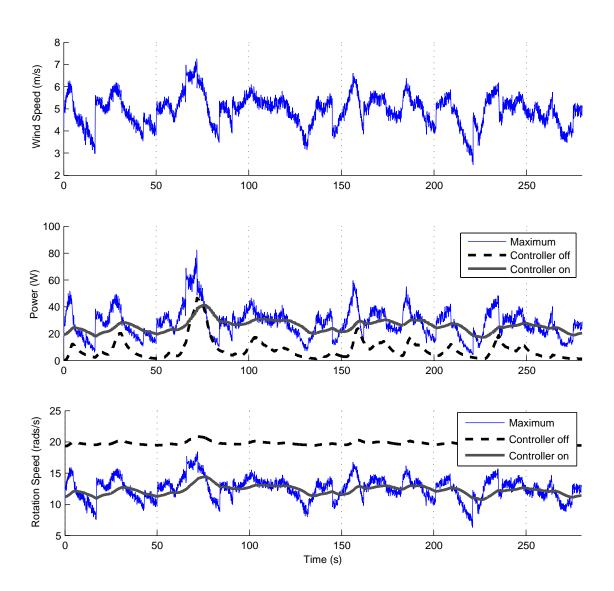

|      | Tracking results for 5m/s average wind speed                                    | 34 |

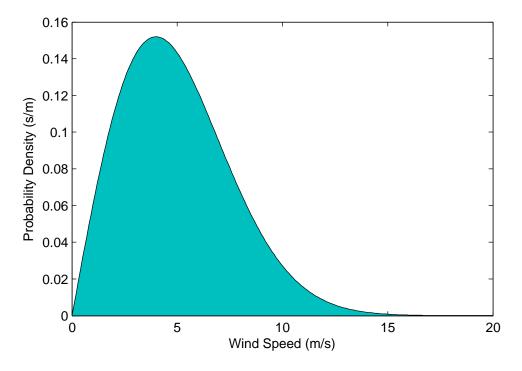

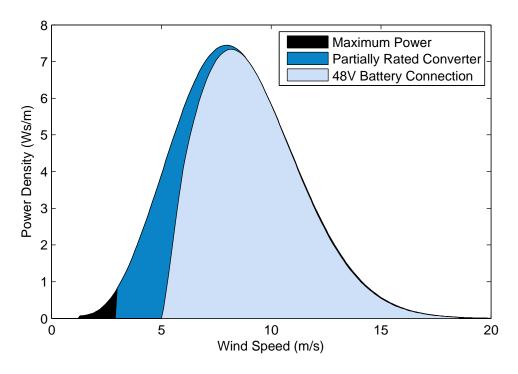

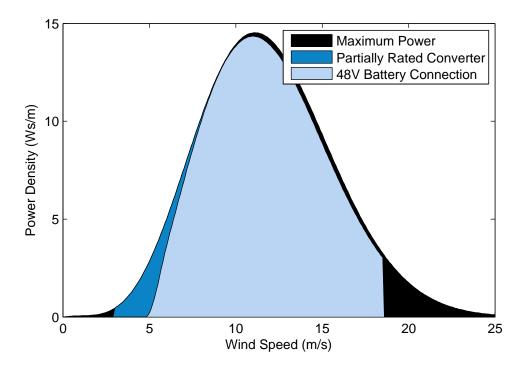

|      | Wind speed distribution for 5m/s average wind speed                             | 35 |

|      | Power density for 5m/s average wind speed                                       | 36 |

|      | Power density for 7m/s average wind speed                                       | 36 |

| 2.20 | Small scale wind turbine grid connection                                        | 39 |

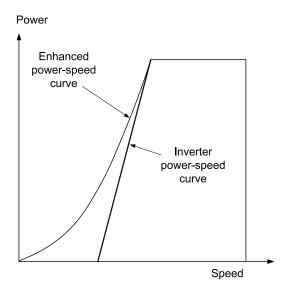

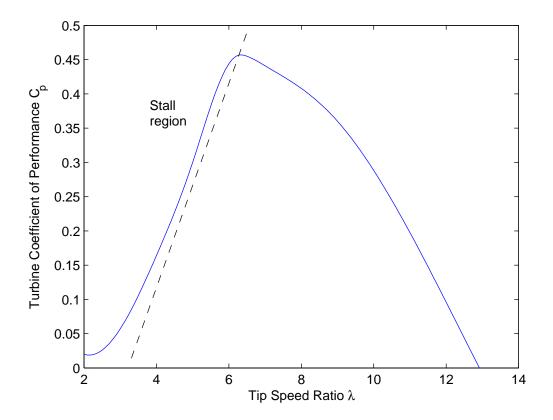

| 3.1  | A $C_p - \lambda$ curve for a stall-regulated wind turbine                      | 42 |

| 3.2  | A $C_p - \lambda$ curve for a pitch-regulated turbine at various pitch angles . | 43 |

| 3.3  | Operating limits for a wind turbine                                             | 45 |

| 3.4  | Wind turbine simple operating region                                            | 46 |

| 3.5  | Power curve for simple operating region                                         | 47 |

| 3.6  | Speed-limited operating region                                                  | 47 |

| 3.7  | Power curve for speed-limited operating region                                  | 48 |

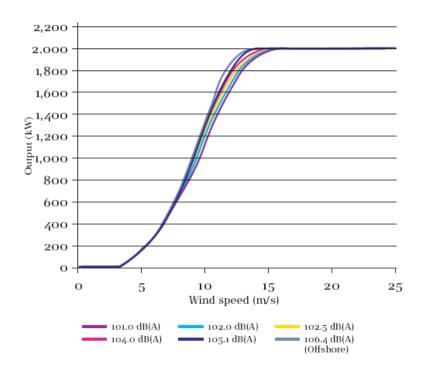

| 3.8  | Power curve for Vestas V80 2MW turbine                             | . 49  |

|------|--------------------------------------------------------------------|-------|

| 3.9  | Torque-limited operating region                                    |       |

| 3.10 | Power curve for torque-limited operating region                    | . 50  |

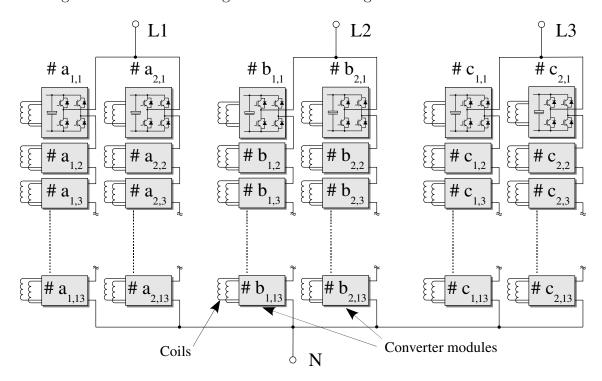

|      | The proposed generator grid interface                              |       |

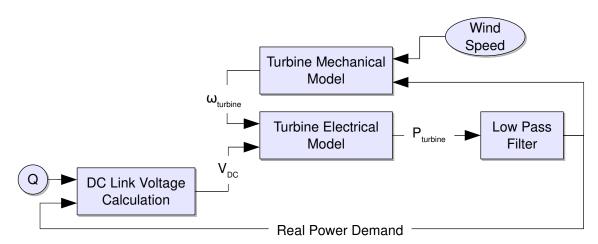

| 3.12 | Converter module connection in greater detail                      | . 52  |

| 3.13 | Simulation model structure                                         | . 55  |

|      | Simulated power curve for diode rectifier connection               |       |

| 3.15 | Simulated turbine speed for diode rectifier connection             | . 57  |

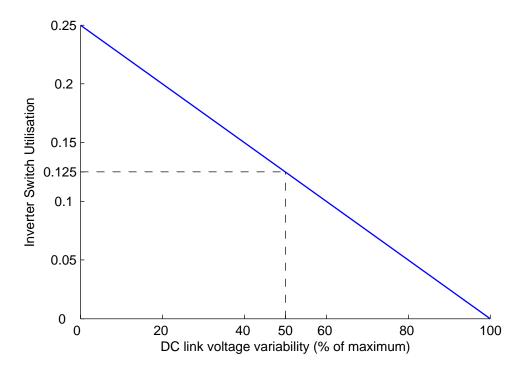

| 3.16 | Switch utilisation for PWM switching of inverter                   | . 59  |

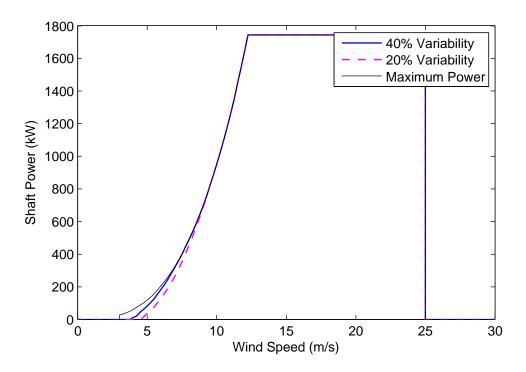

| 3.17 | Simulated power curves for diode rectifier and PWM output          | . 60  |

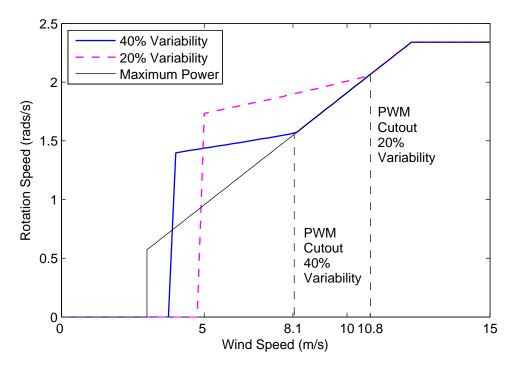

| 3.18 | Simulated turbine speed for diode rectifier and PWM output         | . 60  |

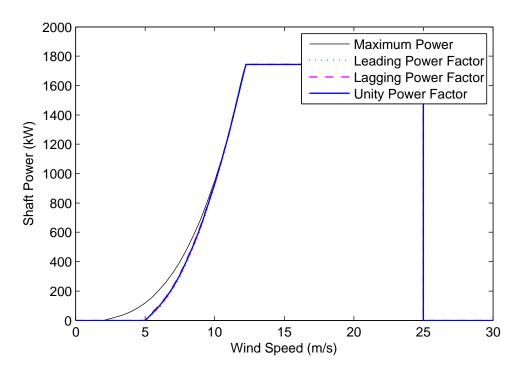

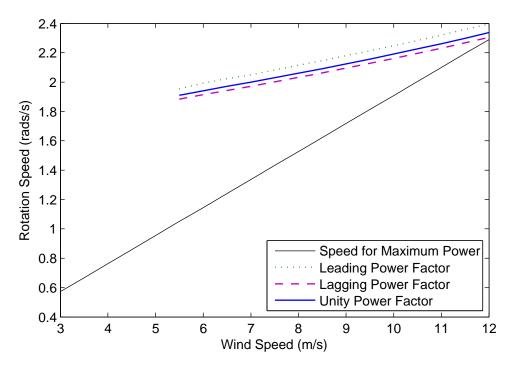

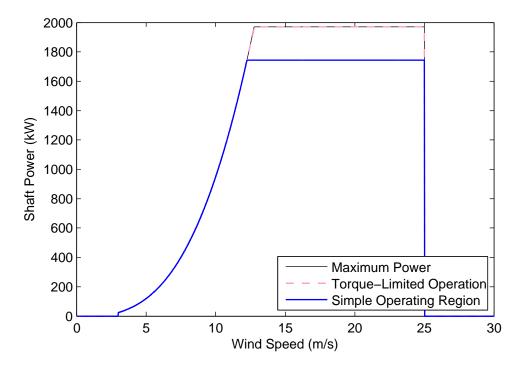

| 3.19 | Calculated power curves for boost rectifier connection             | . 61  |

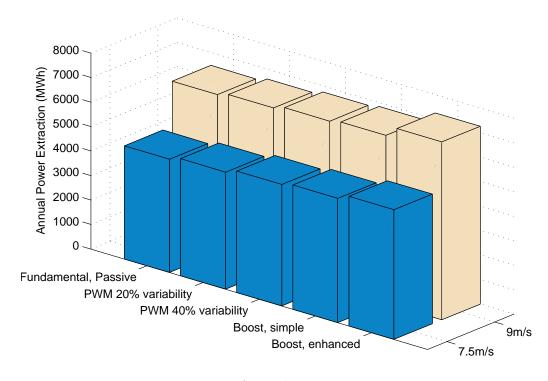

| 3.20 | Annual power extracted                                             | . 62  |

| 4 1  |                                                                    | a =   |

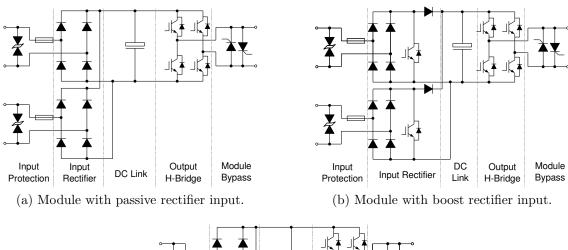

| 4.1  | Module schematic designs                                           |       |

| 4.2  | Rectifier conduction states                                        |       |

| 4.3  | Boost rectifier equivalent circuit                                 |       |

| 4.4  | Boost rectifier equivalent phasor diagram                          |       |

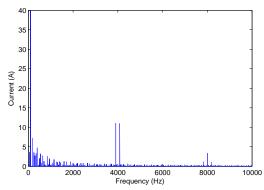

| 4.5  | DC Link capacitor current spectra                                  |       |

| 4.6  | Module cost breakdown                                              |       |

| 4.7  | Module losses                                                      |       |

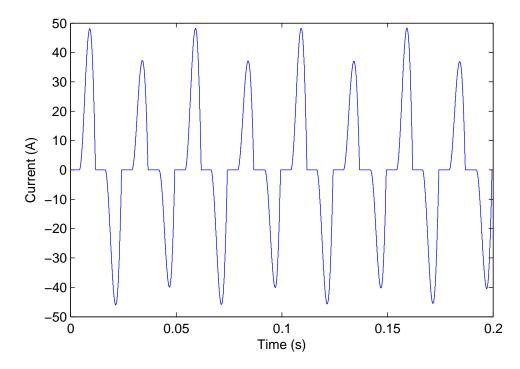

| 4.8  | Distorted passive rectifier coil current, due to DC voltage ripple | . 83  |

| 5.1  | Simplified diagram of the generator structure                      | . 86  |

| 5.2  | Generator Rim Cross Section                                        | . 87  |

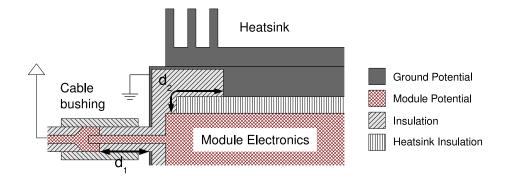

| 5.3  | Power Module Insulation                                            |       |

| 5.4  | Variation of Corona Inception Voltage with Curve Radius            |       |

| 5.5  | Tracking in Insulation of Fully Insulated Module                   |       |

| 0.0  | Tracking in insulation of runy insulated Module                    | . 50  |

| 6.1  | Overall control structure                                          | . 101 |

| 6.2  | Boost rectifier circuit                                            | . 103 |

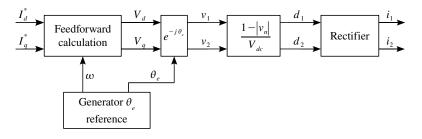

| 6.3  | Rectifier PWM waveform synthesis                                   | . 104 |

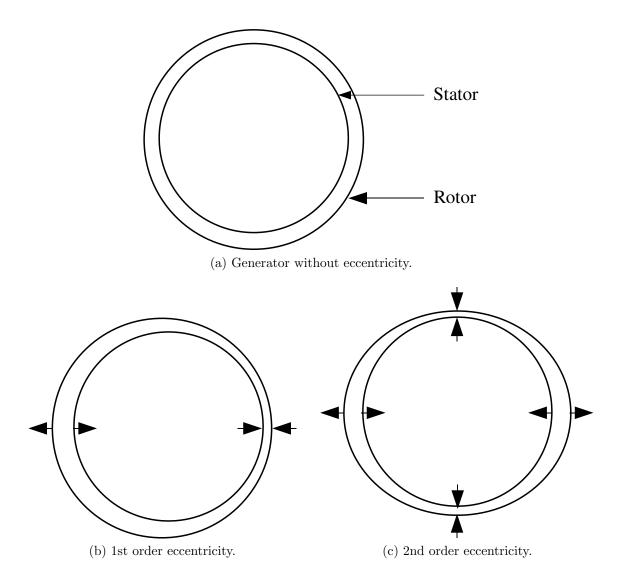

| 6.4  | Generator Eccentricity                                             | . 105 |

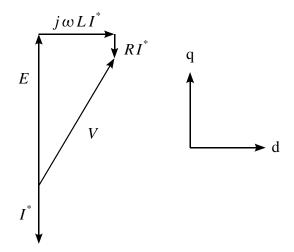

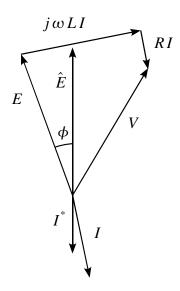

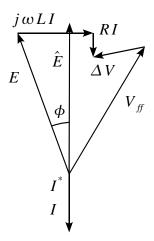

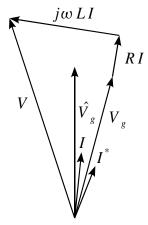

| 6.5  | Boost rectifier phasor diagram                                     | . 106 |

| 6.6  | Basic current controller structure                                 | . 107 |

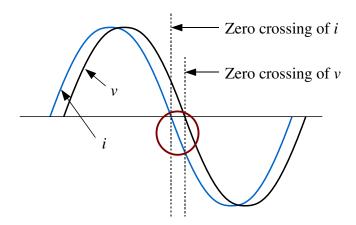

| 6.7  | Current zero-crossing problem                                      | . 108 |

| 6.8  | Improved current controller structure                              | . 109 |

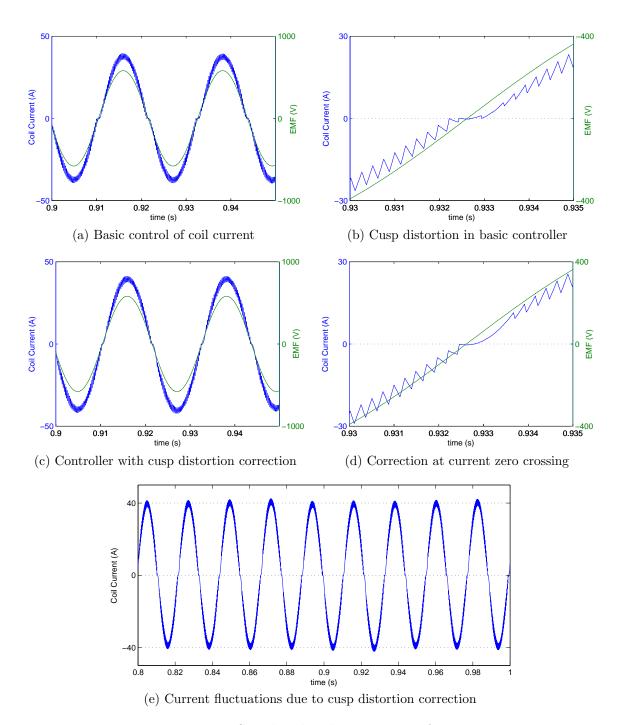

| 6.9  | Simulated coil current waveforms                                   | . 110 |

| 6.10 | Simulated coil current waveforms for improved controller           | . 111 |

| 6.11 | Effects of rotor eccentricity using basic controller               | . 112 |

| 6.12 | Effects of rotor eccentricity using improved controller            | . 113 |

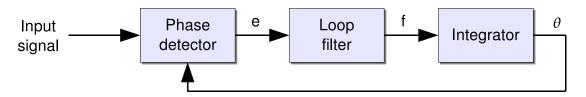

| 6.13 | Basic phaselock loop structure                                     | . 114 |

| 6.14 | Phasor diagram with incorrect EMF estimation                       | . 114 |

|      | Phase detector with EMF estimation                                 |       |

| 6.16 | Phasor diagram with current proportional controller                | . 116 |

|      | Phase detector for current proportional controller system          |       |

|      | Variation of rotor time constant with wind speed                   |       |

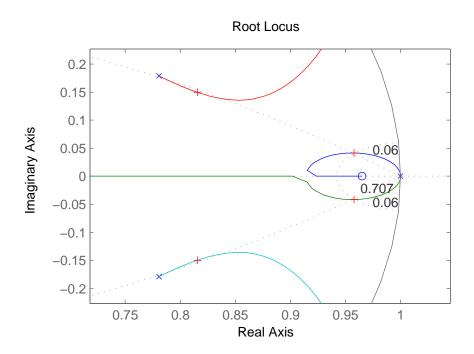

|      | Root locus of PLL system                                           |       |

|      |                                                                    |       |

List of Figures xiii

|            | Response of PLL phase angle estimation to step in phase angle    |       |

|------------|------------------------------------------------------------------|-------|

|            | Simulated rectifier overall control structure                    |       |

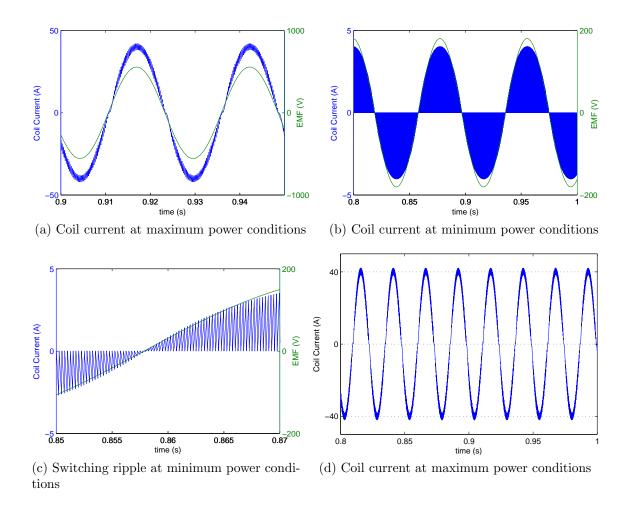

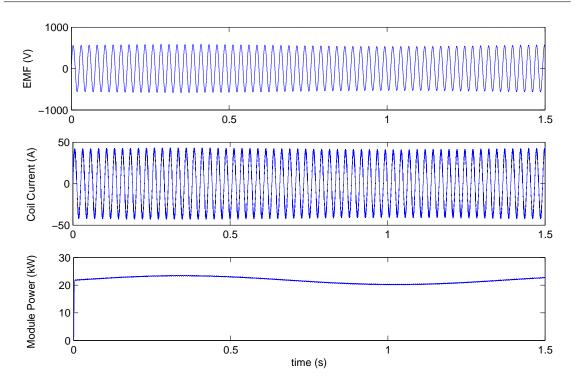

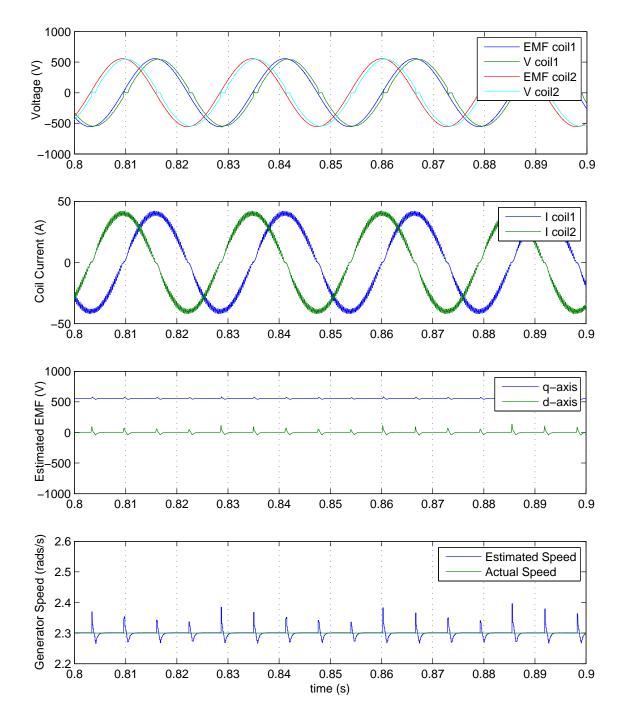

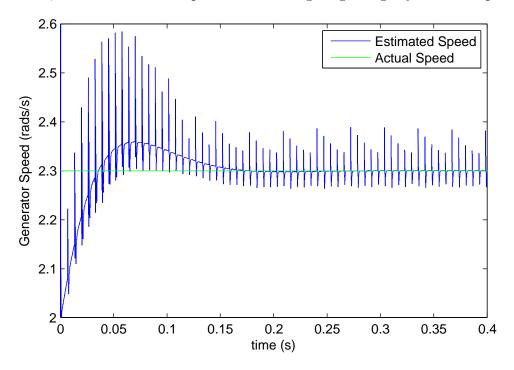

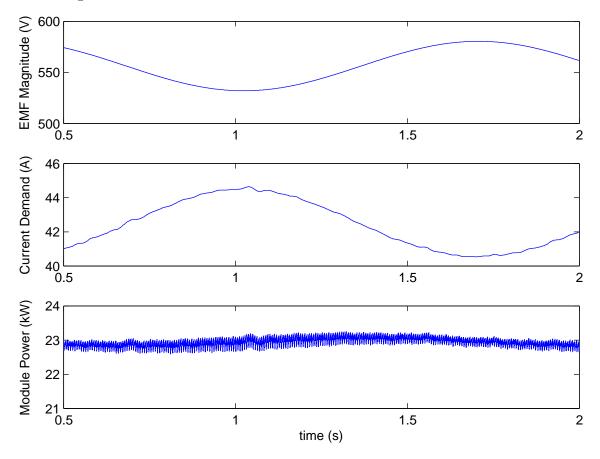

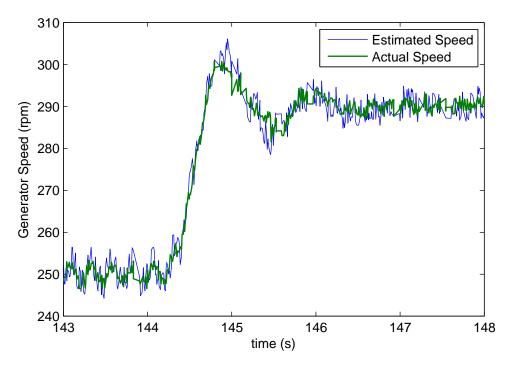

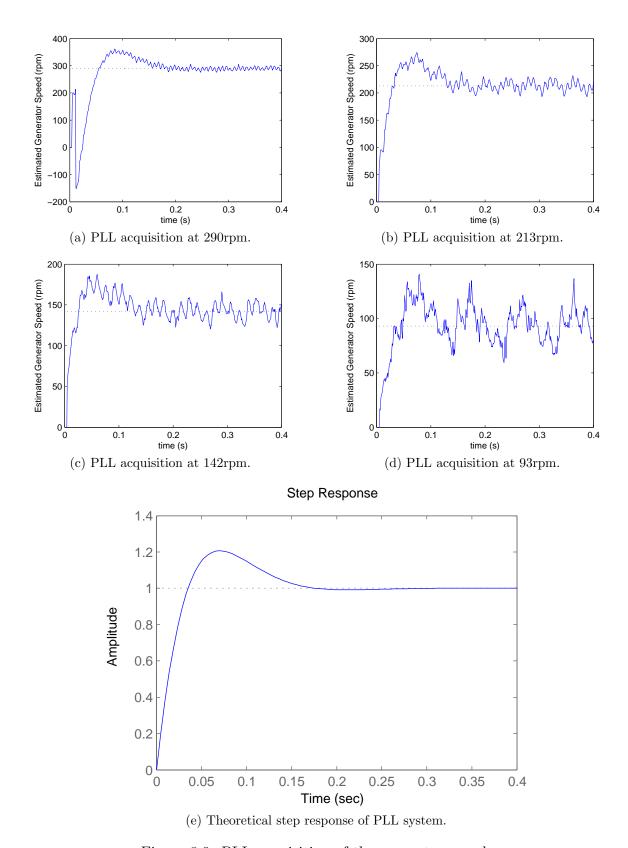

|            | Steady state EMF tracking at maximum power conditions            |       |

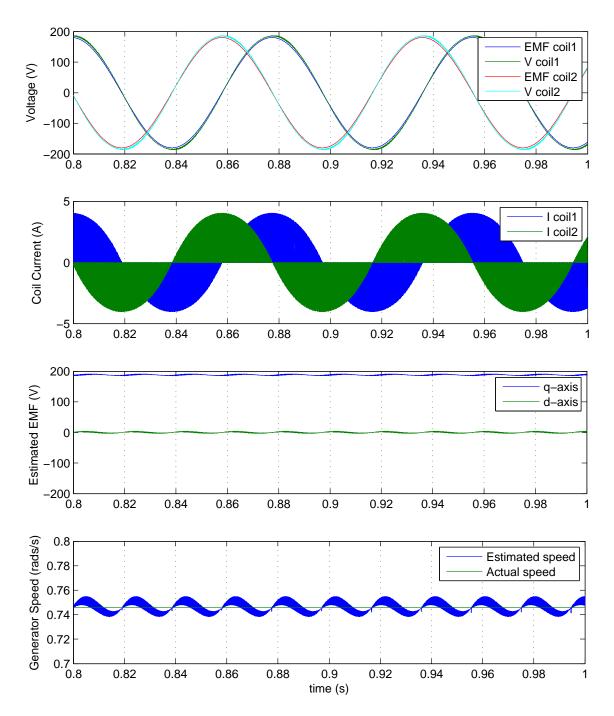

|            | Steady state EMF tracking at minimum power conditions            |       |

|            | EMF tracking step response at maximum power conditions           |       |

|            | EMF tracking step response at minimum power conditions           |       |

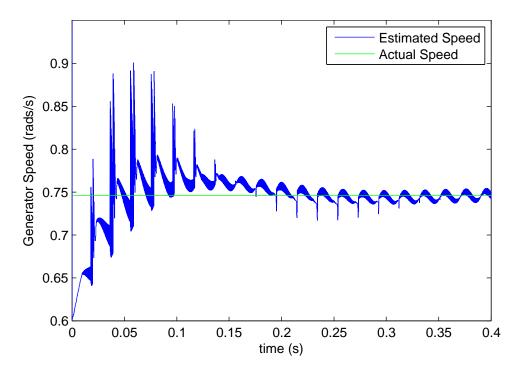

|            | Estimation of EMF magnitude with rotor eccentricity              |       |

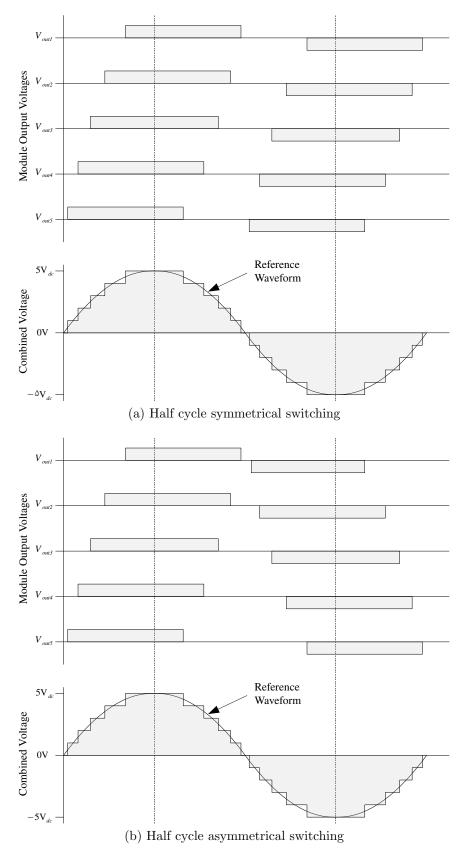

|            | Conventional Inverter Switching                                  |       |

|            | 11-level inverter improved power sharing switching schemes       |       |

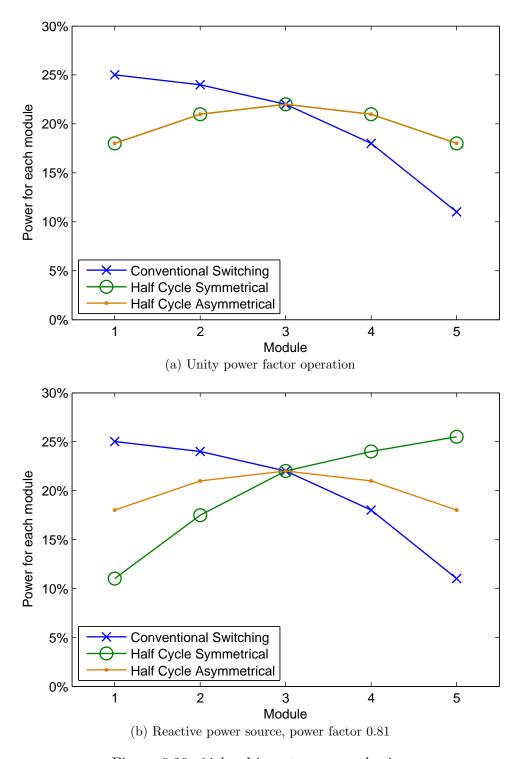

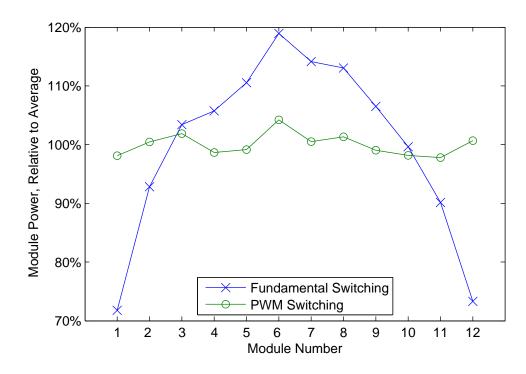

|            | 11-level inverter power sharing                                  |       |

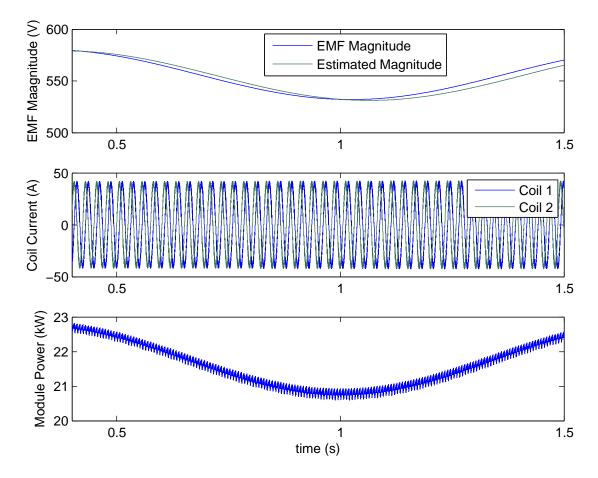

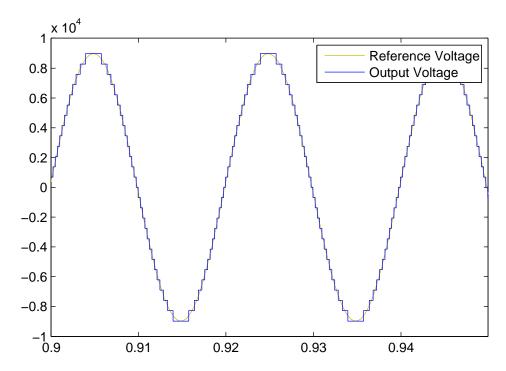

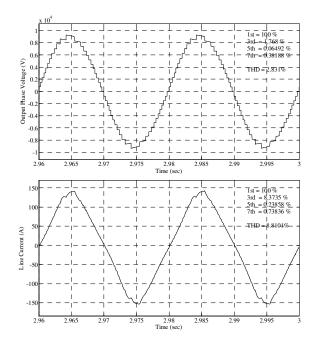

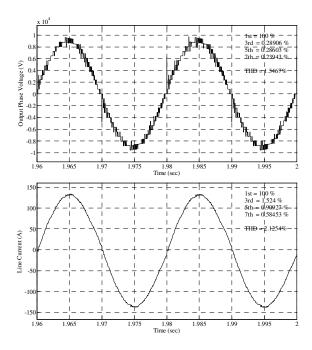

|            | Typical voltage waveform produced by the inverter                |       |

|            | Distorted inverter voltage and current due to DC-link ripple     |       |

|            | Method of synthesising the inverter output signals               |       |

|            | Inverter voltage corrected by distributed active filtering       |       |

|            | DC-Link Model                                                    |       |

|            | DC-Link voltage controller structure                             |       |

|            | Frequency response for 20-step averaging filter                  |       |

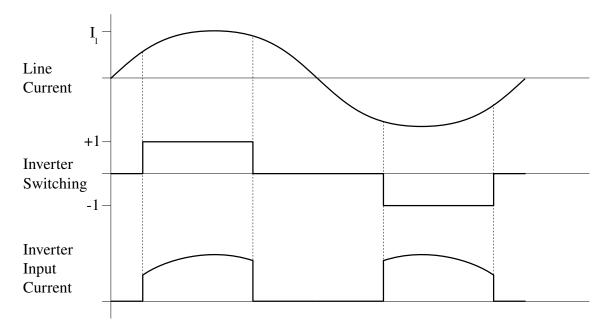

|            | Emulation of inverter current                                    |       |

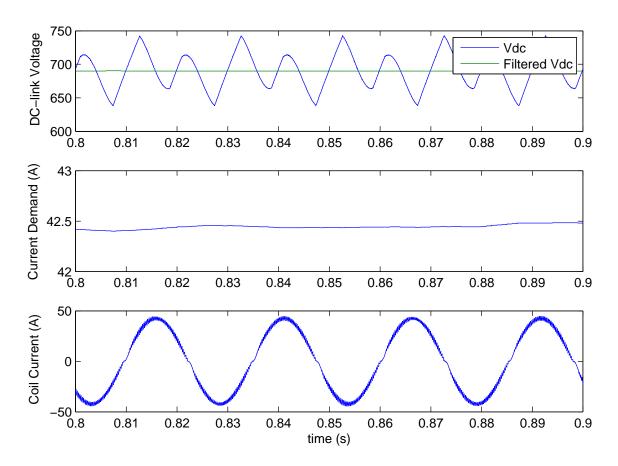

| 6.38       | DC-Link voltage control in the steady state                      | . 137 |

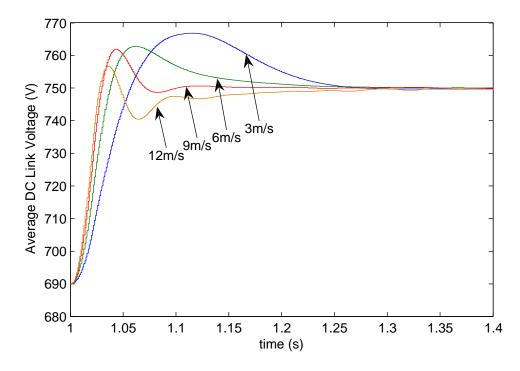

| 6.39       | Response of DC voltage to step in voltage demand                 | . 137 |

| 6.40       | Eccentricity performance with DC-link voltage controller         | . 138 |

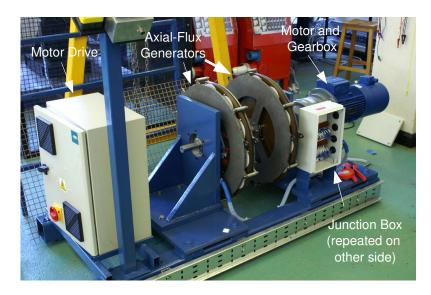

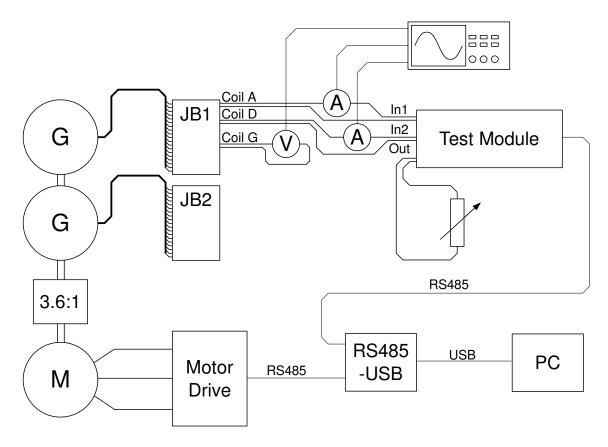

| 7.1        | Motor-generator test rig layout                                  | . 143 |

| 7.2        | Overview of power module rack system                             | . 145 |

| 7.3        | Diversion of ground currents around sensitive system             | . 147 |

| 7.4        | Test system power module schematic                               | . 149 |

| 7.5        | Prototype power board                                            |       |

| 7.6        | Evaluation of power board thermal performance                    |       |

| 7.7        | Final power board design, without control board                  | . 153 |

| 7.8        | Communication architectures between the controller and modules   |       |

| 7.9        | The Modbus serial data unit                                      | . 157 |

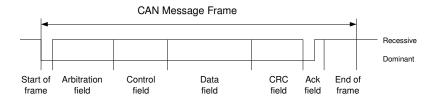

| 7.10       | CAN standard message frame                                       |       |

|            | Control board layout                                             |       |

|            | Module ground map                                                |       |

|            | Complete module with control board                               |       |

|            | Diagram of the complete test system                              |       |

|            | Layout of the power electronics rack                             |       |

|            | Central controller program structure                             |       |

|            | Structure of the rectifier controller                            |       |

|            | Rectifier PWM, ADC and interrupt timing.                         |       |

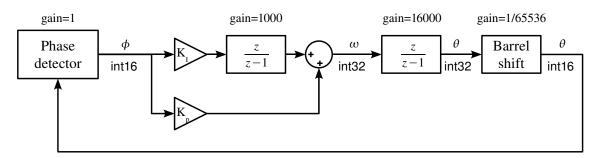

|            | Phaselock-loop gains and variable types                          |       |

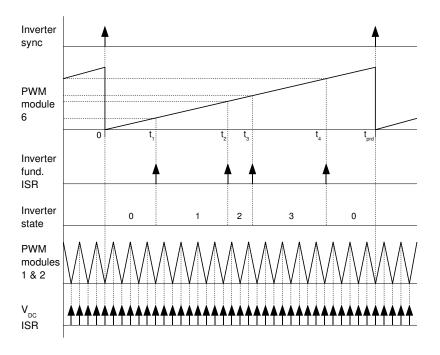

|            | Inverter PWM and state transitions                               |       |

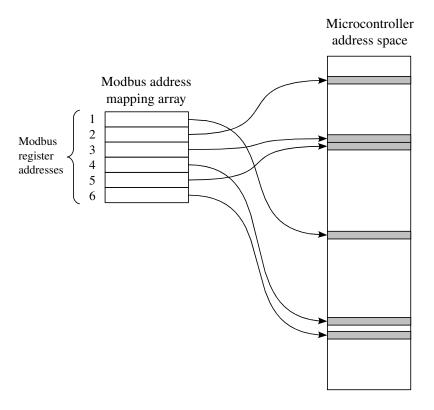

|            | Mapping of Modbus table entries to microcontroller memory space. |       |

| 8.1        | Rectifier test arrangement                                       |       |

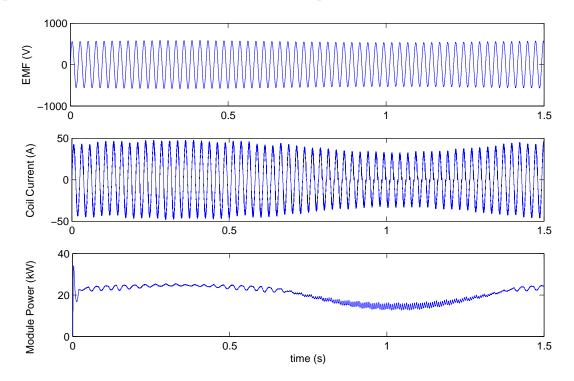

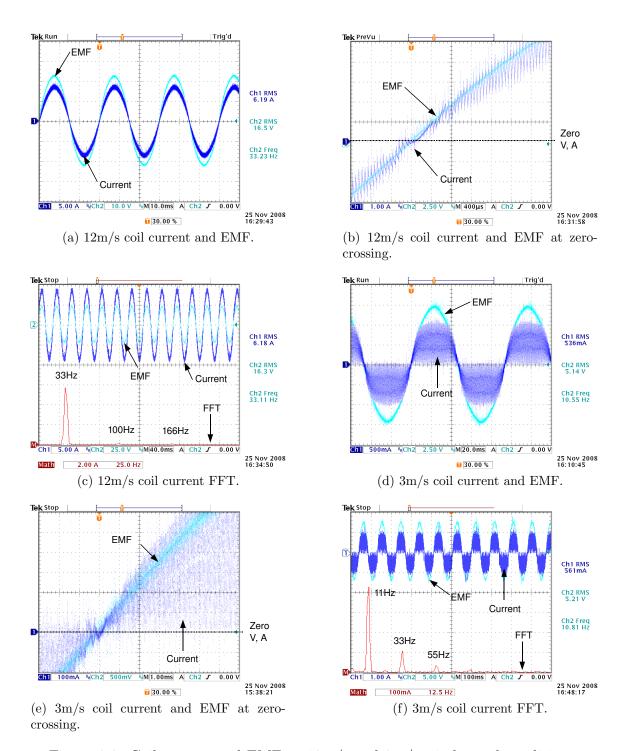

| 8.2        | Coil current and EMF at 12m/s and 3m/s wind speed conditions     |       |

| 8.3        | Coil current and EMF at 6m/s and 9m/s wind speed conditions      |       |

| $\circ$ .0 | con carroin and Diff at only and only a wind speed conditions    | . 104 |

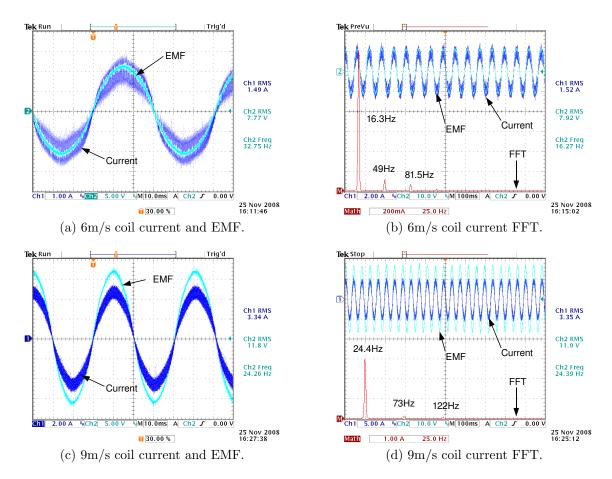

| 8.4        | Steady state EMF tracking at 12m/s wind condition                | . 185 |

|------------|------------------------------------------------------------------|-------|

| 8.5        | Steady state EMF tracking at 3m/s wind condition                 | . 186 |

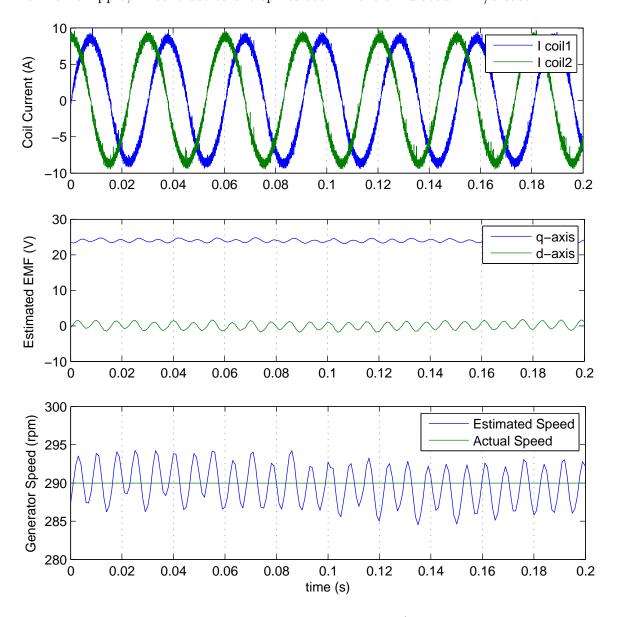

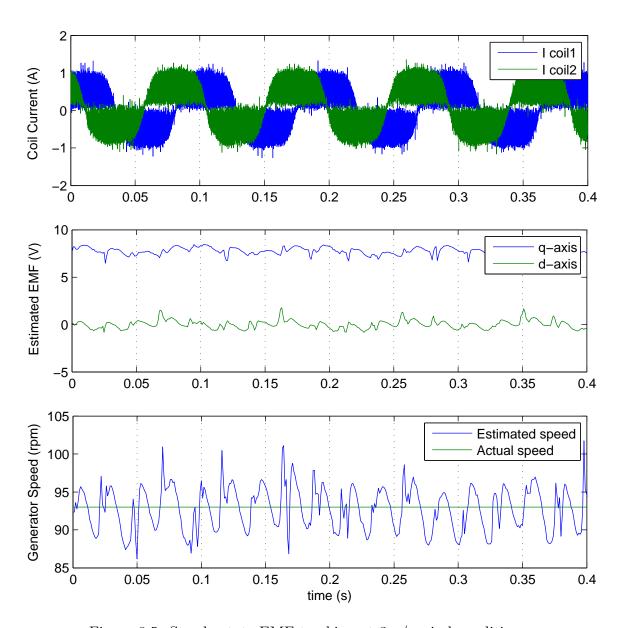

| 8.6        | Response to a step change in speed demand, 12m/s wind condition. | . 187 |

| 8.7        | Response to a step change in speed demand, 3m/s wind condition   | . 188 |

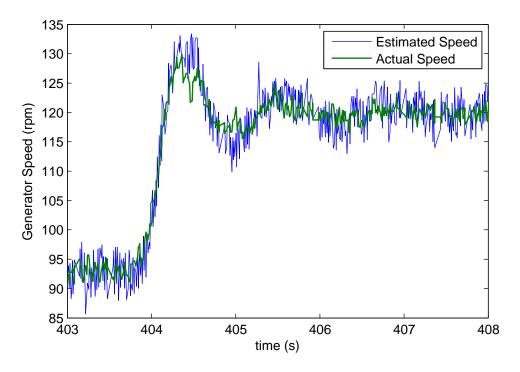

| 8.8        | EMF acquisition using coil current sensors                       |       |

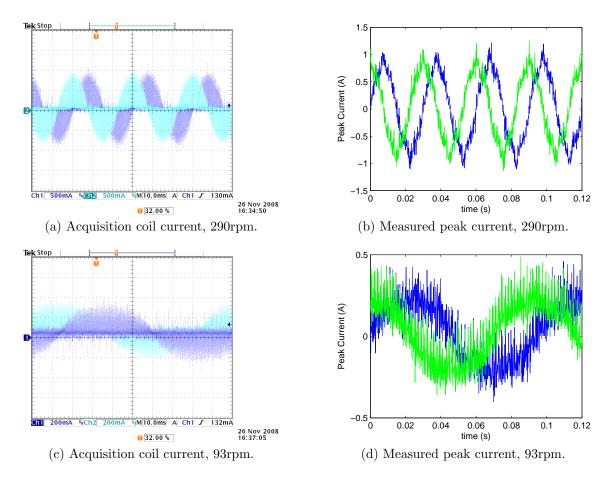

| 8.9        | PLL acquisition of the generator speed                           | . 191 |

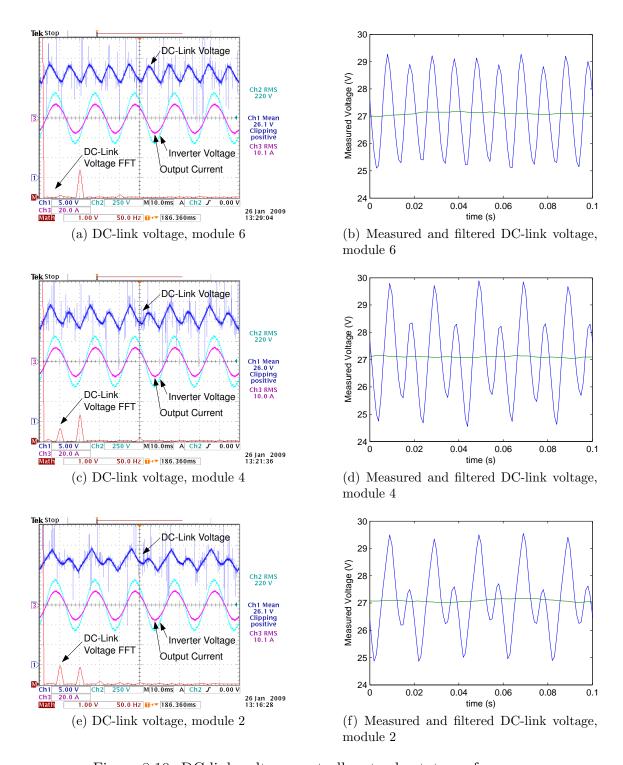

| 8.10       | DC-link voltage controller steady state performance              | . 192 |

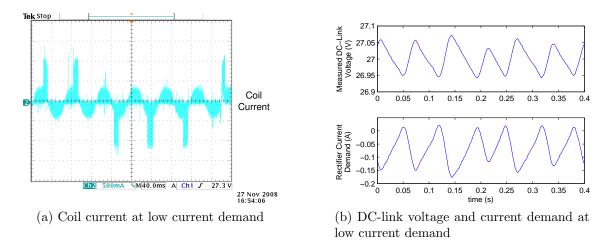

|            | Low current demand condition, steady state                       |       |

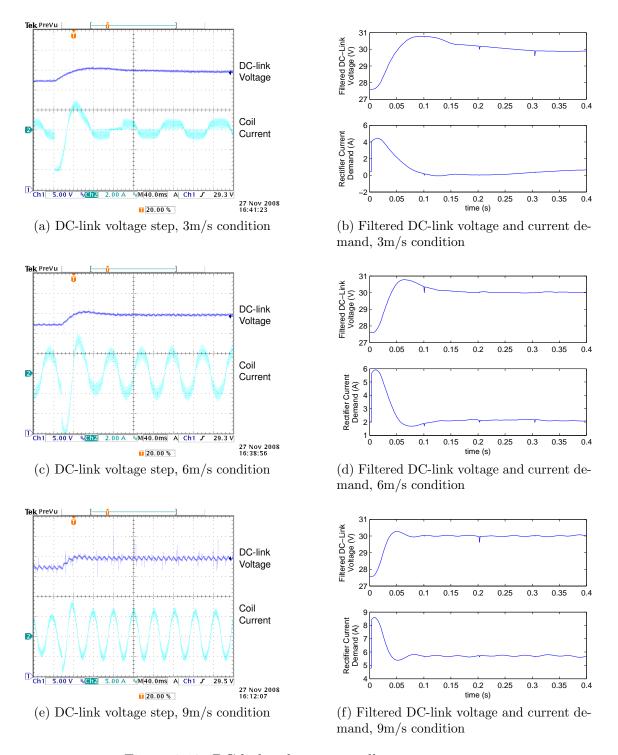

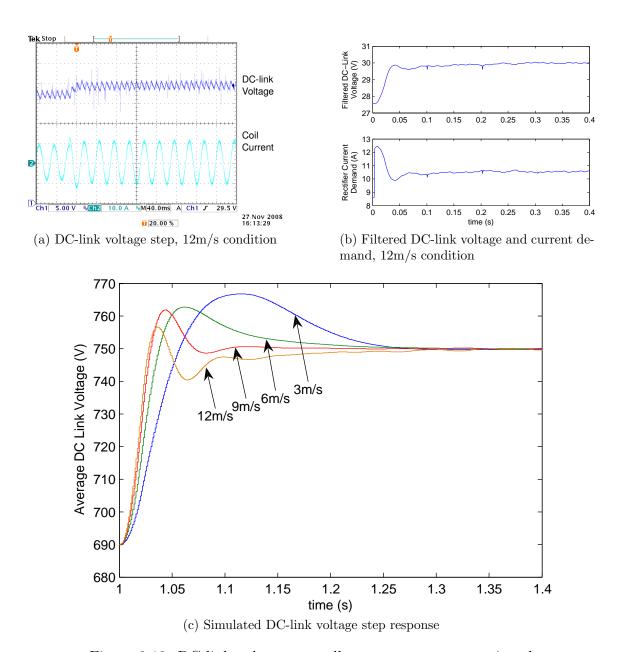

| 8.12       | DC-link voltage controller step responses                        | . 195 |

| 8.13       | DC-link voltage controller step responses, continued             | . 196 |

| 8.14       | Inverter output current and voltage, resistive load              | . 198 |

| 8.15       | Inverter output $V,I,$ grid connection, unity power factor       | . 200 |

| 8.16       | Inverter output $V,I,$ grid connection, reactive power           | . 201 |

|            | Inverter power sharing                                           |       |

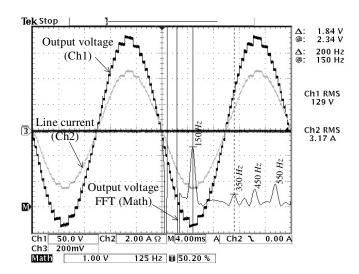

|            | Inverter voltage harmonic distortion correction                  |       |

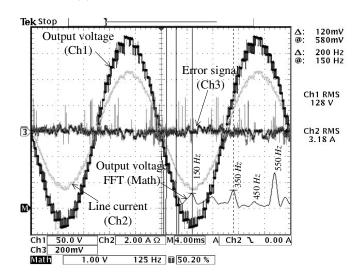

|            | Inverter V,I, waveforms with and without module faults           |       |

| 8.20       | Inverter response to a sudden module fault                       | . 206 |

| 9.1        | Interleaved inverter PWM carrier waveforms                       | 010   |

|            |                                                                  |       |

| 9.2<br>9.3 | Synchronisation and interleaving of PWM carrier waveforms        |       |

| 9.3<br>9.4 | CAN activity due to PWM interleaving process                     |       |

| 9.4        | Grid angle reference PLL structure                               |       |

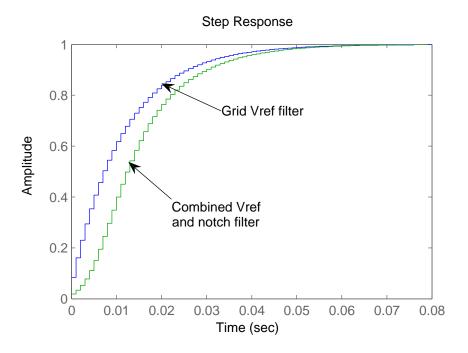

| 9.6        | Grid voltage reference filter structure                          |       |

| 9.7        | Synchronisation of Inverter Grid Reference                       |       |

| 9.1        | Inverter voltage waveform                                        |       |

| 9.9        | Inverter voltage wavelorm                                        |       |

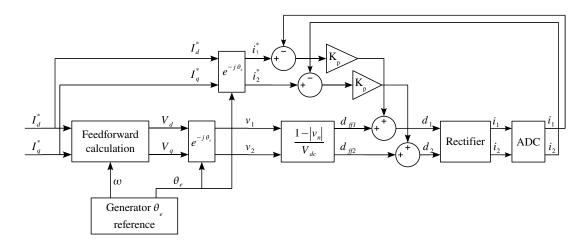

|            | Inverter current controller structure                            |       |

|            | Simulation structure of single module                            |       |

|            | Inverter simulation structure                                    |       |

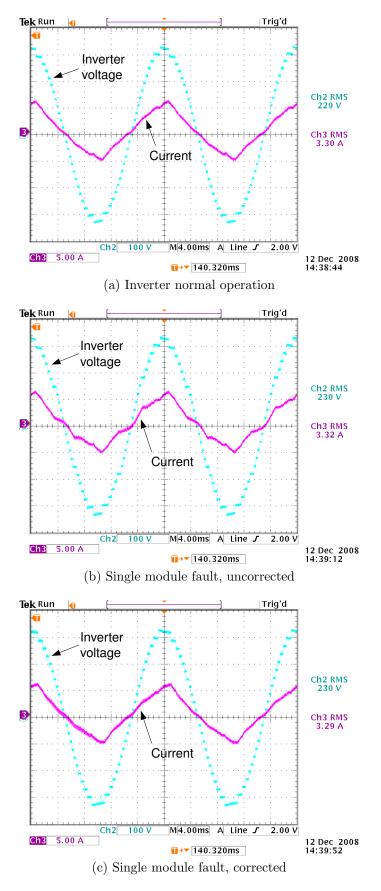

|            | Simulated inverter voltage and current, normal operation         |       |

|            | Simulated inverter voltage and current, find fault conditions    |       |

|            | Inverter V,I, with short circuit and different Kp values         |       |

|            | Inverter voltage and current, emulated grid fault conditions     |       |

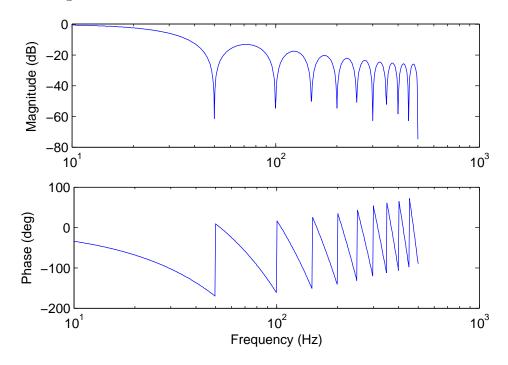

|            | 100Hz notch filter frequency characteristics                     |       |

|            | Inverter phasor diagram                                          |       |

|            | Inverter grid voltage estimation loop and current controller     |       |

|            | Root locus of grid reference PLL                                 |       |

|            | Detail of grid reference PLL root locus                          |       |

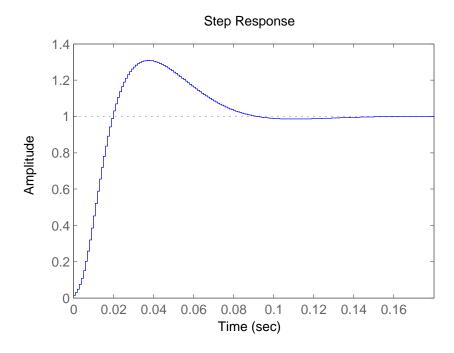

|            | Grid PLL step response                                           |       |

|            | Grid voltage reference step response                             |       |

|            | Locking of inverter onto grid voltage                            |       |

|            | Inverter V,I, grid connection, current limiting                  |       |

|            | Inverter current limiting, with unstable Kp value                |       |

|            | Inverter V,I, grid connection, normal operation                  |       |

|            | Inverter grid fault ridethrough                                  |       |

|            | Inverter module power sharing                                    |       |

|            | - ~ ~                                                            |       |

List of Figures xv

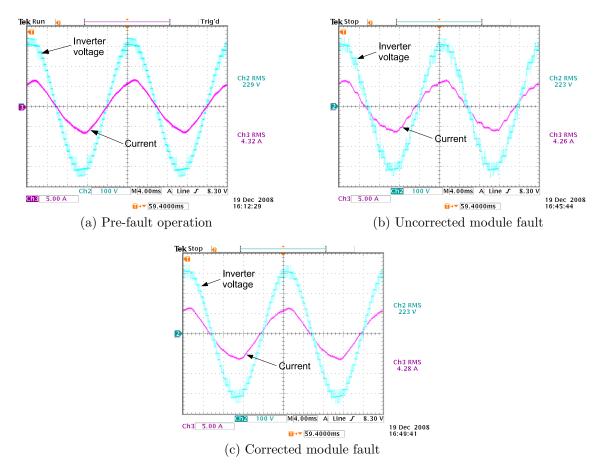

|     | Inverter V,I, waveforms with and without module faults              |

|-----|---------------------------------------------------------------------|

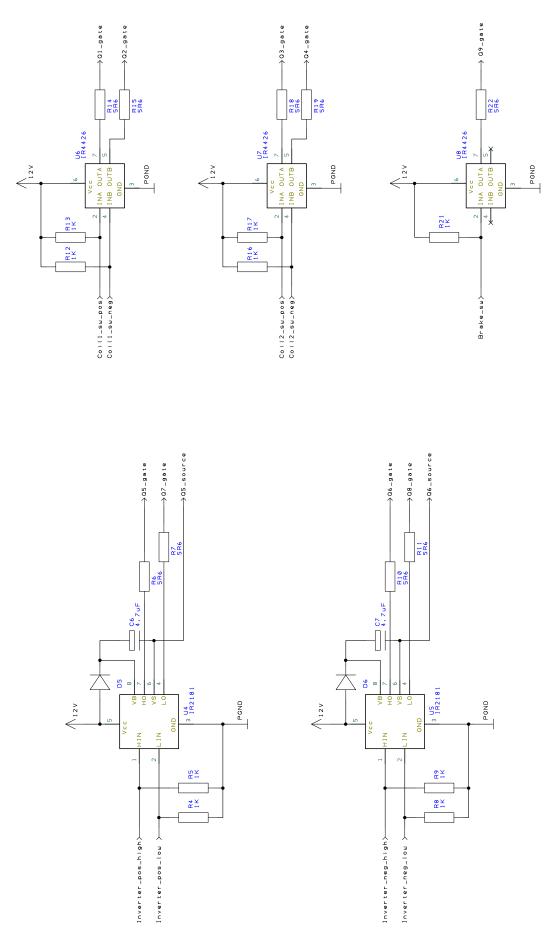

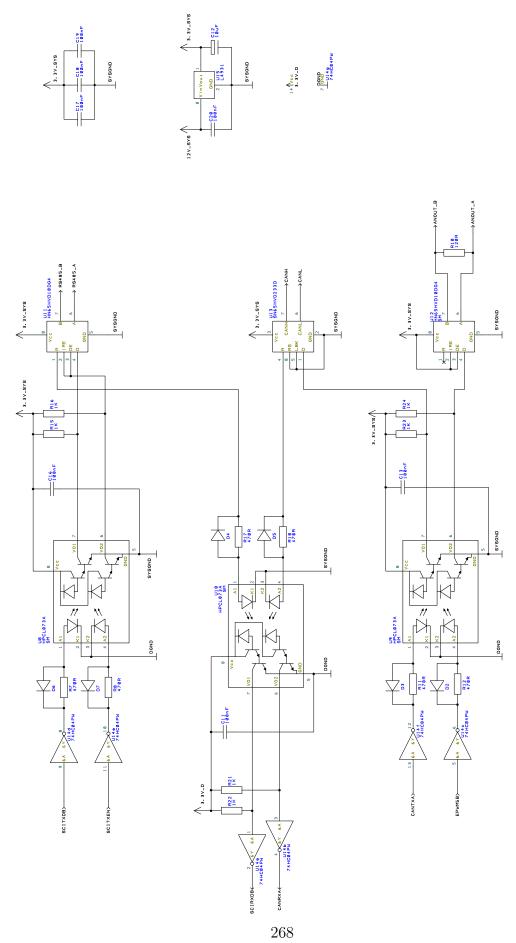

| B.1 | Power processing part of the electrical board                       |

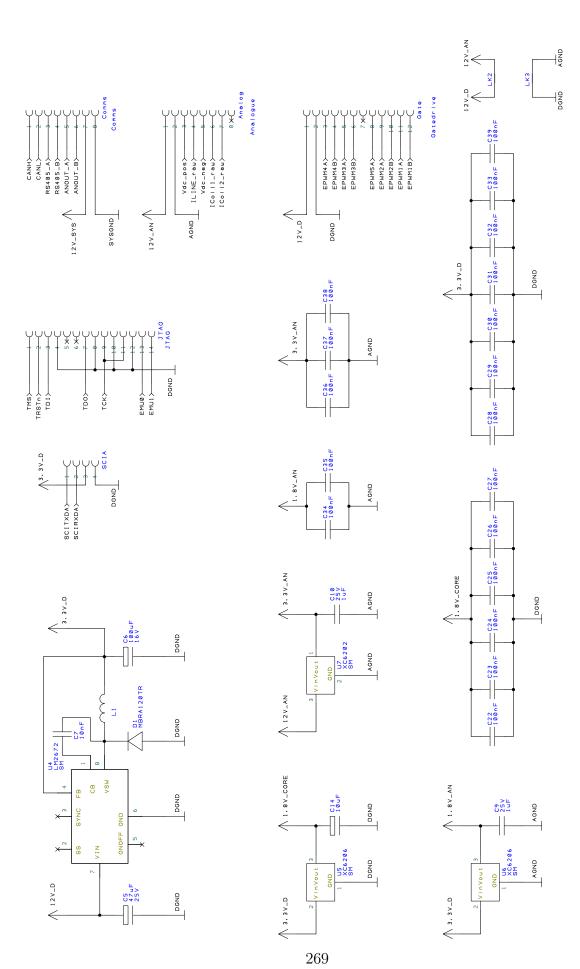

| B.2 | Electrical board MOSFET gate drivers                                |

| B.3 | Electrical board inputs and outputs                                 |

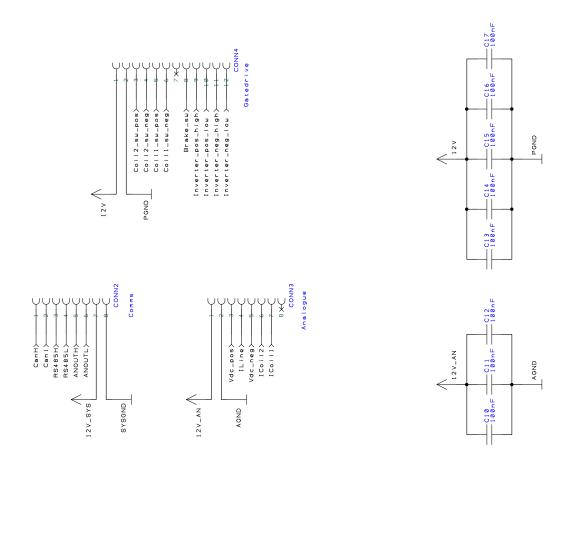

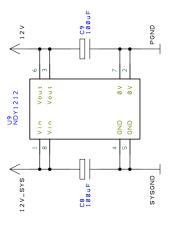

| B.4 | Main components of the controller board                             |

| B.5 | Isolated communications section of the controller board 268         |

| B.6 | Power supply and decoupling capacitros for the controller board 269 |

# List of Tables

| 2.1  | Turbine characteristics                            | 17     |

|------|----------------------------------------------------|--------|

| 2.2  | Generator characteristics                          | 17     |

| 2.3  | Turbine operating range                            | 25     |

| 2.4  | Average power extracted                            | 32     |

| 2.5  | Annual energy capture                              | 37     |

| 2.6  | Comparison of partially and fully rated converters | 37     |

| 3.1  | Generator Parameters                               | 54     |

| 3.2  |                                                    | 54     |

| 3.3  | Annual power extracted                             | 62     |

| 4.1  | Inverter DC-link voltage                           | 73     |

| 4.2  |                                                    | 73     |

| 4.3  | ŭ ŭ                                                | 74     |

| 4.4  | 0 0                                                | 75     |

| 4.5  |                                                    | 76     |

| 4.6  | 1                                                  | <br>78 |

| 4.7  |                                                    | <br>78 |

| 4.8  |                                                    | 80     |

| 4.9  | ,                                                  | 81     |

| 4.10 |                                                    | 82     |

| 5.1  | Comparison of encapsulation compounds              | 92     |

| 6.1  | Turbine operating conditions                       | 35     |

| 7.1  | System Parameters                                  | 44     |

| 7.2  | Estimated switching device losses                  |        |

| 7.3  | Range and calibration of various quantities        |        |

| 7.4  | Inverter output settings and states                |        |

| 7.5  | Inverter module switch-on times                    |        |

| 7.6  | Switching angle calculation                        |        |

| 8.1  | Turbine operating conditions for rectifier testing | 81     |

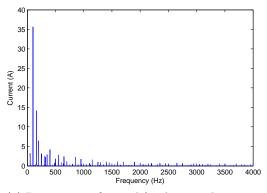

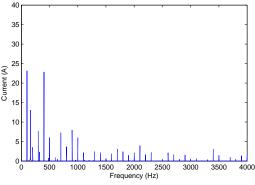

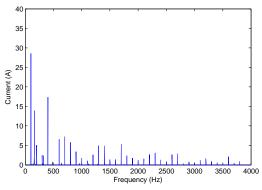

| 8.2  | Coil current harmonic to fundamental ratios        |        |

| 8.3  | Coil inductance variation with magnet alignment    |        |

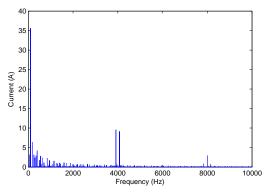

| 8.4  | DC-link voltage harmonic content                   |        |

| 8.5  | Turbine operating conditions for inverter testing  |        |

| 9.1  | Current controller proportional gains used         | 38     |

# Chapter 1

## Introduction

The birth of the modern wind turbine is considered by many to have occurred in 1957 with the 200kW Gedser turbine [1], shown in Figure 1.1, which featured a 3-bladed upwind turbine, driving a cage rotor induction machine through a step up gearbox, and featuring electromechanical yaw control. Until the mid 1990's, most turbines were based on this "Danish Concept".

Figure 1.1: The Gedser wind turbine [2]

The generator was connected directly to the electricity grid, usually with a capacitor bank for reactive power compensation and often through a soft starter. This resulted in an almost fixed speed operation, meaning that any gusts in the wind would result in a sudden spike in the electrical power output. This required a stiff grid in order to maintain stability and also resulted in high mechanical stresses to the turbine drive train [3]. Blade pitch control was added to turbines in order to reduce the generator torque at high wind speeds but the time constant of the pitch control mechanism was usually too slow to compensate for gusts. Such limitations increased the interest in variable speed wind turbines. Variable speed operation offers the following advantages:

- The turbine inertia can be used to smooth the mechanical forces in the drive train, so the energy of the gust will cause the turbine rotation speed to increase temporarily instead of being transferred onto the grid.

- In a similar fashion, the turbine power output is smoothed, which is of benefit to the operators of the electricity network.

- Power capture is increased at lower wind speeds as the turbine speed can be matched to the wind speed and so track the maximum power point of the system.

- Acoustic noise is reduced at lower wind speeds by the lower rotation speed of the turbine.

#### 1.1 Variable Speed Concepts

#### 1.1.1 Geared Doubly Fed Induction Generator

The most widely used method of achieving variable speed is to use a Doubly-Fed Induction Generator (DFIG), shown in Figure 1.2a, and Figure 1.3, in which the stator of a wound rotor induction machine is connected directly to the grid, while the rotor is connected via a 4-quadrant ac-ac converter. The converter is typically rated at around 25% of the turbine output, and allows a speed variation of around ±33% from the synchronous speed [3]. The generator is typically a 6-pole unit, with a synchronous speed of 960rpm, and is connected to the turbine hub through a step up gearbox. The generator and converter are standard industrial parts, which has contributed to an increase in reliability and reduction in cost of wind turbine systems.

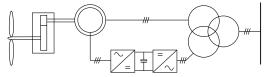

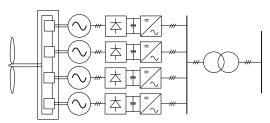

(a) Geared drivetrain with doubly-fed induction generator and transformer interface.

(c) Direct drive generator with four fully-rated converters and transformer interface.

(b) Geared drive train with permanent magnet generator, fully rated converter and transformer interface.

(d) Clipper concept – geared drive train with multiple generators and fully rated converters.

Figure 1.2: Turbine Drive Systems

Figure 1.3: A Nordex wind turbine, using a geared generator [4]

Reliability of the geared turbine system is generally high, due to the use of a standard industrial generator and converter, although the generator brushes need to be maintained. The gearbox is one of the less reliable parts, generally as wind turbine gearboxes tend to be specialised parts [5]. Scaling turbines to larger sizes results in a lower rotation speed, which increases the gear ratio required to achieve the rated speed of the generator. This has resulted in an increase in the number of stages in the gearbox, usually 3 for large turbines, as well as the gearbox size, which reduces the turbine efficiency and gearbox reliability.

The increase in the size of the turbines has meant that the current in the generator connection cables has increased as the voltage has remained static at 690V. This is a problem in a DFIG-based system where the transformer and converter are usually housed in the base of the tower in order to reduce the weight of the nacelle. This means that several high current cables must be passed down the entire height of the tower.

A further issue with the DFIG-based system is in it's ability to ride through grid faults. A generator without power electronics is able to ride through faults because the generator is designed to withstand the high currents that occur for a short period of time when the grid voltage collapses. A power electronic interface must limit the current by reducing the modulation depth of the output as the power device thermal inertia is too low to allow it to withstand high over-currents, which is desired to operate protection relays.

#### 1.1.2 Direct Drive Synchronous Machine

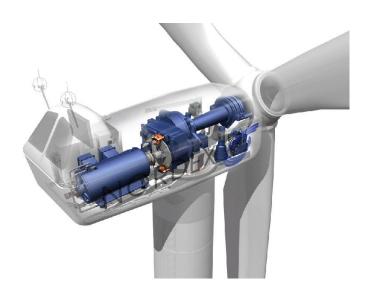

The use of a slow speed direct drive generator, as in Figure 1.2c, eliminates the need for a gearbox in the turbine, increasing efficiency and eliminating a source of unreliability. Enercon is the main producer of direct drive turbines and produce models up to 2.3MW in size along with a prototype capable of producing up to 6MW. Some examples of direct drive machines are shown in Figure 1.4.

The generator most used in direct drive turbines is the wound field synchronous machine, similar to what is used in conventional power generation. Variable speed is achieved by using a fully-rated direct in line ac-ac converter, which is more expensive than the partially rated converter of the DFIG system. Fault tolerance can be achieved by using several small converters instead of one large one – the loss of one

Figure 1.4: Some Direct Drive Turbines

small converter will result in a reduction in maximum power output but the turbine will still produce power. The fully-rated converter typically allows a greater range in turbine speeds than the DFIG system, increasing power capture at low wind speeds. The Enercon E70, shown in Figure 1.4a, uses this type of generator.

Machines using permanent magnets instead of electrical excitation have also been designed [8], which offer an improvement in efficiency and a reduction in complexity compared with electrical excitation. However the magnets used are expensive and the generator is more difficult to manufacture due to the permanent force of attraction between the rotor and stator. The Zephyros Z72, shown in Figure 1.4b, uses this type of generator. An induction generator of this size would be impractical for direct drive, as the larger air gap of a large diameter machine would result in a high leakage flux, and thus a high magnetising current [1].

Low speed slotted synchronous machines are often used in marine propulsion and hydroelectric generation, and these typically have a rated speed of around 100-200rpm with 30-60 poles and power ratings up to hundreds of MW. By contrast, the Enercon E82 is rated at 2MW and rotates at up to 19.5rpm, and would require a 300-pole generator to achieve 50Hz output. This leads to a very small pole pitch as well as a large generator diameter, while retaining the small airgap used in high speed machines, leading to high air gap closing forces. Because of the high air gap forces, a very strong and stiff structure is required in order to maintain the air gap

size. A geared system typically has a specific weight of around 10kg/kW for the generator and gearbox, while present direct drive systems have a specific weight of 20-30kg/kW [1].

The multipole generator system is complicated and expensive to manufacture, and has been shown to be less reliable than the DFIG-based system which uses standard parts [5]. The converter has also been shown to be less reliable, but the absence of a gearbox means that overall reliability is similar to that of the DFIG system. Cost is also increased due to the fully-rated converter, although the systems using permanent magnets instead of electrical excitation offer even greater efficiency but at higher cost. Fault ride-through capability is improved, due to the fully-rated converter that interfaces directly to the grid, as is operation in weak grids. Efficiency is higher due to the removal of the gearbox, while power capture is improved by the increased speed range.

#### 1.1.3 Alternative Systems

Wind turbine systems have been developed which use a fully-rated converter and a high speed induction or permanent magnet synchronous generator connected through a gearbox, shown in Figure 1.2b. Such systems are not widespread due to the increased cost of the converter compared with the DFIG system, while still including a gearbox. One system has been introduced by the manufacturer Clipper, which uses a step-up gearbox driving four permanent magnet generators at 1133rpm rated speed, with each generator having it's own power converter, shown in Figure 1.2d. Advantages are claimed in fault tolerance and grid fault ride through capability, although the turbine is primarily marketed for remote areas with weak grid connections and long fault clearance times.

It is anticipated that as power electronic converters become more compact and economical, concepts including fully-rated converters will become more attractive while the DFIG, suffering from problems with fault ride through and reliability of the brushes and slip rings, would gradually fade away in newly built wind turbines.

A potential solution for the scalability issues of current designs is to use a medium speed generator, operating at around 100-200rpm, and a single stage gearbox [9]. The generator would be smaller than a typical direct drive generator, and much more similar to conventional designs, while the single stage gearbox would be more

reliable and lighter. Further weight improvements could be achieved by integrating the gearbox, generator and low-speed bearing.

All the concepts detailed above are connected to the grid using a step up transformer, located either in the base of the turbine or the nacelle. The grid voltage is typically 11-33 kV and the generators typically output power at 690V. Systems using industrial medium voltage converters have been designed [10], although these are more expensive due to the higher cost of high voltage power semiconductor devices.

#### 1.2 Turbine Scalability

Perhaps the biggest trend in the wind industry is the move towards greater numbers of offshore turbines. Onshore turbines are limited in size by site access and transportation, and few turbines larger than 3MW are in operation onshore. There is less of a transportation issue offshore, while the cost of installation, foundations and electrical connection is much greater per turbine. For this reason the offshore industry is driving the building of larger turbines.

While reliability is important onshore, it is even more important offshore where access to the turbine for maintenance is significantly more difficult and expensive. It is clear that both of the current mainstream turbine designs suffer from reliability issues, which need to be solved in order to make offshore wind power competitive with other forms of generation, and these problems will become more significant as the turbine size increases.

From a reliability standpoint it is desirable to eliminate the gearbox, so a direct drive solution is required. Unfortunately the direct drive turbines currently in operation suffer from the problems with the complexity and weight of the generator, and the unreliability of the power electronic interface, which must be addressed.

#### 1.3 Lightweight Direct Drive Generators

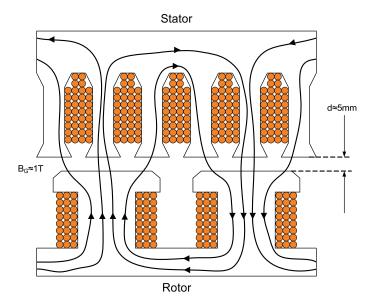

All iron-cored electrical machines, as in Figure 1.5, experience a force of attraction between rotor and stator, which may be 100 times greater than the torque producing shear force. In a radial flux machine this force is balanced between the different sides of the rotor. However if the rotor or stator become distorted this will decrease the

air gap size in parts of the machine, increasing the stress in that area, which will further distort the machine. For this reason radial electrical machines need to have a stiff structure to maintain a constant air gap and prevent this deformation. A stiff structure is simple to achieve in a high speed machine, but much more difficult in a low speed machine with a large rotor diameter but relatively small air gap size. The generators are also expensive to manufacture due to the large number of rotor poles, which leads to a large number of stator slots compared with a high speed machine, making winding the generator a long process.

Figure 1.5: Cross section of a slotted generator, with electrical excitation

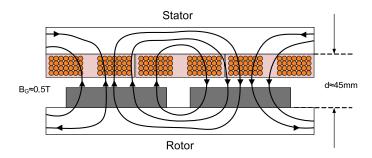

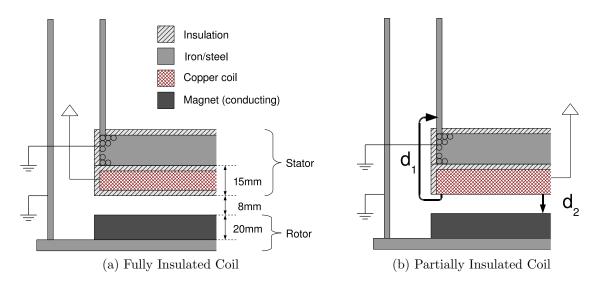

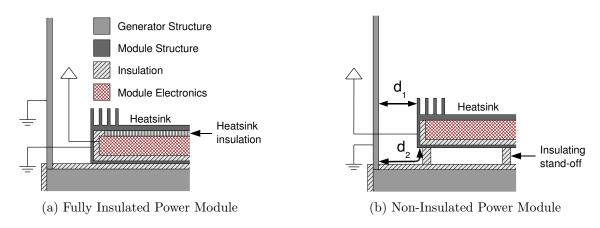

An alternative generator construction is to situate the stator coils in the air gap of the generator, with an iron core behind them, and permanent magnet excitation on the rotor, which is shown in Figure 1.6. This would reduce the airgap flux density from around 1T to 0.5T, which would significantly reduce the attraction forces between rotor and stator. The lower flux density means that a greater number of turns would be required in the stator coils in order to achieve the same EMF. This is possible because the elimination of the stator slots allows more space for copper, and enhanced cooling potential, which allows a higher current density to be used at the expense of lower efficiency. The reduced airgap closing forces allow a lighter structure to be used to support the generator.

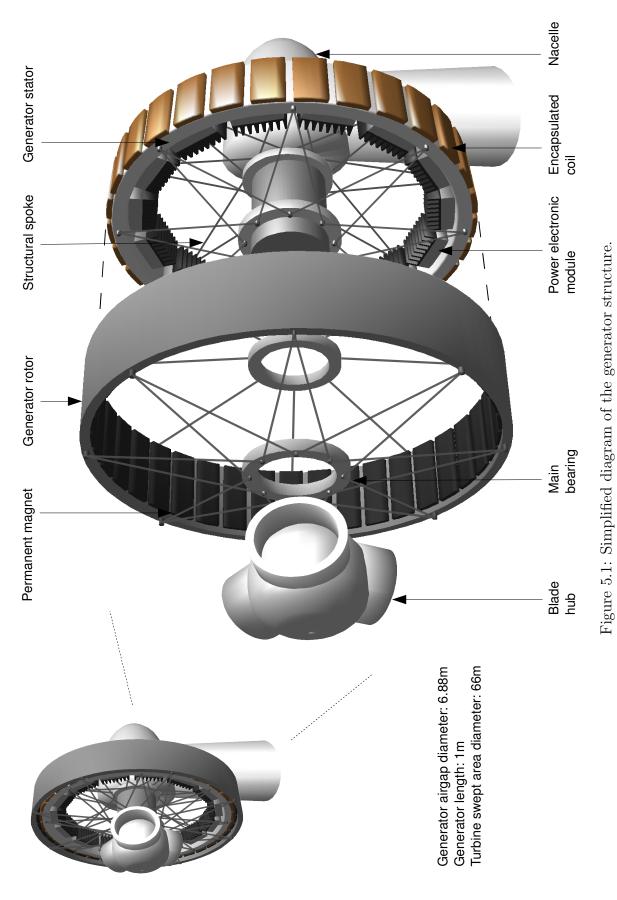

A generator has been designed in association with Durham University which uses a completely ironless stator, and a prototype has been constructed [11]. The

Figure 1.6: Cross section of a slotless generator, with permanent magnet excitation

ironless stator reduces the flux density to around 0.25T, and the highly uneven flux distribution around the permanent magnets mean that a larger pole pitch must be used than in an iron cored generator in order to avoid excessive leakage flux. This results in a very large generator diameter – up to a third of the turbine diameter. To support the generator a spoked structure has been proposed. The generator with an iron core but airgap windings mentioned in the previous paragraph has been proposed as an alternative solution as it offers a greatly reduced diameter.

It is proposed modular system of coils be used, with racetrack coils being random wound and encapsulated as single units before being attached to the stator. This approach should allow greater reliability, and reduced cost of the mass produced coils, compared with a slotted machine.

#### 1.4 Power Electronic Interface

One of the distinguishing features of the lightweight concept under consideration is that the separate coils and modular design mean that it is fairly easy to vary the number of electrical phases of the generator. Most electrical machines use three phases, as this is what the electricity grid uses. Although connecting a machine through a power electronic inverter allows a different number of phases to be used, the convention of using three phases is kept in order to allow machines and inverters from different manufacturers to interoperate. In spite of this, multi-phase machine designs offer several advantages over three-phase [12]:

• Multi-phase machines have a higher fault tolerance than 3 phase. If one phase of a three phase machine is lost then the machine will behave as a single phase machine, and will be unable to self start as well as being significantly derated.

If one phase of a 15 phase machine is lost then the machine will still start and derating will be minimal.

- Multi-phase machines produce a magnetic field with lower space-harmonic content, leading to higher efficiencies.

- The reduced space-harmonics in the magnetic field leads to lower-time harmonic components in the excitation waveform. These components would produce a pulsating torque and excess noise.

The issue of fault tolerance is of greatest interest in wind applications, but this can still be achieved using a three phase generator with multiple coils connected separately rather than in series. One method for connecting the coils devised by the designers of the proposed generator is to connect each coil to a common DC bus, via a single phase rectifier. This is possible because of the minimal mutual coupling between coils, and offers a high level of fault tolerance. However, the use of passive rectifiers and the low reactance of the coils leads to a short conduction period, which would lead to a pulsating torque. To minimise this pulsating torque several phases are used, the generator design used in this project features 8 phases.

At present, low-speed direct-drive and multi-phase machines are being used in the area of marine propulsion. Although there are many differences, some of the technology may be appropriate to large scale wind.

#### 1.4.1 Marine Drive and Other Multiphase Applications

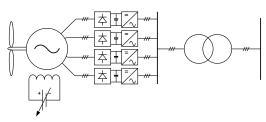

Electric ship propulsion is attracting considerable interest, due to the increases in efficiency and the ability to distribute the engines around the ship without the need for long drive shafts. A distribution voltage of 4.16kV and 60Hz is usually used, with 13.8kV used in larger ships. Direct drive machines are used, with multi-phase machines in particular attracting considerable interest due to their fault tolerance and smooth torque characteristics. In the past synchronous machines have been used, driven by thyristor-based converters, with several 3-phase converters being used to supply the phases in groups of three. The converters are often supplied by a phase shifting transformer to step the voltage down and reduce the rectifier input current harmonics. This arrangement is shown in Figure 1.7a. A more recent connection method involves using voltage source inverters, shown in Figure 1.7b,

where a phase shifting transformer is not needed if an actively controlled PWM rectifier is used. At present converters are available which can operate up to 4.16kV, so a step-down transformer is not always required.

(a) Multi-phase synchronous machine with current-source inverter

(b) Multi-phase induction machine with voltage-source inverters

Figure 1.7: Marine Drive Systems

Most of these machines are similar to conventional machines, unlike the proposed concept, so most of the power conversion technology would not be appropriate. For instance, the Alstom Advanced Induction Motor shown in Figure 1.8, designed for ship propulsion, is a 20MW machine rotating at 180rpm, using around 20 poles. As a comparison, a 1.8MW lightweight direct drive generator design would rotate at 15rpm and have around 200 poles.

Figure 1.8: Alstom/Converteam advanced induction motor [13]

The conventional machine design used in most multi-phase machines uses overlapping coils, leading to a high level of coupling between phases. This combined with the need to provide excitation for the induction machine means that coils cannot be considered separately, and an often complex centralised switching scheme must be used [12]. The centralised switching and higher airgap tolerance of the more compact machine means that distributed power electronics is not necessary, and the converters are usually housed in several cubicles allowing easy access for repairs. However the multiple converters provide for a high level of fault tolerance, as described in [12], and this would be beneficial for large scale wind turbines.

Another application of multiphase machines is in aircraft applications, where a high level of fault tolerance is required. A design of brushless DC machine for aircraft fuel pumps uses a 4 phase machine with single tooth windings, specifically designed to minimise coupling between coils. The coils are each driven by an individual single phase inverter and DC link, although control is central. In this case the inverter is separate from the machine, which at 15kW and 60,000rpm and oil cooled is very compact, while the inverter is air cooled and fairly large [14].

The main similarity between multi-phase machines and the lightweight direct drive generator technology is that in both cases the machine and power conversion must be designed together as a system, rather than the conventional practice of buying generic machines and drives from different suppliers. Most multi-phase machines rely for fault tolerance on the larger number of phases and sophisticated control while the proposed concept relies on having a large number of identical coils with an arbitrary number of phases.

#### 1.4.2 Power Conversion Issues with Lightweight Generators

The modular nature of the proposed concept invites a modular power conversion scheme, in order to reduce cost and improve fault tolerance, and the nature of the machine provides opportunities and challenges in the design of such a scheme. These issues, to be found in any generator using separate coils along with a lightweight ironless or slotless structure, are detailed below:

- The use of separate modular coils results in low mutual inductance between adjacent coils, meaning that a modular power conversion scheme can be controlled locally, without having to worry about coils connected to other modules.

This is different from the multi-phase induction machine arrangement in which central control is required and therefore fault tolerance is lower.

- The lightweight generator structure results in a lower air gap stability, meaning that the air gap size and hence the coil EMF could vary around the machine

and with time as the machine rotates. It is desirable to keep the power drawn from each coil constant in order to keep the torque distribution around the generator even, and to prevent torque pulsations.

The slotless design allows the coils to be more easily insulated to a higher voltage than possible in a slotted generator. This could allow a system to be used in which the grid interface transformer can be eliminated, improving efficiency and reducing cost.

#### 1.4.3 Proposed Power Electronic Interface

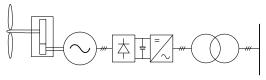

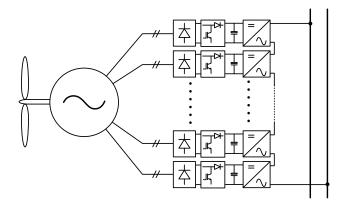

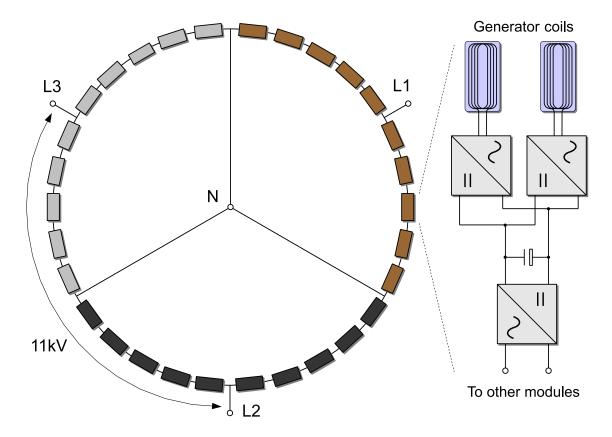

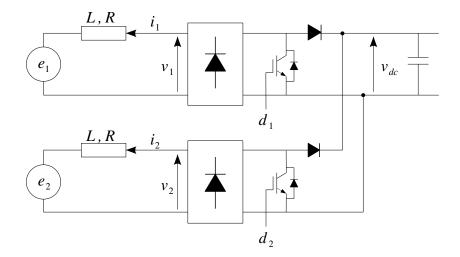

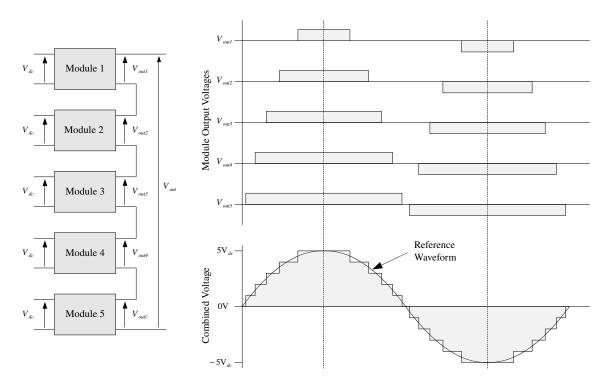

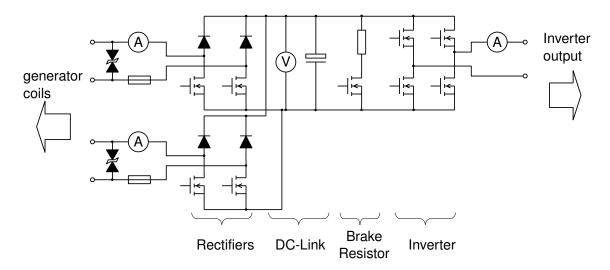

It has been proposed that a cascaded multilevel voltage source inverter (CMVSI) be used to connect the generator to the grid. This type of inverter consists of several H-bridge inverters whose outputs are cascaded to form one phase of the inverter, with the outputs switched so as to synthesize a sinusoidal voltage output. Such a system allows for a high output voltage while using lower voltage switching devices, and a modular approach can be used with each level being a separate identical module to reduce costs.

One of the main problems limiting the use of multilevel converters has been the difficulty of controlling the DC-link voltages of the different levels. In the proposed design the DC links of the modules will be fed by individual coils in the generator, and if a boost rectifier is used the DC-link voltages will be individually controllable. Such a system, with boost rectifiers, is shown in Figure 1.9.

Figure 1.9: Direct-drive generator with one phase of the cascaded multilevel inverterbased grid interface

#### 1.5 Scope of this Project

A switching strategy for the proposed inverter has been developed within Durham University, which aims to equalise the power sharing between converter modules as much as possible. A rectifier topology and control system have not been determined, and must be designed, with the following features being desirable:

- Shaping the coil current so that it is sinusoidal and in phase with the coil EMF, in order to maximise the power extraction from the coils and minimise torque ripple.

- Allowing a wide variation in turbine speed, allowing maximum power capture at a wide range of wind speeds.

- Regulating the module DC link voltage to maintain a constant voltage with changing inverter output, and a difference in power sharing between modules.

- Preventing ripple in the DC link voltage, at twice the grid frequency due to the inverter switching, from causing an associated ripple in the rectifier current demand.

- Mitigating any undesirable effects of the airgap eccentricity on the generator EMF.

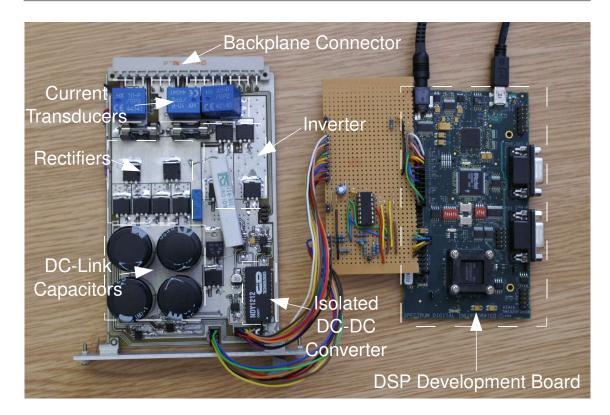

The design of the rectifier will have a significant impact on the system efficiency and cost, as well as the power output and control strategy. A 1.8MW lightweight generator has been designed, and components will be sized for this design. The choice of components will give allow a breakdown of the electrical losses in the system, as well as the costs of the converter components. A test system will be designed and built around a smaller direct drive generator in order to validate the proposed power electronic design.

While the inverter switching strategy has been developed, it has not been implemented in hardware, method of implementation must be developed. As the power electronic modules could feature a significant processing power due to the rectifier, much of the inverter switching could be implemented on the modules themselves, rather than determining each switching instance in a central controller. This would

have the advantage of reducing the number of control cables that would need to connect to the modules.

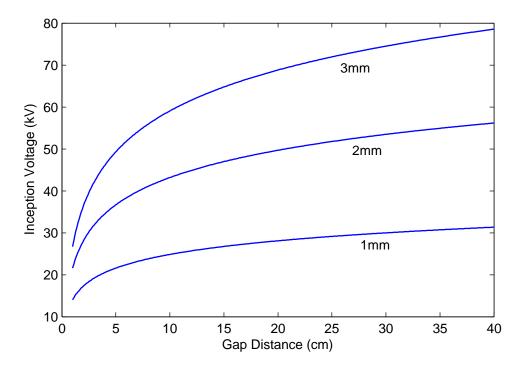

As the proposed system will have a high voltage output of 11kV, the issues with using such a high voltage will be investigated. In particular the insulation requirements in the generator and power electronics will be determined, as well as the arrangements for lightning strike protection.

The main goal of this project is to show that the proposed system is workable, which will be demonstrated on a laboratory prototype. A significant advantage of the proposed inverter system is that of fault tolerance, where the inverter is able to continue operating after faults in some of the modules, and this must be demonstrated. The ability of the inverter to ride through grid faults should also be investigated.

The choice of a cascaded multilevel inverter, with a high voltage output, for grid interfacing, is highly dependent on the design of the proposed generator. While the generator design makes the proposed power electronic system possible, the design and control of the power electronic system could also mitigate many of the disadvantages of the generator design, increasing the viability of the complete system.

## Chapter 2

# The Savonius Project

Initial work was concerned with developing a power electronic interface for a small scale wind turbine, with a newly developed direct drive axial flux generator. The interface is designed to connect the generator to a battery bank, to charge the batteries, and the aim was to increase the power extraction compared with connecting the generator through a passive rectifier alone. This is achieved by increasing the speed range of the turbine, so that the turbine's maximum power operating point can be tracked over a wider range of wind speeds.

While this system different from the large scale applications mentioned in the introduction, the principle of increasing the speed range of the turbine to improve the power capture is equally valid for large scale systems, as is the method for estimating the improvement in the annual power capture of the turbine.

The wind turbine used is a savonius-type vertical-axis turbine, which will extract 166W in a 9m/s wind, and rotating at the optimum speed of 216RPM. It is a drag-based turbine, so it will generate torque from rest and can self-start. The turbine is shown in Figure 2.1, and further details are given in Table 2.1. The generator is an air-cored axial-flux generator, with coils wound on nylon bobbins and mounted in a plastic frame in the air gap, and is designed to be cheap to produce and rugged [15]. The individual bobbin-wound coils mean that characteristics will be similar to the lightweight direct-drive generator, which was mentioned in the introduction. In particular the mutual inductance between coils will be low. The generator has 12 coils in 3 phases, and for this application the 4 coils in each phase will be connected in parallel. A summary of the generator characteristics is given in Table 2.2.

Typically small scale wind turbines use permanent magnet synchronous genera-

Figure 2.1: The savonius wind turbine

| Turbine diameter          | $0.78 { m m}$        |

|---------------------------|----------------------|

| Turbine height            | 2.4m                 |

| Turbine moment of inertia | $7.9 \mathrm{Nms}^2$ |

Table 2.1: Turbine characteristics

| Number of coils          | 12        |

|--------------------------|-----------|

| Number of pole pairs     | 8         |

| Coil Inductance          | 4mH       |

| Coil Resistance          | $1\Omega$ |

| Maximum current per coil | 3A        |

Table 2.2: Generator characteristics

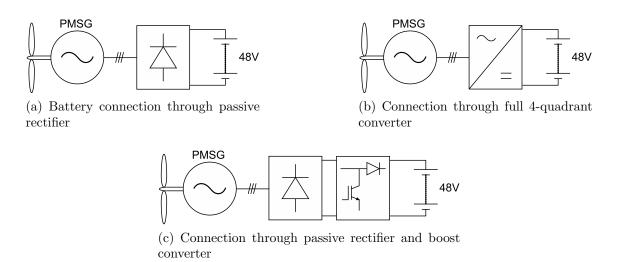

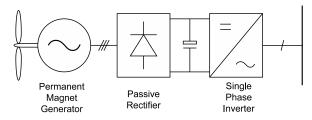

tors (PMSG), as in this case, which are connected to the batteries through a passive diode rectifier. This is shown in Figure 2.2a. A charge controller is usually also used, which will prevent the batteries being over charged by dumping power into a load. The fixed battery voltage limits the speed range of the turbine, meaning that the number of turns in the generator coils will determine the operating speed of the turbine, and hence the power capture in different average wind speeds.

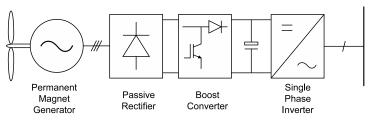

An alternative approach would be to replace the passive rectifier with a fully active four-quadrant converter, shown in Figure 2.2b. This would provide a voltage boosting capability allowing the turbine speed to vary, as well as drawing a sinusoidal current, maximising the generator utilisation and minimising torque ripple. Unfortunately the converter would use 6 or more switching devices, making it costly in terms of components and gate driving circuitry. The converter would also require the generator EMF position to be tracked, requiring a powerful controller.

A cheaper alternative is to use a boost converter in between the passive rectifier and battery, to allow the turbine to operate at different speeds, shown in Figure 2.2c. Although the passive rectifier would still cause a torque ripple in the generator, the converter would be significantly cheaper, requiring only one transistor. It is this design which shall be considered.

Figure 2.2: Small scale wind turbine battery connection

#### 2.1 Modeling of the System

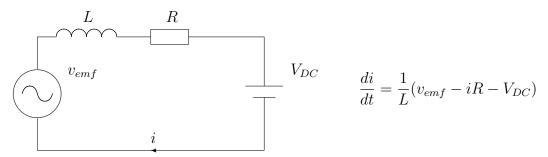

Initial modeling was carried out in order to find the most efficient operating point for different wind speeds, and to calculate the power curve – the curve of power output against wind speed. For all modeling the generator was represented as sinusoidal EMFs in series with inductance and resistance for each phase, with the EMF being proportional to the rotation speed. The DC side of the rectifier was modeled as a Thevenin-type voltage source to represent the battery and boost converter. The mechanical power extracted by the turbine is given by the following equation:

$$P_{\text{mech}} = 0.5 C_p \rho v_w^3 A \tag{2.1}$$

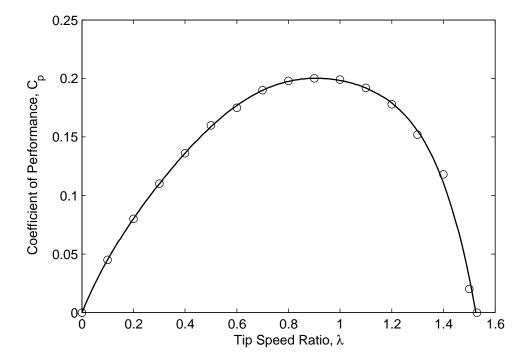

Where  $P_{\text{mech}}$  is the mechanical power extracted,  $C_p$  the turbine coefficient of performance, which determines how much of the energy in the wind the turbine can extract,  $v_w$  the wind speed, A the turbine swept area and  $\rho$  the air density.  $C_p$  is a function of,  $\lambda$ , the ratio of the speed of the blade tips to the wind speed, and is shown for this turbine in Figure 2.3.

Figure 2.3: Turbine  $C_p$ - $\lambda$  curve

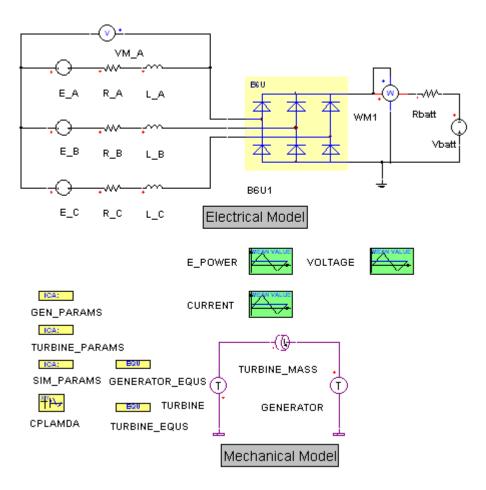

A simulation was created using Simplorer, shown in Figure 2.4. For a given wind speed and turbine speed, the mechanical power can be calculated using Equation 2.1,

and the torque calculated by dividing by the speed. The electrical torque can be calculated from the electrical circuit simulation, from the coil real power. When the electrical torque is subtracted from the mechanical, the resultant torque will cause the turbine to change speed, and the speed will move toward a steady state value where the mechanical and electrical torques balance, at a rate determined by the turbine moment of inertia.

Figure 2.4: Simplorer model for the system

The simulation was run for a simulation time of 10s, to allow the turbine speed to settle at the steady state value, and at the end of the time the power output and other variables were recorded. This was carried out at DC voltages between 10V and 100V and wind speeds between 1 and 20m/s, with a step of 1V and 1m/s respectively. 1820 simulations were required, which were set up and performed automatically.

The results of the simulations were processed using Matlab, to smooth out and interpolate the curves. For each wind speed, the maximum electrical power was September 9, 2009

found along with the other parameters at this power. The electrical power was also calculated for DC voltages of 24V and 48V, to simulate the effects of connecting the output of the rectifier directly to a battery.

### 2.2 Simulation Results

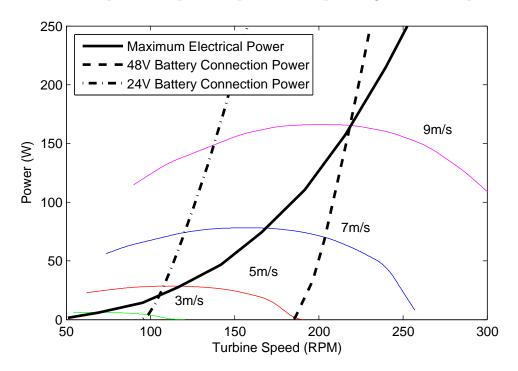

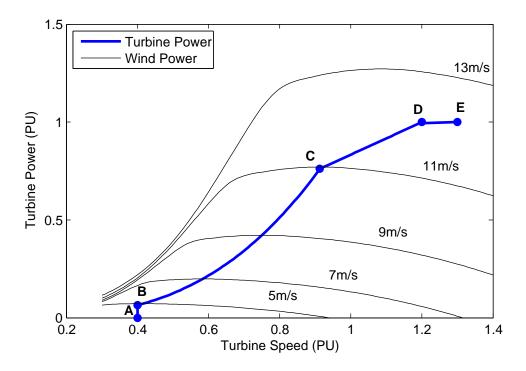

Some of the simulated power-speed curves for various wind speeds are shown in Figure 2.5, along with the operating lines for maximum power and direct battery connection. It can be seen that the direct battery connections limit the speed to a narrow range, with the speed being higher at higher powers due to the voltage drop from the generator resistance increasing. The battery terminal voltage will also increase due to the internal resistance of the batteries. The line of maximum electrical power is slightly to the right of the maximum mechanical power, as the faster generator speed reduces the current for a given power, increasing the efficiency. This offsets the drop in wind power capture from operating at a faster speed.

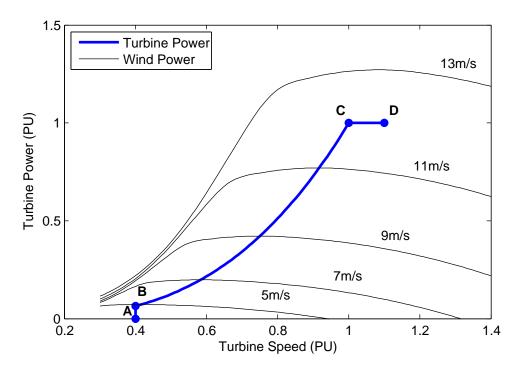

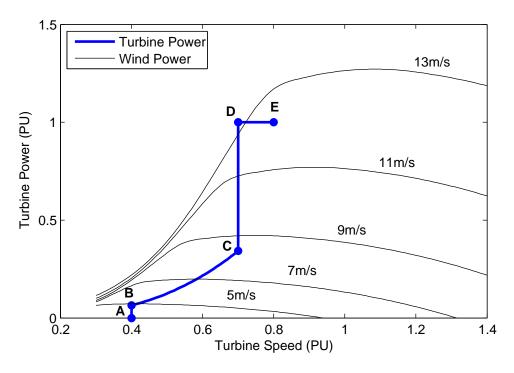

Figure 2.5: Electrical power vs. turbine speed at different wind speeds.

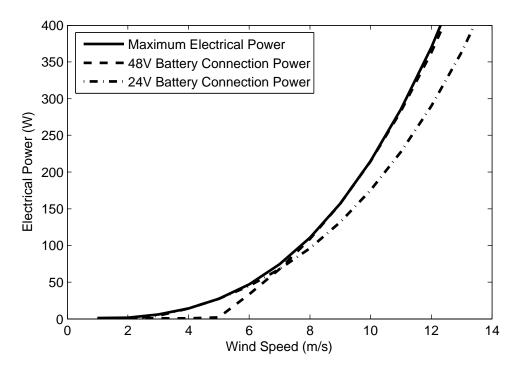

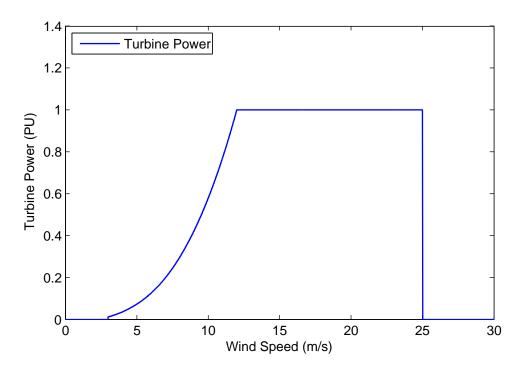

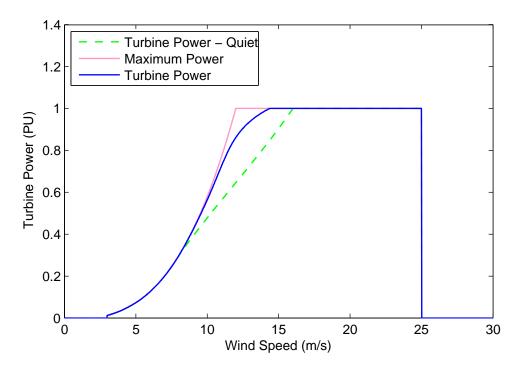

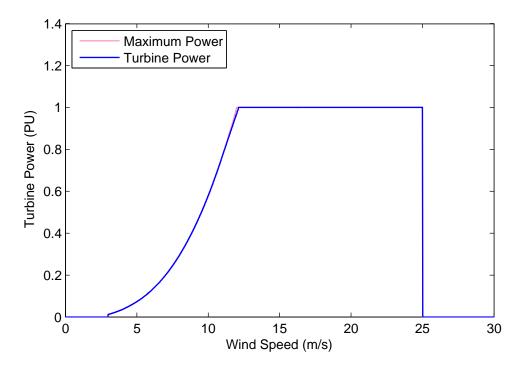

The simulated power vs. wind speed curve is shown in Figure 2.6 for maximum power and battery connections. It can be seen that the limited speed range of the direct battery connection at 48V battery voltage limits the power capture at low

wind speeds. Above around 8m/s wind speed, the power capture is very similar. At 24V battery voltage, the speed range of the turbine is limited around a lower value than at 48V, and the power capture is good at low wind speeds, but deteriorates above 7m/s wind speed.

Figure 2.6: Electrical power vs. wind speed

# 2.3 Proposed Power Tracking Solution

### 2.3.1 Converter Topology

It can be seen in Figure 2.6 that a direct battery connection at 48V, as currently used, results in a good tracking of the maximum power curve at wind speeds above 8m/s. It is only below 8m/s where energy capture efficiency is low. It is therefore proposed to use a boost-type DC-DC converter to boost the DC output of the rectifier at low wind speeds so that the generator will operate at the optimum speed. At above 8-9m/s the DC output of the rectifier will reach the battery voltage, the converter will stop switching and the current will be carried by the boost diode, which will have to be rated appropriately. This represents a cost saving over a converter rated across the entire range as the switching transistor and smoothing capacitor will have a much

smaller rating and can be significantly cheaper. A further cost saving is achieved by using the generator inductance as the inductance in the boost converter.

As the converter cuts out when the DC output of the rectifier reaches the battery voltage, the converter cut-out wind speed will depend on the EMF produced by the generator and the battery voltage. A low generator EMF and high battery voltage will result in a high converter cut-out wind speed, leading to a large speed range and good power capture, but would require a large converter. A high generator EMF and low battery voltage will result in a low converter cut-out wind speed and a small converter, which will limit the maximum generator speed, leading to reduced power capture at higher wind speeds. Because of this, it is vital to match the generator EMF and the battery voltage to achieve the optimum converter cut-out wind speed, which is a compromise between power capture and converter size and cost.

### 2.3.2 Tracking Algorithm

If the generator resistance is ignored, the generated power output of a wind turbine is related to the wind speed cubed, when the turbine is operating at the optimum speed. At the optimum speed, the tip speed ratio will be constant, so the rotation speed will be proportional to the wind speed, i.e.

$$P_{\rm gen} \propto {v_{\rm wind}}^3$$

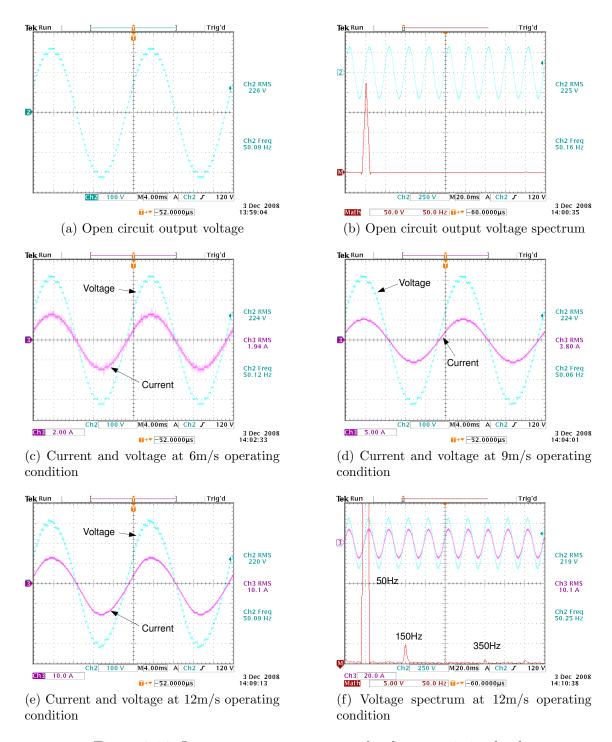

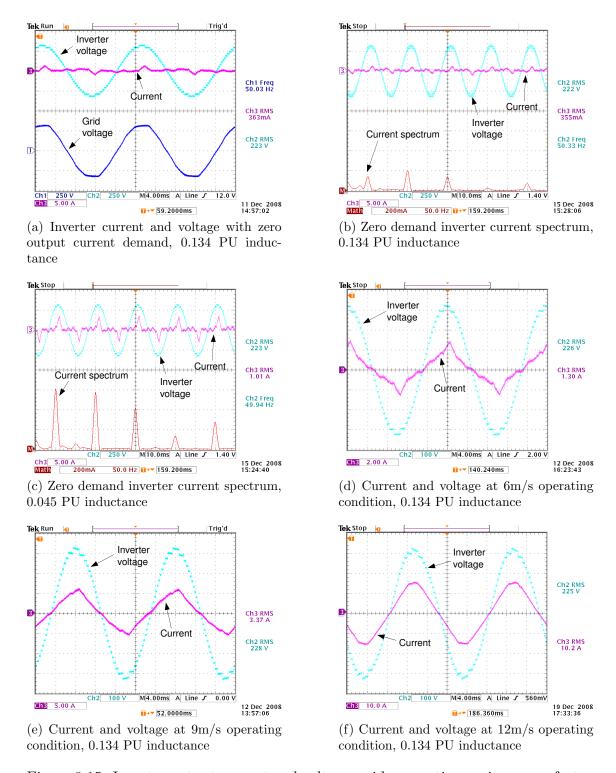

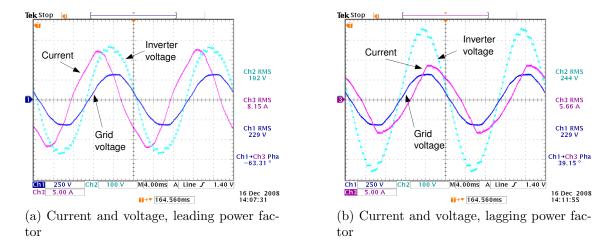

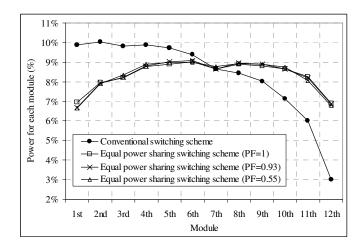

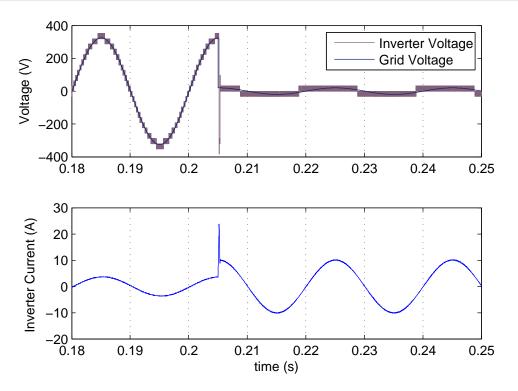

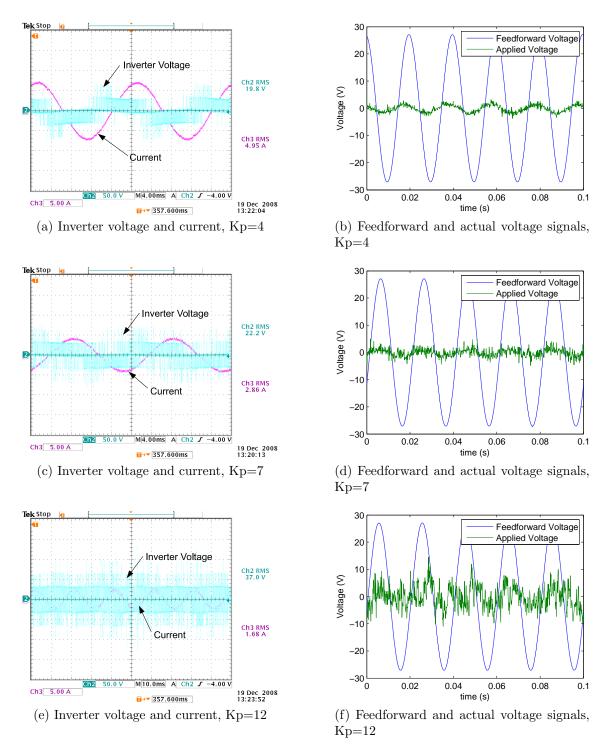

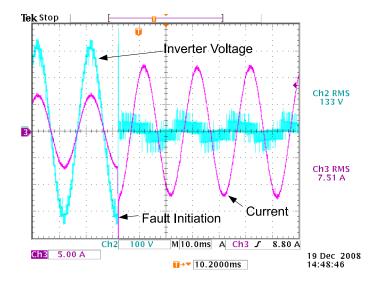

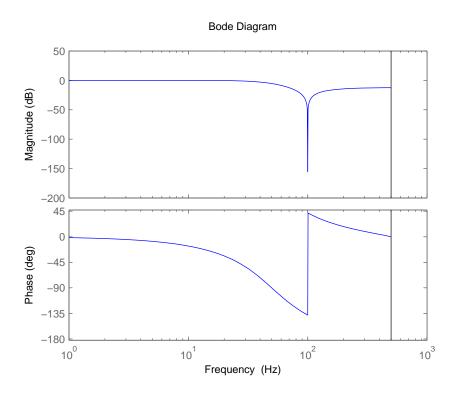

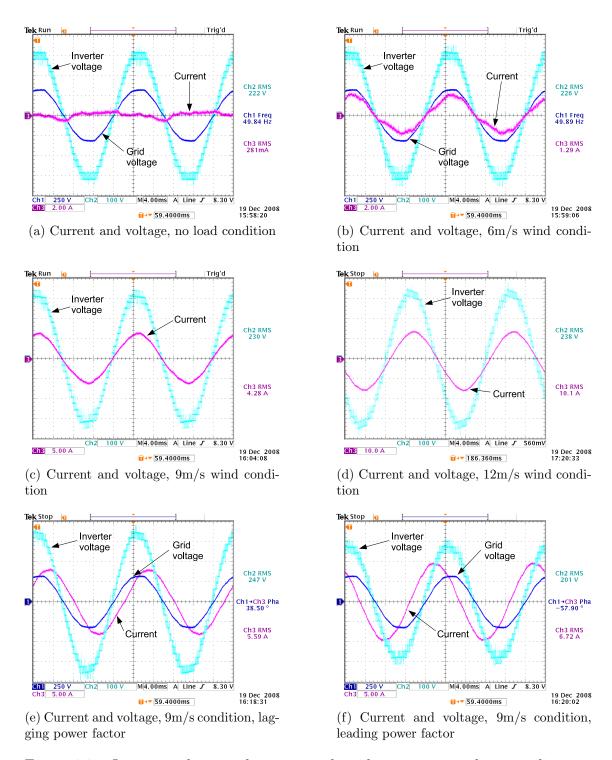

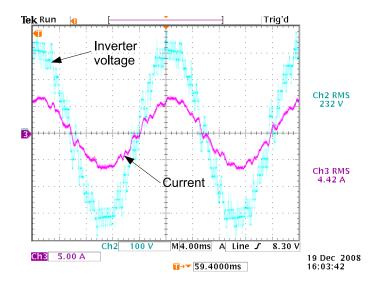

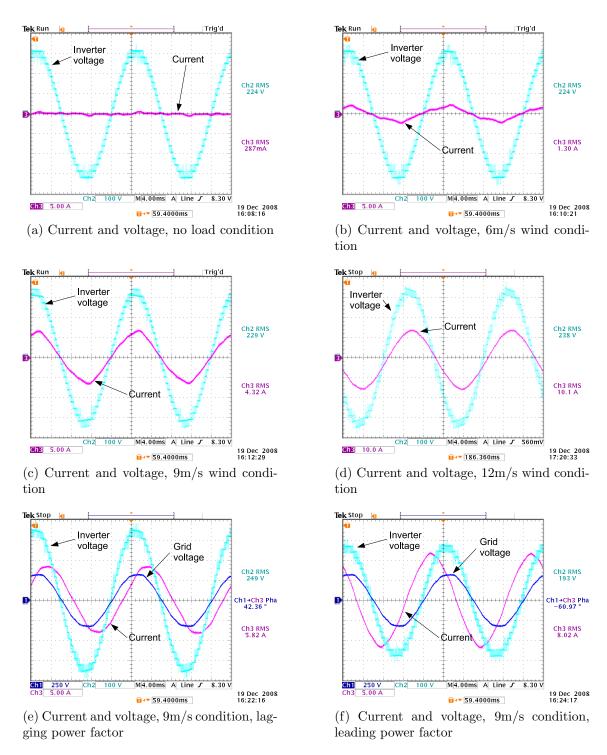

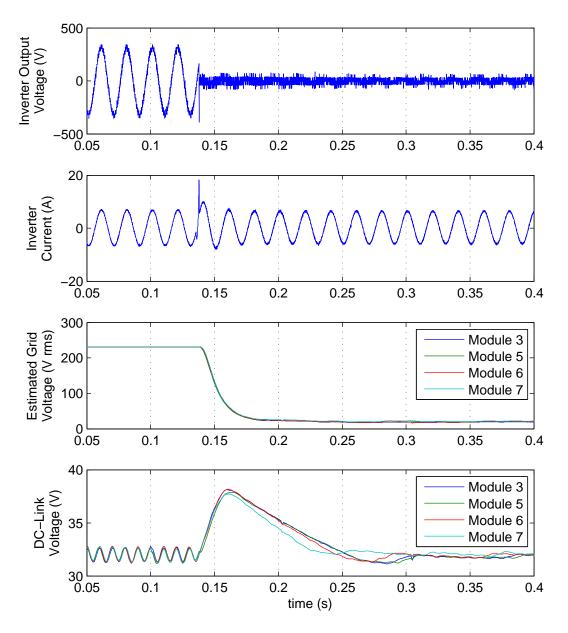

$$P_{\rm gen} \propto {\omega_{\rm gen}}^3 \eqno(2.2)$$